# **Chapter 1**

# **Real Time Interrupt Module**

#### Topic

#### Page

| 1.1  | Revision History 1–2       |

|------|----------------------------|

|      | Reference documents 1-4    |

| 1.3  | General Description        |

|      | Introduction               |

|      | Register Mapping 1–7       |

|      | Block diagram 1–10         |

|      | Module Operation 1–11      |

|      | Control Registers 1–19     |

|      | Interface                  |

| 1.10 | Design Considerations 1–73 |

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments. This revision supersedes all previous versions.

**Revision History**

1-2

# 1.1 Revision History

| Date     | Version  | Author     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/31/02 | Rev. A   | Frank Noha | Initial revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 06/21/02 | Rev. A.1 | Frank Noha | changed all references to counter block 1 and 2 to 0<br>and 1 (i.e. UC2 -> UC1,)<br>page 5: changed reference to external clock timout<br>counter to external clock supervising circuit<br>page 11: added note for TBHCOMP and TBLCOMP<br>values<br>updated detection period for NTU<br>page 14: added note for standby mode with PLL off<br>page 56: removed "TBINT flag setting when external<br>timebase counter reaches zero"<br>page 57: clarified setting of TBINT flag<br>section 1.9: updated interface signal list<br>removed VBUSP-FIRST, VBUSP-<br>BYTECNT, VBUSP-AMODE, VBUSP-<br>AERROR<br>changed overflow interrupts and capture<br>events to bus type |

| 08/23/02 | Rev. A.2 | Frank Noha | changed all references from WKEY to RTIWDKEY<br>page 10: changed incoming signal name Up Counter<br>1 to Up Counter 0.<br>page 11 end of first paragraph: changed Free Run-<br>ning Counter 1 to Free Running Counter 0.<br>added additional Note, to set<br>RTIGCTRL[0].<br>page 13: changed NOR gate in Blockdiagram to<br>reflect American symbol<br>page 52: corrected typo for writting 1 to register bits<br>18, 17, 16 to reflect disabling of interrupts<br>page 59: changed bit setting after Reset to 0xA3<br>page 62/63: changed signal names with RTI_ prefix<br>page 63: changed WD_RESET signal to<br>RTI_RESETn                                        |

| 08/30/02 | Rev. A.3 | Frank Noha | page 14: added overflow interrupt generation in<br>standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 09/27/02 | Rev. A.4 | Frank Noha | page 38, 40, 42, 44: changed wording of interrupt<br>generation to flagged and generate DMA<br>request to initiate DMA request<br>changed note to state that the compare will<br>only be active at counter enable                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 01/22/03 | Rev. A.5 | Frank Noha | added variable "platform_name"<br>page 14: added chapter 1.7.5 Suspend Mode behav-<br>iour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Date     | Version   | Author     | Description                                                                                                                                                                                                                                                                                                                                 |

|----------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/21/03 | Rev. A.6  | Frank Noha | clarified RTITBHCOMP behaviour on page 12 and page 49                                                                                                                                                                                                                                                                                       |

| 06/11/03 | Rev. A.7  | Frank Noha | updated read of reserved register bits to read as 0<br>page 11: added paragraph about NTU detection<br>page 14: updated key values to 16 bit<br>page 21: increased size of WDKEY register to 16 bit<br>page 61: updated WDKEY register for new values<br>page 64: added NTU period requirement                                              |

| 06/12/03 | Rev. A.8  | Frank Noha | page 10: clarified capture event read<br>page 11: modified paragraph about NTU detection<br>page 12: clarified behaviour if NTU pulse is not<br>detected after switching to ext. timebase<br>page 34,39: clarified capture event read<br>page 64: modified NTU period requirements                                                          |

| 07/31/03 | Rev. A.9  | Frank Noha | added Digital Watchdog<br>changed reset value on RTIWDKEY register to be<br>consistent with the DWD spec                                                                                                                                                                                                                                    |

| 08/04/03 | Rev. A.10 | Frank Noha | page 15: updated blockdiagram for suspend mode<br>behaviour and changed RTICLK to OSC-<br>CLK for DWD Counter<br>page 18: added DWD behaviour in suspend mode<br>page 23: added KEYST bit in RTIWDSTATUS<br>page 65: added KEYST bit and comment about sta-<br>tus bits<br>page 70: added OSC_CLK<br>page71: added System Interface section |

| 12/17/03 | Rev. A.11 | Frank Noha | page 15ff, page 64: changed DWDPRLD value to 12<br>bits<br>added Digital Watchdog down counter                                                                                                                                                                                                                                              |

| 06/23/04 | Rev. A.12 | Frank Noha | page 13: corrected typo's<br>page 56: corrected enabled to disabled in 1st sen-<br>tence                                                                                                                                                                                                                                                    |

| 03/28/05 | Rev. A.13 | Frank Noha | page 67: changed reset value of WDKEY register                                                                                                                                                                                                                                                                                              |

Real Time Interrupt Module

# 1.2 Reference documents

The version number of a document is related to the version used for the Real Time Interrupt Module development

| Reference<br>number | Document Name/Company | Reference | version |

|---------------------|-----------------------|-----------|---------|

|                     |                       |           |         |

# 1.3 General Description

This document describes the functionality of the Real Time Interrupt Module used on TMS470 Platform derivatives.

Real Time Interrupt Module

## 1.4 Introduction

The Real Time Interrupt Module (RTI) provides timer functionality for operating systems and for benchmarking code. The Module incorporates several counters, which define the timebases needed for scheduling in the operating system.

This module is specifically designed to fulfill the requirements for OSEK ("Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug"; "Open Systems and the Corresponding Interfaces for Automotive Electronics") as well as OSEK/Time compliant operating systems.

The timers also give the ability to benchmark certain areas of code by reading the counter contents at the beginning and the end of the desired code range and calculating the difference between the values.

#### 1.4.1 Main Features

- Two independent counter blocks for generating different timebases

- Each block consists of

- One 32 bit prescale counter

- One 32 bit free running counter

- Two capture registers for capturing the prescale and free running counter on a special event

- Free running counter 0 can be incremented by either the internal prescale counter or by an external event

- External Clock supervising circuit to switch to internal prescale counter 0, if external clock source fails to increment in a predefined window

- Four configurable compare registers for interrupt generation, working either with counter 0 or counter 1. Compare 0 to 3 can also generate DMA request signals

- Automatic update of all compare registers on compare match to generate periodic interrupts

- · Fast enabling/disabling of interrupts

- Analog Watchdog via external RC Network to prevent for runaway code

- Digital Watchdog

- RTI clock input derived from either VBUS or Oscillator output clock, selectable in the System Module

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

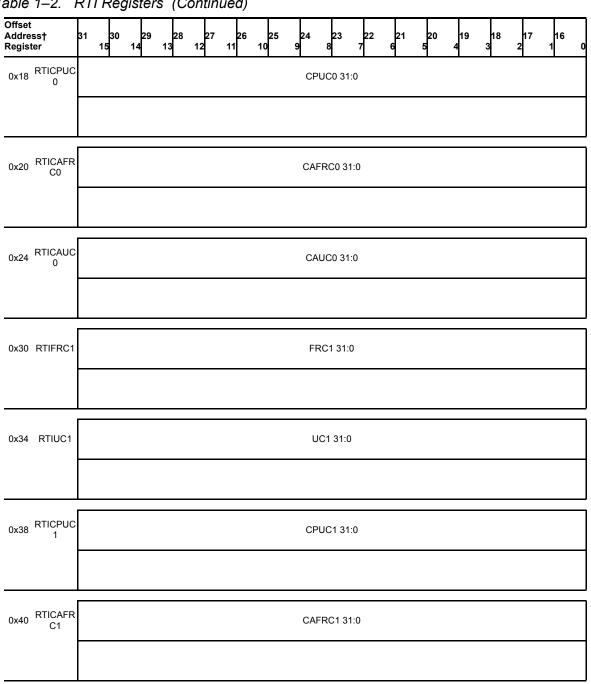

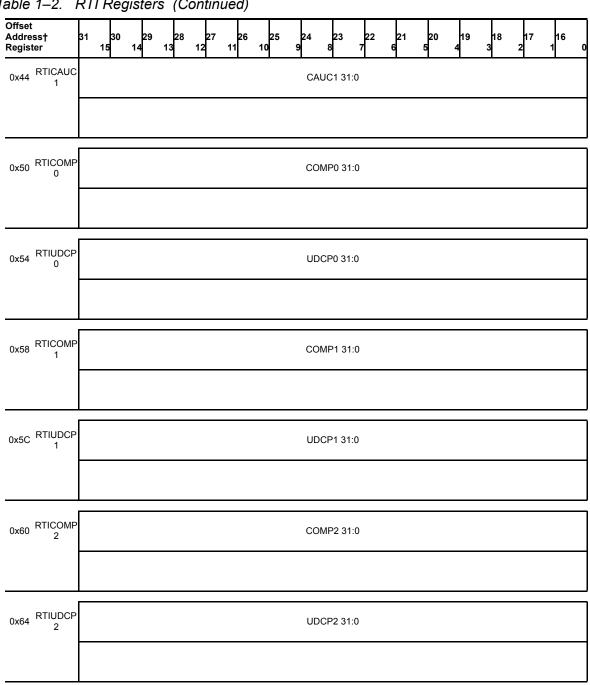

# 1.5 Register Mapping

# Table 1–1. Register Mapping

| Offset<br>Address <sup>†</sup> | Mnemonic         | Name                                | Description                                                 | Page |

|--------------------------------|------------------|-------------------------------------|-------------------------------------------------------------|------|

| 00h                            | RTIGCTRL         | Global Control<br>Register          | starts / stops the counters                                 | 1-24 |

| 04h                            | RTITBCTRL        | Timebase Control                    | selection which source triggers free run-<br>ning counter 0 | 1-26 |

| 08h                            | RTICAPC-<br>TRL  | Capture Control                     | controls the capture source for the counters                | 1-28 |

| 0Ch                            | RTICOMPC-<br>TRL | Compare Control                     | controls the source for the compare reg-<br>isters          | 1-30 |

| 10h                            | RTIFRC0          | Free Running<br>Counter 0           | current value of free running counter 0                     | 1-32 |

| 14h                            | RTIUC0           | Up Counter 0                        | current value of prescale counter 0                         | 1-33 |

| 18h                            | RTICPUC0         | Compare Up<br>Counter 0             | compare value compared with prescale counter 0              | 1-34 |

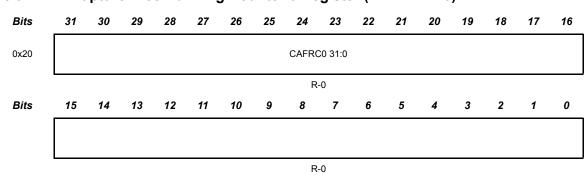

| 20h                            | RTICAFRC0        | Capture Free Run-<br>ning Counter 0 | current value of free running counter 0 on external event   | 1-35 |

| 24h                            | RTICAUC0         | Capture Up<br>Counter 0             | current value of prescale counter 0 on external event       | 1-36 |

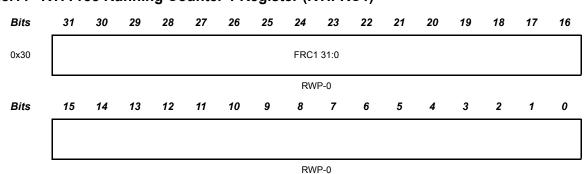

| 30h                            | RTIFRC1          | Free Running<br>Counter 1           | current value of free running counter 1                     | 1-37 |

| 34h                            | RTIUC1           | Up Counter 1                        | current value of prescale counter 1                         | 1-38 |

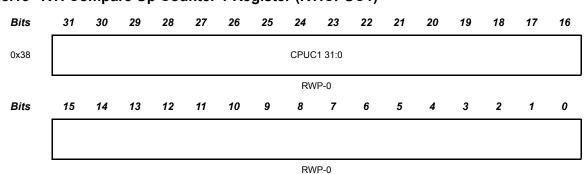

| 38h                            | RTICPUC1         | Compare Up<br>Counter 1             | compare value compared with prescale counter 1              | 1-39 |

| 40h                            | RTICAFRC1        | Capture Free Run-<br>ning Counter 1 | current value of free running counter 1 on external event   | 1-40 |

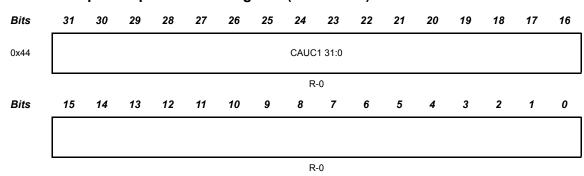

| 44h                            | RTICAUC1         | Capture Up<br>Counter 1             | current value of prescale counter 1 on external event       | 1-41 |

| 50h                            | RTICOMP0         | Compare 0                           | compare value to be compared with the counters              | 1-42 |

Real Time Interrupt Module 1-7

Table 1–1. Register Mapping

| Offset<br>Address <sup>†</sup> | Mnemonic         | Name                        | Description                                                                                             | Page |

|--------------------------------|------------------|-----------------------------|---------------------------------------------------------------------------------------------------------|------|

| 54h                            | RTIUDCP0         | Update Compare 0            | value to be added to the compare regis-<br>ter 0 value on compare match                                 | 1-43 |

| 58h                            | RTICOMP1         | Compare 1                   | compare value to be compared with the counters                                                          | 1-44 |

| 5Ch                            | RTIUDCP1         | Update Compare 1            | value to be added to the compare regis-<br>ter 1 value on compare match                                 | 1-45 |

| 60h                            | RTICOMP2         | Compare 2                   | compare value to be compared with the counters                                                          | 1-46 |

| 64h                            | RTIUDCP2         | Update Compare 2            | value to be added to the compare regis-<br>ter 2 value on compare match                                 | 1-47 |

| 68h                            | RTICOMP3         | Compare 3                   | compare value to be compared with the counters                                                          | 1-48 |

| 6Ch                            | RTIUDCP3         | Update Compare 3            | value to be added to the compare regis-<br>ter 3 value on compare match                                 | 1-49 |

| 70h                            | RTIT-<br>BLCOMP  | Timebase Low<br>Compare     | compare value to activate edge detec-<br>tion circuit                                                   | 1-50 |

| 74h                            | RTITBH-<br>COMP  | Timebase High<br>Compare    | compare value to deactivate edge detec-<br>tion circuit                                                 | 1-51 |

| 80h                            | RTISETINT        | Set Interrupt<br>Enable     | sets interrupt enable bits int RTIINTC-<br>TRL without having to do a read-modify-<br>write operation   | 1-52 |

| 84h                            | RTICLEAR-<br>INT | Clear Interrupt<br>Enable   | clears interrupt enable bits int RTIINTC-<br>TRL without having to do a read-modify-<br>write operation | 1-56 |

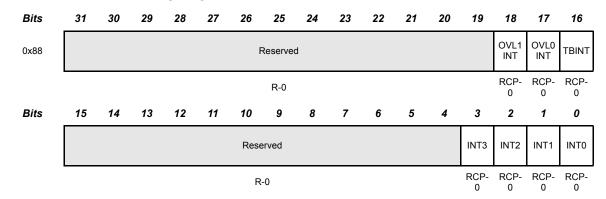

| 88h                            | RTIINTFLAG       | Interrupt Flags             | interrupt pending bits                                                                                  | 1-60 |

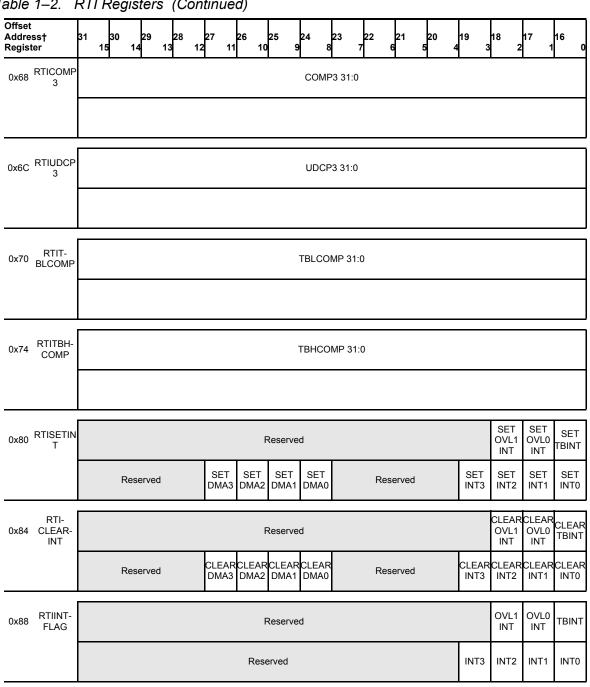

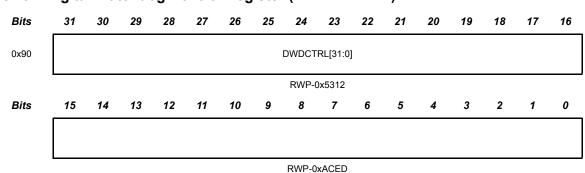

| 90h                            | RTIDWDC-<br>TRL  | Digital Watchdog<br>Control | enables the Digital Watchdog                                                                            | 1-63 |

| 94h                            | RTIDWD-<br>PRLD  | Digital Watchdog<br>Preload | sets the experation time of the Digital Watchdog                                                        | 1-64 |

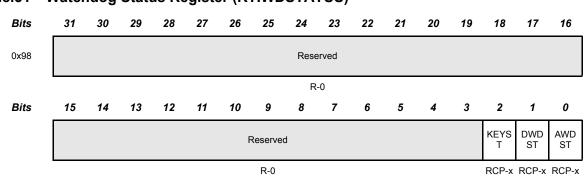

| 98h                            | RTIWDSTA-<br>TUS | Watchdog Status             | reflects the status of Analog and Digital Watchdog                                                      | 1-65 |

1-8

Table 1–1. Register Mapping

| Offset<br>Address <sup>†</sup> | Mnemonic        | Name                             | Description                                                 | Page |

|--------------------------------|-----------------|----------------------------------|-------------------------------------------------------------|------|

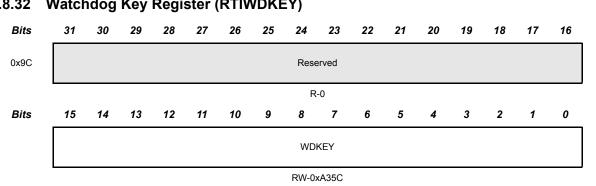

| 9Ch                            | RTIWDKEY        | Watchdog Key                     | correct written key values discharge the external capacitor | 1-67 |

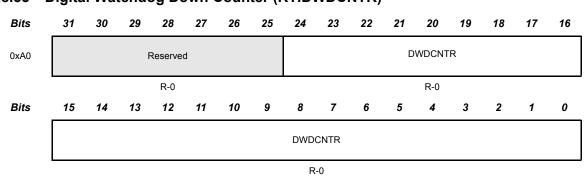

| A0h                            | RTIDWD-<br>CNTR | Digital Watchdog<br>Down Counter | current value of DWD down counter                           | 1-69 |

Real Time Interrupt Module

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information 1-9

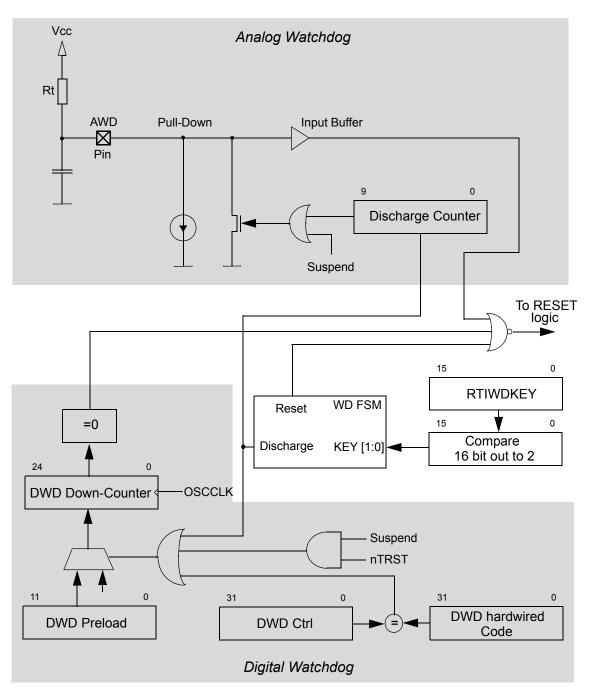

# 1.6 Block diagram

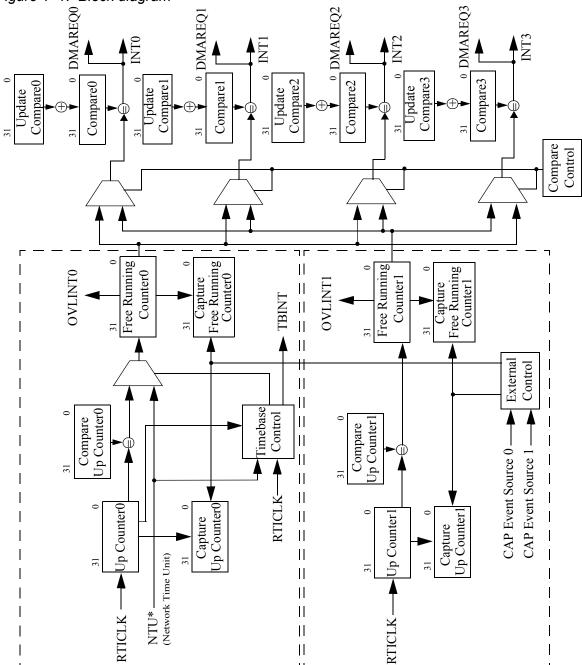

Figure 1–1. Block diagram

1-10

## 1.7 Module Operation

#### 1.7.1 Counter Operation

The two counter blocks provide the same base functionality, whereas counter block 0 has some additional features.

Each block consists of two 32 bit up counters (Up Counter and Free Running Counter). The Up Counter (UCx) is driven by the RTICLK and counts up until the compare value in the Compare Up Counter register (CPUCx) is reached. When the compare matches, the second counter (FRCx), which is a free running counter is incremented. At the same time UCx is reset to zero. If FRCx overflows a interrupt is generated to the vectored interrupt manager.

To ensure the consistency of the counters, when both counter value have to be determined, the Free Running Counter has to be read first. This will ensure that at the CPU read cycle, the Up Counter value is stored in the counter register. The second read is done on the Up Counter register, which holds then the value of the counter cycle of the previous read on the Free Running Counter register.

Both blocks provide also a capture feature on external events. Two capture sources can trigger the capture event. Which event triggers block 0 or block 1 is configurable. The sources are coming from the interrupt manager, in order to be able to generate a capture event when one of the peripheral modules has generated an interrupt. The peripheral, which can generate an event is configured in the interrupt manager. When the event is detected, UCx and FRCx are stored in Capture Up Counter (CAUCx) and Capture Free Running Counter (CAFRCx) registers. The read order of the captured values has to be like the order of the actual counters. So the CAFRCx has to be read first and the CAUCx registers has to be read after the CAFRCx value was determined. While the CAFRCx is read the CAUCx value is loaded into a shadow register to ensure data consistency, when during the two reads of the captured data another capture event happens. If the application fails to read twill be overwritten.

In order to generate interrupt requests to the vectored interrupt manager, there are four compare registers (CPx). Each of the compare registers can be configured to work either on FRC0 or FRC1. When the counter value matches the compare value, an interrupt is generated. All compares provide an additional feature, with an automatic update of the compare value with the value stored in Update Compare (UDCPx) registers when the compare matches. This gives the ability to generate periodic interrupts/DMA requests, without having to update the compare value by software.

#### 1.7.2 Timebase Control

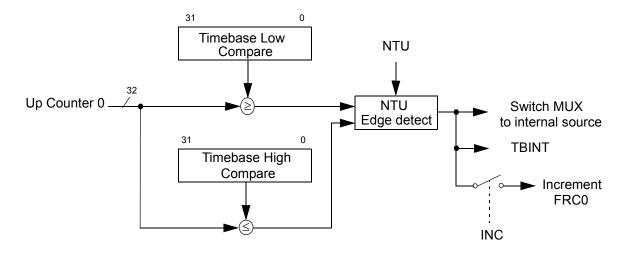

Figure 1–2. Timebase Control

To simplify the operating system design and reduce the need of CPU resources when time triggered functionality is needed, counter block 0 has additional capabilities. The source, which can trigger FRC0 can be either UC0 or an external clock source NTU (i.e. TTCAN, Flexray,...). This can be chosen by software. However to fulfill safety requirements, it is necessary to provide a fallback solution, if the external clock source fails (i.e. due to bus failure). To achieve this, there is a edge detection circuit implemented in the 'TB Control' block.

The edge detection of the NTU signal is done with VCLK and the Free Running Counter timebase is synchronized to the RTICLK. To ensure a proper detection of NTU, the NTU period has to be at least twice as long as the RTICLK period and the positive NTU pulsewidth has to be at least two times the VCLK period.

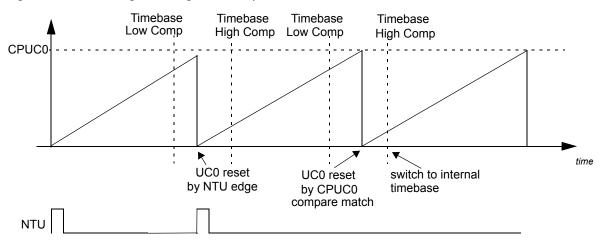

The edge detection circuit will detect clock edges on the NTU signal only when UC0 is bigger or equal than the value stored in Register Timebase Low Compare and lower or equal than the value stored in Register Timebase High Compare. This effectively opens a window in which an edge of the NTU signal is expected. Outside this window, no edges will be detected. If no edge will occure while the edge detection circuit is active, the multiplexer is switched

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

to internal timebase, optionally a timebase interrupt is generated and if the INC bit is set, FRC0 will automatically incremented by one in order to compensate the missed clock cycle of NTU. If an edge occurs, UC0 will be reset in order to synchronize the two timebases. However to synchronize the periods of the two signals, this has to be done by software by adapting CPUC0 to the period of the NTU signal.

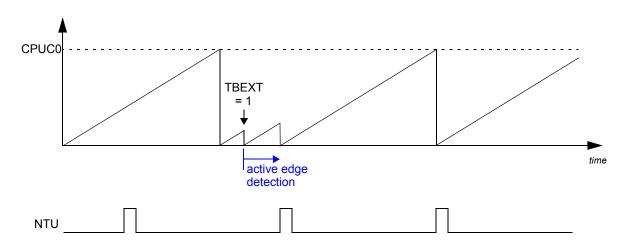

If the application decides to switch from internal source to external source a synchronization between the two signals has to be done. This will be done when the TBEXT bit is set. By setting this bit, UC0 will be reset and the edge detection circuit will be active for one (CPUC0 period + TBHCOMP) or until an edge is detected. If there is no pulse during this period the external clock source will be reset to internal clock source. If an edge is detected, the windowed edge detection behaviour will take place. Setting the TBEXT bit will not increment Free Running Counter 0.

If external timebase is used, then software has to ensure that Timebase Low Compare and Timebase High Compare are programmed to a valid state before switching TBEXT to external, in order to alow proper operation of the Timebase Control Circuit. Following condition has to be met: RTITBLCOMP < RTICPUC0 and RTITBHCOMP < RTICPUC0. RTITBHCOMP has to be lower than RTICPUC0, since RTIUC0 will be reset if RTICPUC0 is reached. RTITBHCOMP will represent the number of RTICLK cycles from RTICPUC0 until the circuit switches to internal timebase if no NTU edge is detected.

If external timebase is used, RTIGCTRL[0] has to be set to 1 (enable UC0) in order to ensure that the Timebase Control circuit does not wait indefinitely for an incoming signal.

Figure 1-3 shows a timing example for the the synchronization phase when the TBEXT bit is set.

Figure 1–3. Synchronization example

Figure 1–4. Missing NTU signal example

1-14

# 1.7.3 Analog/Digital WatchdogAnalog and Digital Watchdog

Real Time Interrupt Module 1-15

The analog and digital watchdogs generate resets to prevent for runaway code. The can be used independently of one or the other.

#### Analog Watchdog

The periodic of the analog watchdog is determined by an external RC circuit. Whenever the threshold voltage is passed, a reset is generated. The watchdog may be cleared by writing a 0xE51A and then 0xA35C to the RTIWDKEY register. When the correct values are written, the analog watchdog drains the external capacitor and resets the external RC delay. If an incorrect value is written to the RTIWDKEY register, a watchdog reset occurs immediately.

If the pin is left unconnected, the analog watchdog is disabled by the internal pulldown

While the device is in debug mode (Suspend), the external capacitor is always discharged.

The counter which controls the discharge time of the external capacitor should be 10 bit wide. This ensures that the capacitor is discharged correctly.

The values used for the external components have to match the application requirements.

#### **Digital Watchdog**

Some applications might want to use a digital watchdog instead of a analog watchdog. The digital watchdog generates also resets after a programmable periode, if no correct key sequence was written to the RTIWDKEY register.

The digital watchdog is disabled per default. If it should be used, it has to be enabled by writing to the RTIDWDCTRL register a 32-bit value which is the inverted value of the hardwired code in the module. Once the DWD is enabled it cannot be disabled.

If the correct key sequence is written to the RTIWDKEY register (0xE51A followed by 0xA35C), the 25-bit DWD Down Counter is reloaded with the 12-bit preload value stored in RTIDWDPRLD. If the incorrect values are written, a watchdog reset will occur immediately. A reset will also be generated, when the DWD Down Counter is decremented to 0.

While the device is in debug mode (Suspend), the DWD Down Counter keeps the value it had when entering debug mode.

The DWD Down Counter will be decremented with OSCCLK frequency.

The experation time of the DWD Down Counter can be determined with following equation:

$t_{exp} = (RTIDWDPRLD+1) \times 2^{13} / RTICLK$ (EQ 1)

where: RTIDWDPRLD = 0...8191

#### 1.7.4 Low Power Mode Operation

The TMS470 Platform can be placed into different Low Power modes (see System Module Specification 'Low Power Modes').

The operation of the RTI Module is guaranteed in Run, Idle and Standby mode. In Halt mode all clocks will be switched off and the RTI Module will not work in this mode either.

In Run and Idle modes all parts of the RTI will be active, since it has to be able to wake up the device with Compare and Timebase interrupts. Capturing events generated by the Vectored Interrupt Module is also possible since in both modes the peripheral modules are operational and are able to generate interrupts, which can trigger capture events. It is also possible to generate DMA request in both modes.

In Standby mode the RTI Module will generate Compare, Timebase and Overflow interrupts. The Compare interrupts will periodically wake up the device. The Overflow interrupt will notify the operating system that a counter overflow occured. When the device is put into Standby mode, the peripheral which is generating the external clock NTU is no longer active and the Timebase Control circuitry has to switch to internal clocking scheme, when it detects a missing clock on NTU. The Timebase interrupt will wake up the device and the application software will be able to adapt the periodic interrupt generated, since the DMA controller will also be powered down. This will prevent DMA transfers after waking up the device, which were probably requested at a time, which does not correlate to the current state of the system. Capturing events while in Standby mode is also not supported.

In the special case of Standby Mode with PLL off, RTICLK might have a different period than with PLL enabled, since RTICLK will be derived from the oscillator output.

Halt Mode will completely deactivate the RTI Module.

#### 1.7.5 Suspend Mode Behaviour

Once the system enters suspend mode, the behaviour of the RTI depends on the COS bit (RTIGCTRL.15). If the bit is cleared and suspend is active, all counters will stop operation. If the bit is set to one, all counters will be clocked normally and the RTI will work like in normal mode. However if the external timebase (NTU) is used and the system is suspended, the timebase control circuit will switch to internal timebase, once it detects the missing NTU signal of the suspended communication controller. This has to be signaled with an TBINT, so that software can resynchronize after suspend is released.

The Analog Watchdog will not be serviced by software in suspend mode. In order to avoid reset generation, the external capacitor will be discharged while in suspend mode.

The DWD counter will not decrement in suspend mode and will hold its current value while in suspend mode.

# 1.8 Control Registers

#### 1.8.1 Control registers

This section describes the Real Time Interrupt Module registers The registers support 8-bit, 16-bit and 32-bit writes. The offset is relative to the associated peripheral select.

| Offset                |                   |                |                  |              |              |              |            |              |              |

|-----------------------|-------------------|----------------|------------------|--------------|--------------|--------------|------------|--------------|--------------|

| Address†<br>Register  | 31 30 29<br>15 14 | 28 27<br>13 12 | 26 25<br>11 10 9 | 24 23<br>9 8 | 22 21<br>7 6 | 20<br>5 4    | 19 18<br>3 | 17<br>2 1    | 16<br>0      |

| 0x00 RTIGC-<br>TRL    |                   |                |                  | Reserve      | d            |              |            |              |              |

|                       | cos               |                |                  | Reserved     |              |              |            | CNT1<br>EN   | CNT0<br>EN   |

| 0x04 RTITBC-<br>TRL   |                   |                |                  | Reserve      | d            |              |            |              |              |

|                       |                   |                | Res              | erved        |              |              |            | INC          | TB<br>EXT    |

| 0x08 RTICAPC-<br>TRL  |                   |                |                  | Reserve      | d            |              |            |              |              |

|                       |                   |                | Res              | erved        |              |              |            | CAP<br>CNTR1 | CAP<br>CNTR0 |

| 0x0C RTICOM-<br>PCTRL |                   |                |                  | Reserve      | d            |              |            |              |              |

|                       | Reserved          | COMP<br>SEL3   | Reserved         | COMP<br>SEL2 | Reserved     | COMP<br>SEL1 | Res        | erved        | COMP<br>SEL0 |

| 0x10 RTIFRC0          |                   |                |                  | FRC0 31      | :0           |              |            |              |              |

|                       |                   |                |                  |              |              |              |            |              |              |

| 0x14 RTIUC0           |                   |                |                  | UC0 31:      | 0            |              |            |              |              |

|                       |                   |                |                  |              |              |              |            |              |              |

Table 1–2. RTI Registers

Real Time Interrupt Module 1-19

Table 1–2. RTI Registers (Continued)

Table 1–2. RTI Registers (Continued)

1-21 Real Time Interrupt Module

Table 1–2. RTI Registers (Continued)

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

1-22

| able 1–2.                      | RTI Registers (Continued)                                                                |

|--------------------------------|------------------------------------------------------------------------------------------|

| Offset<br>Address†<br>Register | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16<br>15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| 0x90 RTID-<br>WDCTRL           | DWDCTRL[31:0]                                                                            |

|                                |                                                                                          |

| 0x94 RTIDWD-<br>PRLD           | Reserved                                                                                 |

|                                | Reserved DWDPRLD                                                                         |

| 0x98 RTIWD-<br>STATUS          | Reserved                                                                                 |

|                                | Reserved KEYST DWDS AWDS                                                                 |

| 0x9C RTIWD-<br>KEY             | Reserved                                                                                 |

|                                | WDKEY                                                                                    |

| 0xA0 RTIDWD-<br>CNTR           | Reserved DWDCNTR                                                                         |

|                                | DWDCNTR                                                                                  |

Table 1–2. RTI Registers (Continued)

Real Time Interrupt Module 1-23

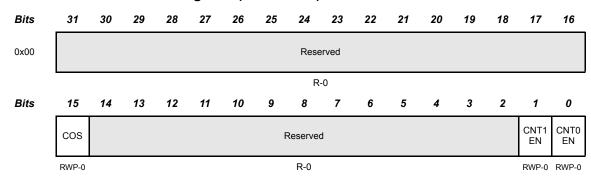

## 1.8.2 RTI Global Control Register (RTIGCTRL)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -*n* = Value after reset

#### Bits 31:16 Reserved.

Reads return 0 and writes have no effect

#### Bit 15 COS: Continue On Suspend.

This bit determines if both counters are stopped when the device goes into debug mode or if they continue counting.

User and privilege mode (read):

0 = counters are stopped while in debug mode

1 = counters are running while in debug mode

Privilege mode (write):

0 = stop counters in debug mode

1 = continue counting in debug mode

#### Bits 14:2 Reserved.

Reads return 0 and writes have no effect

### Bit 1 CNT1EN: Counter 1 Enable.

The CNT1EN bit starts and stops the operation of counter block 1 (UC1 and FRC1).

User and privilege mode (read):

0 = counters are stopped

1 = counters are running

Privilege mode (write):

0 = stop counters

1 = start counters

#### Bit 0 CNT0EN: Counter 0 Enable.

The CNT0EN bit starts and stops the operation of counter block 0 (UC0 and FRC0).

User and privilege mode (read):

0 = counters are stopped

1 = counters are running

Privilege mode (write):

0 = stop counters

1 = start counters

Real Time Interrupt Module 1-25

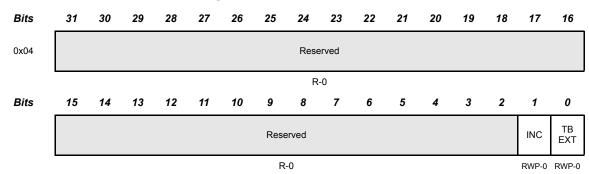

#### 1.8.3 RTI Timebase Control Register (RTITBCTRL)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bits 31:2 Reserved.

Reads return 0 and writes have no effect

#### Bit 1 INC: Increment Free Running Counter 0.

This bit determines wether the Free Running Counter 0 is automatically incremented if a failing clock on the NTU signal is detected.

User and privilege mode (read):

- 0 = FRC0 will not be incremented

- 1 = FRC0 will be incremented

Privilege mode (write):

- 0 = Do not increment FRC0 on failing external clock

- 1 = Increment FRC0 on failing external clock

#### Bit 0 TBEXT: Timebase External.

The Timebase External bit selects whether the Free Running Counter 0 is clocked by the internal Up Counter 0 or from the external signal NTU. Since setting the TBEXT bit to 1 resets Up Counter 0, Free Running Counter 0 will not be incremented in this occurrence. The only source which is able to increment Free Running Counter 0 is NTU.

When the Timebase Supervisor circuit detects a missing clockedge, then the TBEXT bit is reset.

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

The selection if the external signal should be used, can only be done by software.

User and privilege mode (read):

0 = UC0 clocks FRC0

1 = NTU clocks FRC0

Privilege mode (write):

- 0 = MUX is switched to internal UC0 clocking scheme

- 1 = MUX is switched to external NTU clocking scheme

Real Time Interrupt Module 1-27

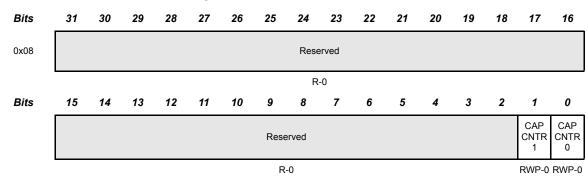

#### 1.8.4 RTI Capture Control Register (RTICAPCTRL)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -*n* = Value after reset

#### Bits 31:2 Reserved.

Reads return 0 and writes have no effect

#### Bit 1 CAPCNTR1: Capture Counter 1.

This bit determines, which external interrupt source triggers a capture event of both UC1 and FRC1.

User and privilege mode (read):

- 0 = capture event is triggered by Capture Event Source 0

- 1 = capture event is triggered by Capture Event Source 1

Privilege mode (write):

- 0 = enable capture event triggered by Capture Event Source 0

- 1 = enable capture event triggered by Capture Event Source 1

#### Bit 0 CAPCNTR0: Capture Counter 0.

This bit determines, which external interrupt source triggers a capture event of both UC0 and FRC0.

User and privilege mode (read):

- 0 = capture event is triggered by Capture Event Source 0

- 1 = capture event is triggered by Capture Event Source 1

Privilege mode (write):

0 = enable capture event triggered by Capture Event Source 0

1 = enable capture event triggered by Capture Event Source 1

Real Time Interrupt Module 1-29

| Bits | 31 | 30       | 29 | 28           | 27 | 26       | 25 | 24           | 23   | 22       | 21 | 20           | 19 | 18       | 17 | 16           |

|------|----|----------|----|--------------|----|----------|----|--------------|------|----------|----|--------------|----|----------|----|--------------|

| 0x0C |    |          |    |              |    |          |    | Rese         | rved |          |    |              |    |          |    |              |

|      |    |          |    |              |    |          |    | R-           | 0    |          |    |              |    |          |    |              |

| Bits | 15 | 14       | 13 | 12           | 11 | 10       | 9  | 8            | 7    | 6        | 5  | 4            | 3  | 2        | 1  | 0            |

|      | F  | Reserved | ł  | COMP<br>SEL3 |    | Reserved |    | COMP<br>SEL2 | ł    | Reserved |    | COMP<br>SEL1 |    | Reserved |    | COMP<br>SEL0 |

|      |    | R-0      |    | RWP-0        |    | R-0      |    | RWP-0        |      | R-0      |    | RWP-0        |    | R-0      |    | RWP-0        |

#### 1.8.5 RTI Compare Control Register (RTICOMPCTRL)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bits 31:13 Reserved.

Reads return 0 and writes have no effect

#### Bit 12 COMPSEL3: Compare Select 3.

This bit determines the counter with which the compare value hold in compare register 3 is compared.

User and privilege mode (read):

0 = value will be compared with FRC 0

1 = value will be compared with FRC 1

Privilege mode (write):

0 = enable compare with FRC 0

1 = enable compare with FRC 1

#### Bits 11:9 Reserved.

Reads return 0 and writes have no effect

#### Bit 8 COMPSEL2: Compare Select 2.

This bit determines the counter with which the compare value hold in compare register 2 is compared.

User and privilege mode (read):

0 = value will be compared with FRC 0

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

|          | 1 = value will be compared with FRC 1                                                                |

|----------|------------------------------------------------------------------------------------------------------|

|          | Privilege mode (write):                                                                              |

|          | 0 = enable compare with FRC 0                                                                        |

|          | 1 = enable compare with FRC 1                                                                        |

| Bits 7:5 | Reserved.                                                                                            |

|          | Reads return 0 and writes have no effect                                                             |

| Bit 4    | COMPSEL1: Compare Select 1.                                                                          |

|          | This bit determines the counter with which the compare value hold in compare register 1 is compared. |

|          | User and privilege mode (read):                                                                      |

|          | 0 = value will be compared with FRC 0                                                                |

|          | 1 = value will be compared with FRC 1                                                                |

|          | Privilege mode (write):                                                                              |

|          | 0 = enable compare with FRC 0                                                                        |

|          | 1 = enable compare with FRC 1                                                                        |

| Bits 3:1 | Reserved.                                                                                            |

|          | Reads return 0 and writes have no effect                                                             |

| Bit 0    | COMPSEL0: Compare Select 0.                                                                          |

|          | This bit determines the counter with which the compare value hold in compare register 0 is compared. |

|          | User and privilege mode (read):                                                                      |

|          | 0 = value will be compared with FRC 0                                                                |

|          | 1 = value will be compared with FRC 1                                                                |

|          | Privilege mode (write):                                                                              |

|          | 0 = enable compare with FRC 0                                                                        |

|          | 1 = enable compare with FRC 1                                                                        |

|          |                                                                                                      |

1-31

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24   | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 1 |

|----|----|----|----|----|----|----|------|------|----|----|----|----|----|----|---|

|    |    |    |    |    |    |    | FRC0 | 31:0 |    |    |    |    |    |    |   |

|    |    |    |    |    |    |    | RW   | P-0  |    |    |    |    |    |    |   |

| 5  | 14 | 12 | 12 | 11 | 10 | 9  | 8    | 7    | 6  | 5  | 4  | 3  | 2  | 1  |   |

#### 1.8.6 RTI Free Running Counter 0 Register (RTIFRC0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 FRC0: Free Running Counter 0.

This registers holds the current value of the Free Running Counter 0 and will be updated continuously.

User and privilege mode (read):

current value of the counter

Privilege mode (write):

the counter can be preset by writing to this register. The counter increments then from this written value upwards.

If counters have to be preset, they have to be disabled in the RTIGCTRL register in order to ensure consistency between RTIUC0 and RTIFRC0.

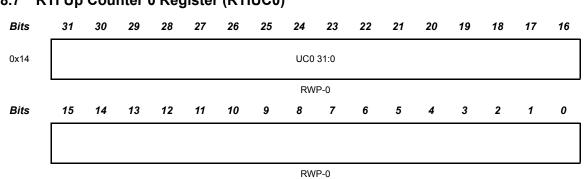

#### 1.8.7 RTI Up Counter 0 Register (RTIUC0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 UC0: Up Counter 0.

This registers holds the current value of the Up Counter 0 and prescales the RTI clock. It will be only updated by a previous read of Free Running Counter 0. This gives effectively a 64 bit read of both counters, without having the problem of a counter being updated between two consecutive reads on Up Counter 0 and Free Running Counter 0.

User and privilege mode (read):

value of the counter when the Free Running Counter 0 was read

Privilege mode (write):

the counter can be preset by writing to this register. The counter increments then from this written value upwards.

If counters have to be preset, they have to be disabled in the RTIGCTRL register in order to ensure consistency between RTIUC0 and RTIFRC0.

If the preset value is bigger than the compare value stored in register RTICPUC0 then it can take a long time until a compare matches, since RTIUC0 has to count up until it overflows.

| 31    | 30 | 29 |    |    |    |    |      |        |    |    |    |    |    |    |    |

|-------|----|----|----|----|----|----|------|--------|----|----|----|----|----|----|----|

|       |    | 29 | 28 | 27 | 26 | 25 | 24   | 23     | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|       |    |    |    |    |    |    | CPUC | 0 31:0 |    |    |    |    |    |    |    |

| RWP-0 |    |    |    |    |    |    |      |        |    |    |    |    |    |    |    |

| 5     | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

#### 1.8.8 RTI Compare Up Counter 0 Register (RTICPUC0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 CPUC0: Compare Up Counter 0.

This registers holds the compare value, which is compared with the Up Counter 0. When the compare matches, Free Running counter 0 is incremented. The Up Counter is set to zero when the counter value matches the CPUC0 value. The value set in this prescales the RTI clock.

$$f_{FRC0} = \frac{RTICLK}{CPUC0 + 1}$$

User and privilege mode (read):

current compare value

Privilege mode (write when TBEXT = 0):

the compare value is updated

Privilege mode (write when TBEXT = 1):

the compare value is not changed

## 1.8.9 RTI Capture Free Running Counter 0 Register (RTICAFRC0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -*n* = Value after reset

#### Bit 31:0 CAFRC0: Capture Free Running Counter 0.

This registers captures the current value of the Free Running Counter 0 when a event occurs, controlled by the external capture control block.

User and privilege mode (read):

value of Free Running Counter 0 on a capture event

Real Time Interrupt Module 1-35

| Bits | 31         | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|------|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0x24 | CAUC0 31:0 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|      | R-0        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Bits | 15         | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|      |            |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|      |            |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|      | R-0        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

#### 1.8.10 RTI Capture Up Counter 0 Register (RTICAUC0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 CAUC0: Capture Up Counter 0.

This registers captures the current value of the Up Counter 0 when a event occurs, controlled by the external capture control block. The read sequence has to be the same as with Up Counter 0 and Free Running Counter 0. So the RTICAFRC0 register has to be read first, before the RTICAUC0 register is read. This sequence ensures that the value of the RTICAUC0 register is the corresponding value to the RTICAFRC0 register, even if another capture event happens in between the two reads.

User and privilege mode (read):

value of Up Counter 0 on a capture event

# 1.8.11 RTI Free Running Counter 1 Register (RTIFRC1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 FRC1: Free Running Counter 1.

This registers holds the current value of the Free Running Counter 1 and will be updated continuously.

User and privilege mode (read):

current value of the counter

Privilege mode (write):

the counter can be preset by writing to this register. The counter increments then from this written value upwards.

If counters have to be preset, they have to be disabled in the RTIGCTRL register in order to ensure consistency between UC1 and FRC1.

Real Time Interrupt Module 1-37

|      | •  |    |    |    | 0  | `  |    | '   |      |    |    |    |    |    |    |    |

|------|----|----|----|----|----|----|----|-----|------|----|----|----|----|----|----|----|

| Bits | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24  | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| 0x34 |    |    |    |    |    |    |    | UC1 | 31:0 |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    | RW  | P-0  |    |    |    |    |    |    |    |

| Bits | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|      |    |    |    |    |    |    |    |     |      |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    |     |      |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    | RW  | P-0  |    |    |    |    |    |    |    |

#### 1.8.12 RTI Up Counter 1 Register (RTIUC1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 UC1: Up Counter 1.

This registers holds the current value of the Up Counter 1 and prescales the RTI clock. It will be only updated by a previous read of Free Running Counter 1. This gives effectively a 64 bit read of both counters, without having the problem of a counter being updated between two consecutive reads on Up Counter 1 and Free Running Counter 1.

User and privilege mode (read):

value of the counter when the Free Running Counter 1 was read

Privilege mode (write):

the counter can be preset by writing to this register. The counter increments then from this written value upwards.

If counters have to be preset, they have to be disabled in the RTIGCTRL register in order to ensure consistency between UC1 and FRC1.

If the preset value is bigger than the compare value stored in register RTICPUC1 then it can take a long time until a compare matches, since UC1 has to count up until it overflows.

# 1.8.13 RTI Compare Up Counter 1 Register (RTICPUC1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 CPUC1: Compare Up Counter 1.

This registers holds the compare value, which is compared with the Up Counter 1. When the compare matches, Free Running Counter 1 is incremented. The Up Counter is set to zero when the counter value matches the CPUC1 value. The value set in this prescales the RTI clock.

$$f_{FRC1} = \frac{RTICLK}{CPUC1+1}$$

User and privilege mode (read):

current compare value

Privilege mode (write):

the compare value is updated

Real Time Interrupt Module 1-39

| Bits | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24    | 23      | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|------|----|----|----|----|----|----|----|-------|---------|----|----|----|----|----|----|----|

| 0x40 |    |    |    |    |    |    |    | CAFRO | 21 31:0 |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    | R     | -0      |    |    |    |    |    |    |    |

| Bits | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7       | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|      |    |    |    |    |    |    |    |       |         |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    |       |         |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    | R     | -0      |    |    |    |    |    |    |    |

# 1.8.14 RTI Capture Free Running Counter 1 Register (RTICAFRC1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

## Bit 31:0 CAFRC1: Capture Free Running Counter 1.

This registers captures the current value of the Free Running Counter 1 when a event occurs, controlled by the external capture control block.

User and privilege mode (read):

value of Free Running Counter 1 on a capture event

# 1.8.15 RTI Capture Up Counter 1 Register (RTICAUC1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 CAUC1: Capture Up Counter 1.

This registers captures the current value of the Up Counter 1 when a event occurs, controlled by the external capture control block. The read sequence has to be the same as with Up Counter 1 and Free Running Counter 1. So the RTICAFRC1 register has to be read first, before the RTICAUC1 register is read. This sequence ensures that the value of the RTICAUC0 register is the corresponding value to the RTICAFRC0 register, even if another capture event happens in between the two reads.

User and privilege mode (read):

value of Up Counter 1 on a capture event

Real Time Interrupt Module 1-41

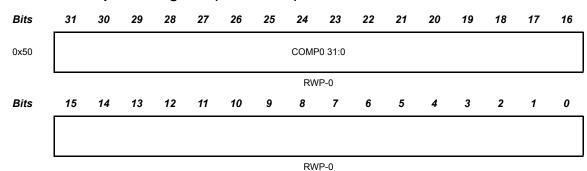

# 1.8.16 RTI Compare 0 Register (RTICOMP0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 COMP0: Compare 0.

This registers holds a compare value, which is compared with the counter selected in the compare control logic. If the Free Running Counter matches the compare value, an interrupt is flagged. With this register it is also possible to initiate a DMA request.

User and privilege mode (read):

current compare value

Privilege mode (write):

update of the compare register with a new compare value

A reset does not generate a compare match, since the compare logic will only be active, when the associated counter block is enabled.

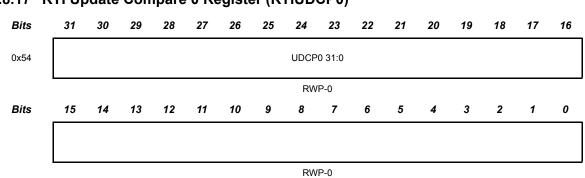

# 1.8.17 RTI Update Compare 0 Register (RTIUDCP0)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 UDCP0: Update Compare 0 Register.

This registers holds a value, which is added to the value in the compare 0 register each time a compare matches. This gives the possibility to generate periodic interrupts without software intervention.

User and privilege mode (read):

value to be added to the compare 0 register on the next compare match

Privilege mode (write):

new update value

# 1.8.18 RTI Compare 1 Register (RTICOMP1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -*n* = Value after reset

#### Bit 31:0 COMP1: Compare 1.

This registers holds a compare value, which is compared with the counter selected in the compare control logic. If the Free Running Counter matches the compare value, an interrupt is flagged. With this register it is also possible to initiate a DMA request.

User and privilege mode (read):

current compare value

Privilege mode (write):

update of the compare register with a new compare value

A reset does not generate a compare match, since the compare logic will only be active, when the associated counter block is enabled.

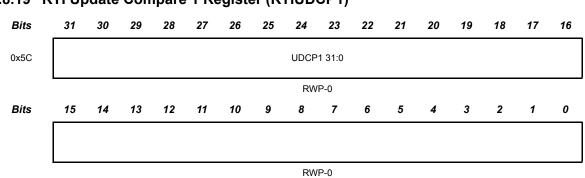

# 1.8.19 RTI Update Compare 1 Register (RTIUDCP1)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 UDCP1: Update Compare 1 Register.

This registers holds a value, which is added to the value in the compare 1 register each time a compare matches. This gives the possibility to generate periodic interrupts without software intervention.

User and privilege mode (read):

value to be added to the compare 1 register on the next compare match

Privilege mode (write):

new update value

Real Time Interrupt Module

1-45

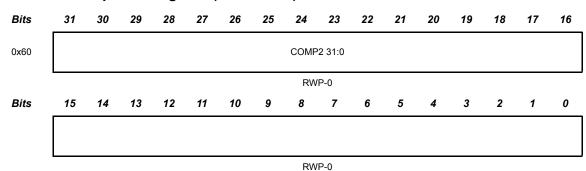

# 1.8.20 RTI Compare 2 Register (RTICOMP2)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 COMP2: Compare 2.

This registers holds a compare value, which is compared with the counter selected in the compare control logic. If the Free Running Counter matches the compare value, an interrupt is flagged. With this register it is also possible to initiate a DMA request.

User and privilege mode (read):

current compare value

Privilege mode (write):

update of the compare register with a new compare value

A reset does not generate a compare match, since the compare logic will only be active, when the associated counter block is enabled.

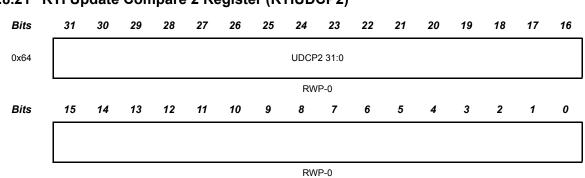

# 1.8.21 RTI Update Compare 2 Register (RTIUDCP2)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 UDCP2: Update Compare 2 Register.

This registers holds a value, which is added to the value in the compare 2 register each time a compare matches. This gives the possibility to generate periodic interrupts without software intervention.

User and privilege mode (read):

value to be added to the compare 2 register on the next compare match

Privilege mode (write):

new update value

1-47

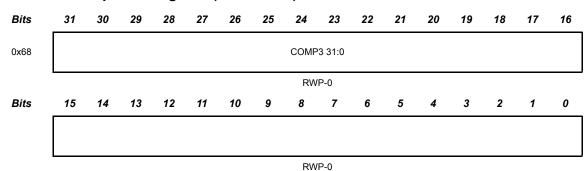

# 1.8.22 RTI Compare 3 Register (RTICOMP3)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 COMP3: Compare 3.

This registers holds a compare value, which is compared with the counter selected in the compare control logic. If the Free Running Counter matches the compare value, an interrupt is flagged. With this register it is also possible to initiate a DMA request.

User and privilege mode (read):

current compare value

Privilege mode (write):

update of the compare register with a new compare value

A reset does not generate a compare match, since the compare logic will only be active, when the associated counter block is enabled.

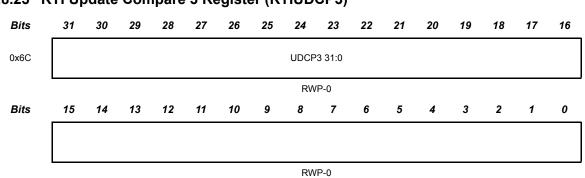

# 1.8.23 RTI Update Compare 3 Register (RTIUDCP3)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 UDCP3: Update Compare 3 Register.

This registers holds a value, which is added to the value in the compare 3 register each time a compare matches. This gives the possibility to generate periodic interrupts without software intervention.

User and privilege mode (read):

value to be added to the compare 3 register on the next compare match

Privilege mode (write):

new update value

Real Time Interrupt Module 1-49

| Bits | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24     | 23        | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|------|----|----|----|----|----|----|----|--------|-----------|----|----|----|----|----|----|----|

| 0x70 |    |    |    |    |    |    | -  | TBLCON | 1P 31 : ( | )  |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    | RW     | P-0       |    |    |    |    |    |    |    |

| Bits | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      | 7         | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|      |    |    |    |    |    |    |    |        |           |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    |        |           |    |    |    |    |    |    |    |

|      |    |    |    |    |    |    |    | RW     | P-0       |    |    |    |    |    |    |    |

# 1.8.24 RTI External Clock Timebase Low Compare Register (RTITBLCOMP)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

# Bit 31:0 TBLCOMP: Timebase Low Compare Value.

This value determines when the edge detection circuit starts monitoring the NTU signal. It will be compared with Up Counter 0.

User and privilege mode (read):

current compare value

Privilege mode (write when TBEXT = 0):

the compare value is updated

Privilege mode (write when TBEXT = 1):

the compare value is not changed

A reset does not generate a compare match.

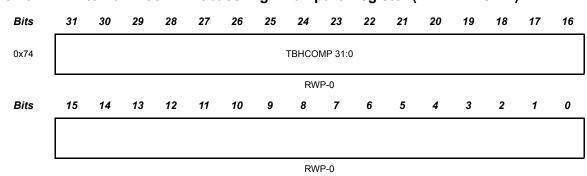

## 1.8.25 RTI External Clock Timebase High Compare Register (RTITBHCOMP)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

#### Bit 31:0 TBHCOMP: Timebase High Compare Value.

This value determines when the edge detection circuit will stop monitoring the NTU signal. It will be compared with Up Counter 0.

RTITBHCOMP has to be less than RTICPUC0, since RTIUC0 will be reset when RTICPUC0 is reached.

Example:

The NTU edge detection circuit should be active +/- 10 RTICLK cycles around RTICPUC0.

RTICPUC0 = 0x00000050 RTITBLCOMP = 0x000046 RTITBHCOMP = 0x0000009

User and privilege mode (read):

current compare value

Privilege mode (write when TBEXT = 0):

the compare value is updated

Privilege mode (write when TBEXT = 1):

the compare value is not changed

A reset does not generate a compare match.

Real Time Interrupt Module

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information 1-51

| Bits | 31 | 30   | 29   | 28 | 27          | 26          | 25          | 24          | 23 | 22   | 21   | 20 | 19          | 18                 | 17                 | 16           |

|------|----|------|------|----|-------------|-------------|-------------|-------------|----|------|------|----|-------------|--------------------|--------------------|--------------|

| 0x80 |    |      |      |    |             | F           | Reserve     | d           |    |      |      |    |             | SET<br>OVL1<br>INT | SET<br>OVL0<br>INT | SET<br>TBINT |

|      |    |      |      |    |             |             | R-0         |             |    |      |      |    |             | RWP-0              | RWP-0              | RWP-0        |

| Bits | 15 | 14   | 13   | 12 | 11          | 10          | 9           | 8           | 7  | 6    | 5    | 4  | 3           | 2                  | 1                  | 0            |

|      |    | Rese | rved |    | SET<br>DMA3 | SET<br>DMA2 | SET<br>DMA1 | SET<br>DMA0 |    | Rese | rved |    | SET<br>INT3 | SET<br>INT2        | SET<br>INT1        | SET<br>INT0  |

|      |    | R-   | -0   |    | RWP-0       | RWP-0       | RWP-0       | RWP-0       |    | R    | -0   |    | RWP-0       | RWP-0              | RWP-0              | RWP-0        |

# 1.8.26 RTI Set/Status Interrupt Register (RTISETINT)

R = Read, W = Write, P = Privilege Mode, U = Undefined; -n = Value after reset

This register prevents the necessity of a read-modify-write operation if a particular interrupt should be enabled.

#### Bits 31:19 Reserved.

Reads return 0 and writes have no effect

# Bit 18 SETOVL1INT: Set Free Running Counter 1 Overflow Interrupt.

User and privilege mode (read):

- 0 = interrupt is disabled

- 1 = interrupt is enabled

Privilege mode (write):

- 0 = leaves the corresponding bit unchanged

- 1 = enable interrupt

#### Bit 17 SETOVL0INT: Set Free Running Counter 0 Overflow Interrupt.

User and privilege mode (read):

- 0 = interrupt is disabled

- 1 = interrupt is enabled

- Privilege mode (write):

- 0 = leaves the corresponding bit unchanged

- 1 = enable interrupt

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

| Bit 16    | SETTBINT: Set Timebase Interrupt.          |

|-----------|--------------------------------------------|

|           | User and privilege mode (read):            |

|           | 0 = interrupt is disabled                  |

|           | 1 = interrupt is enabled                   |

|           | Privilege mode (write):                    |

|           | 0 = leaves the corresponding bit unchanged |

|           | 1 = enable interrupt                       |

| Bits15:12 | Reserved.                                  |

|           | Reads return 0 and writes have no effect   |

| Bit 11    | SETDMA3: Set Compare DMA Request 3.        |

|           | User and privilege mode (read):            |

|           | 0 = DMA request is disabled                |

|           | 1 = DMA request is enabled                 |

|           | Privilege mode (write):                    |

|           | 0 = leaves the corresponding bit unchanged |

|           | 1 = enable DMA request                     |

| Bit 10    | SETDMA2: Set Compare DMA Request 2.        |

|           | User and privilege mode (read):            |

|           | 0 = DMA request is disabled                |

|           | 1 = DMA request is enabled                 |

|           | Privilege mode (write):                    |

|           | 0 = leaves the corresponding bit unchanged |

|           | 1 = enable DMA request                     |

| Bit 9     | SETDMA1: Set Compare DMA Request 1.        |

|           | User and privilege mode (read):            |

|           | 0 = DMA request is disabled                |

Real Time Interrupt Module

1-53

|                | 1 = DMA request is enabled                                                                                                                                                                                                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Privilege mode (write):                                                                                                                                                                                                                                                                        |

|                | 0 = leaves the corresponding bit unchanged                                                                                                                                                                                                                                                     |

|                | 1 = enable DMA request                                                                                                                                                                                                                                                                         |

| Bit 8          | SETDMA0: Set Compare DMA Request 0.                                                                                                                                                                                                                                                            |

|                | User and privilege mode (read):                                                                                                                                                                                                                                                                |

|                | 0 = DMA request is disabled                                                                                                                                                                                                                                                                    |

|                | 1 = DMA request is enabled                                                                                                                                                                                                                                                                     |

|                | Privilege mode (write):                                                                                                                                                                                                                                                                        |

|                | 0 = leaves the corresponding bit unchanged                                                                                                                                                                                                                                                     |

|                | 1 = enable DMA request                                                                                                                                                                                                                                                                         |

| Bits 7:4       | Reserved.                                                                                                                                                                                                                                                                                      |

|                | Reads return 0 and writes have no effect                                                                                                                                                                                                                                                       |

|                |                                                                                                                                                                                                                                                                                                |

| Bit 3          | SETINT3: Set Compare Interrupt 3.                                                                                                                                                                                                                                                              |

| Bit 3          | SETINT3: Set Compare Interrupt 3.<br>User and privilege mode (read):                                                                                                                                                                                                                           |

| Bit 3          |                                                                                                                                                                                                                                                                                                |

| Bit 3          | User and privilege mode (read):                                                                                                                                                                                                                                                                |

| Bit 3          | User and privilege mode (read):<br>0 = interrupt is disabled                                                                                                                                                                                                                                   |

| Bit 3          | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled                                                                                                                                                                                                       |

| Bit 3          | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled<br>Privilege mode (write):                                                                                                                                                                            |

| Bit 3<br>Bit 2 | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled<br>Privilege mode (write):<br>0 = leaves the corresponding bit unchanged                                                                                                                              |

|                | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled<br>Privilege mode (write):<br>0 = leaves the corresponding bit unchanged<br>1 = enable interrupt                                                                                                      |

|                | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled<br>Privilege mode (write):<br>0 = leaves the corresponding bit unchanged<br>1 = enable interrupt<br>SETINT2: Set Compare Interrupt 2.                                                                 |

|                | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled<br>Privilege mode (write):<br>0 = leaves the corresponding bit unchanged<br>1 = enable interrupt<br>SETINT2: Set Compare Interrupt 2.<br>User and privilege mode (read):                              |

|                | User and privilege mode (read):<br>0 = interrupt is disabled<br>1 = interrupt is enabled<br>Privilege mode (write):<br>0 = leaves the corresponding bit unchanged<br>1 = enable interrupt<br>SETINT2: Set Compare Interrupt 2.<br>User and privilege mode (read):<br>0 = interrupt is disabled |

This documents is a preliminary objective specification. Its content is subject to change during product development. Texas Instruments Proprietary Information

1 = enable interrupt

| Bit 1 | SETINT1: Set Compare Interrupt 1.                                                                                   |

|-------|---------------------------------------------------------------------------------------------------------------------|

|       | User and privilege mode (read):                                                                                     |

|       | 0 = interrupt is disabled                                                                                           |

|       | 1 = interrupt is enabled                                                                                            |

|       | Privilege mode (write):                                                                                             |

|       | 0 = leaves the corresponding bit unchanged                                                                          |

|       | 1 = enable interrupt                                                                                                |

|       |                                                                                                                     |

| Bit 0 | SETINT0: Set Compare Interrupt 0.                                                                                   |

| Bit 0 | SETINT0: Set Compare Interrupt 0.<br>User and privilege mode (read):                                                |