# Analog Engineer's Circuit Cookbook: ADCs

First Edition SLYY138 - 03/2018

Edited by:

Art Kay, Luis Chioye and Dale Li

Special thanks for technical contribution:

Peggy Liska

Cynthia Sosa

Reed Kaczmarek

Bryan McKay

Manuel Chavez

## Analog Engineer's Circuit Cookbook: ADCs

(First Edition)

#### Message from the editors:

The Analog Engineer's Circuit Cookbook: ADCs provides analog-to-digital converter (ADC) sub-circuit ideas that can be quickly adapted to meet your specific system needs. Each circuit is presented as a "definition-by-example." They include step-by-step instructions, like a recipe, with formulas enabling you to adapt the circuit to meet your design goals. Additionally, all circuits are verified with SPICE simulations and include links to the corresponding TINA-TI<sup>TM</sup> SPICE circuits.

We've provided at least one recommended ADC for each circuit, but you can swap it with another device if you've found one that's a better fit for your design. You can search our large portfolio of ADCs at <a href="https://www.ti.com/ADCs">www.ti.com/ADCs</a>.

Our circuits require a basic understanding of amplifier and data converter concepts. If you're new to data converter design, we highly recommend completing our TI Precision Labs (TIPL) training series. TIPL includes courses on introductory topics, such as device architecture, as well as advanced, application-specific problem-solving, using both theory and practical knowledge. Check out our curriculum for op amps, ADCs and more at: <a href="https://www.ti.com/precisionlabs">www.ti.com/precisionlabs</a>.

We plan to update this e-book with new ADC circuit building blocks and encourage you to see if your version is the latest at <a href="https://www.ti.com/circuitcookbooks">www.ti.com/circuitcookbooks</a>. If you have feedback on any of our existing circuits or would like to request additional ADC circuits for the next edition of this e-book, please contact us at <a href="mailto:adccookbook@list.ti.com">adccookbook@list.ti.com</a>.

We hope you find our collection of ADC circuits helpful in developing your designs!

#### Additional resources to explore

#### TI Precision Labs

#### ti.com/precisionlabs

- On-demand courses and tutorials ranging from introductory to advanced concepts that focus on application-specific problem solving

- Hands-on labs and evaluation modules (EVM) available

- TIPL Op Amps experimentation platform, ti.com/TIPL-amp-evm

- TIPL SAR ADC experimentation platform, ti.com/TIPL-adc-evm

#### Analog Engineer's Pocket Reference

#### ti.com/analogrefguide

- PCB, analog and mixed-signal design formulae; includes conversions, tables and equations

- e-book, iTunes app and hardcopy available

#### The Signal e-book

#### ti.com/signalbook

Short, bite-sized lessons on on op-amp design topics, such as offset voltage, input bias current, stability, noise and more

#### **Analog Wire Blog**

#### ti.com/analogwire

Technical blogs written by analog experts that include tips, tricks and design techniques

#### TI Designs

#### ti.com/tidesigns

Ready-to-use reference designs with theory, calculations, simulations schematics, PCB files and bench test results

#### ADC Parametric Quick Search

#### ti.com/ADC-search

• Find your next precision or high-speed ADC

#### DIY Amplifier Circuit Evaluation Module (DIYAMP-EVM) ti.com/DIYAMP-EVM

Single-channel circuit evaluation module providing SC70, SOT23 and SOIC package options in 12 popular amplifier configurations

### Dual-Channel DIY Amplifier Circuit Evaluation Module (DUAL-DIYAMP-EVM)

#### ti.com/dual-diyamp-evm

Dual-channel circuit evaluation module in an SOIC-8 package with 10 popular amplifier configurations

#### TINA-TI simulation software

#### ti.com/tool/tina-ti

- Complete SPICE simulator for DC, AC, transient and noise analysis

- Includes schematic entry and post-processor for waveform math

#### Analog Engineer's Calculator

#### ti.com/analogcalc

ADC and amplifier design tools, noise and stability analysis, PCB and sensor tools

#### TI E2E™ Community

#### ti.com/e2e

• Support forums for all TI products

### **Table of Contents**

| Low-Power/Cost-Optimized Circuits                                                                                        | Low-Level Sensor Input Circuits                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Driving a SAR ADC Directly without a Front-End Buffer Circuit (Low-Power, Low-Sampling-Speed DAQ)                        | Low-Input Bias Current Front End SAR ADC Circuit                                                                                                                                                 |

| Level Translation Input Drive Circuits  High-Voltage Battery Monitor Circuit: ±20 V, 0-10 kHz, 18-Bit Fully Differential | Input Protection, Filtering and Isolation Circuits  Reducing Effects of External RC Filter Circuit on Gain and Drift Error for Integrated Analog Front Ends (AFEs): ±10 V, up to 200 kHz, 16-Bit |

| High-Input Impedance, True Differential, Analog Front End (AFE) Attenuator Circuit for SAR ADCs                          | Commonly Used Auxiliary Circuits  Powering a Dual-Supply Op Amp Circuit with One LDO                                                                                                             |

| 18-Bit                                                                                                                   |                                                                                                                                                                                                  |

## Want more circuits?

- Download the *Analog Engineer's* Circuit Cookbook for op amps

- Browse a complete list of op amp and ADC circuits

Visit ti.com/circuitcookbooks

## Driving a SAR ADC Directly Without a Front-End Buffer Circuit (Low-Power, Low-Sampling-Speed DAQ)

Abhijeet Godbole

#### **Design Description**

This design explains how sensor outputs can be directly interfaced with a SAR ADC input. In applications such as *Environmental Sensors*, *Gas Detectors*, and *Smoke or Fire Detectors*, the input is very slow-moving and the sensor output voltage is sampled at fairly slower speeds (10ksps or so). In such or similar systems, the sensor output can be directly interfaced with the SAR ADC input without the need for a driver amplifier to achieve a small form-factor, low-cost design.

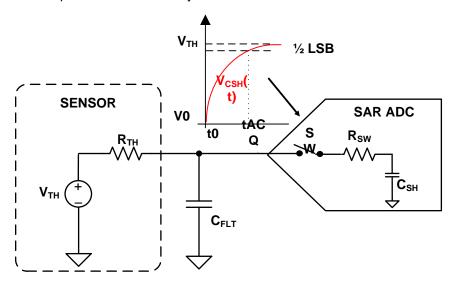

#### Interfacing Sensor Output Directly to a SAR ADC

The following figure shows a typical application diagram for interfacing a sensor directly to a SAR ADC input without the use of a driver amplifier. The sensor block highlights the Thevenin equivalent of a sensor output. Voltage source,  $V_{TH}$ , is the Thevenin-equivalent voltage and source resistance  $R_{TH}$  is the Thevenin-equivalent impedance. Most sensor data sheets provide the Thevenin model of the sensor from which the value of the series impedance can be easily calculated.

#### **Specifications**

| Parameter                                  | Calculated            | Simulated | Measured |

|--------------------------------------------|-----------------------|-----------|----------|

| Transient ADC Input Settling Error         | < 0.5LSB<br>< 100.5µV | 36.24µV   | N/A      |

| Step Input Full Scale Range                | 3.15V                 | 3.15V     | 3.14978  |

| Input Source Impedance (R <sub>TH</sub> )  | 10kΩ                  | 10kΩ      | 10.01kΩ  |

| Filter Capacitor Value (C <sub>FLT</sub> ) | 680pF                 | 680pF     | N/A      |

| ADC Sampling Speed                         | 10ksps                | 10ksps    | 10ksps   |

#### **Design Note**

- 1. Determine source impedance of input signal. Calculate the RC time constant of the input source impedance and filter capacitor (known value).

- 2. Determine the minimum acquisition time required for the input signal to settle for a given source impedance and the filter capacitor combination.

- 3. Select COG capacitors to minimize distortion.

- 4. Use 0.1% 20ppm/°C film resistors or better for good gain drift and to minimize distortion.

#### **Component Selection for ADC Input Settling**

SAR ADCs can be directly interfaced with sensors when the analog input source is capable of driving the switched capacitor load of a SAR ADC and settling the analog input signal to within  $\frac{1}{2}$  of an LSB within the acquisition time of the SAR ADC. To achieve this, the external RC filter ( $R_{TH}$  and  $C_{FLT}$ ) must settle within the acquisition time ( $t_{ACQ}$ ) of the ADC. The relationship between the ADC acquisition time and RC time constant of the external filter is:

$$t_{\text{ACQ}} \ge k \cdot \tau_{\text{FLT}}$$

#### where

- $T_{FLT} = R_{TH} \cdot C_{FLT}$

- · k is the single pole time constant for N bit ADC

The following design example values are given in the table on page 1:

$$R_{TH} = 10k\Omega$$

$C_{FLT} = 680pF$

K = 11 (Single pole time constant multiplier for 14-bit ADC) – More information is found on page 96 and page 97 of the *Analog Engineer's Pocket Reference*.

Minimum acquisition time required for proper settling is calculated using this equation:

$$t_{ACQ} \ge 11 \cdot 10 \text{k}\Omega \cdot 680 \text{pF} = 74.80 \mu \text{s}$$

For more information on SAR ADCs and front end design for SAR ADCs, refer to *Introduction to SAR ADC Front-End Component Selection*.

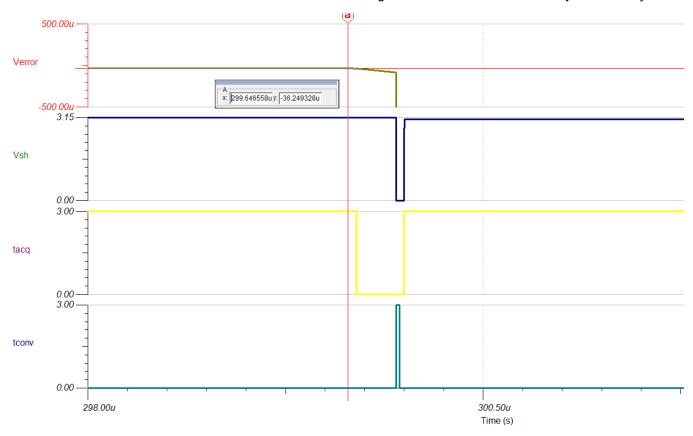

#### Transient Input Settling Simulation using TI-TINA

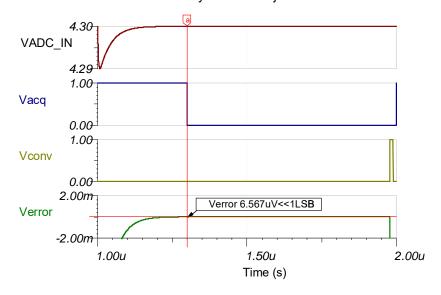

The following figure shows the settling of an *ADS7056* ADC given a 3.15-V DC input signal. This type of simulation shows that the sample and hold kickback circuit is properly selected. Refer to *Refine the Rfilt and Cfilt Values* in the *TI Precision Labs - ADCs* training video series for detailed theory on this subject.

#### Increasing Acquisition Time of SAR ADC for Input Signal Settling

The acquisition time of a SAR ADC can be increased by reducing the throughput in the following ways:

- 1. Reducing the SCLK frequency to reduce the throughput.

- 2. Keeping the SCLK fixed at the highest permissible value and increasing the CS high time.

The following table lists the acquisition time for the previous two cases for the *ADS7056* SAR ADC operating at 10ksps throughput (tcycle = 100µs). Case 2 provides a longer acquisition time for the input signal to settle because of the increased frequency of the SCLK given a fixed conversion and cycle time.

| Case | SCLK    | t <sub>cycle</sub> | Conversion Time (18 · t <sub>SCLK</sub> ) | Acquisition Time<br>(t <sub>cycle</sub> – t <sub>conv</sub> ) |

|------|---------|--------------------|-------------------------------------------|---------------------------------------------------------------|

| 1    | 0.24MHz | 100µs              | 74.988µs                                  | 25.01µs                                                       |

| 2    | 60MHz   | 100µs              | 0.3µs                                     | 99.70µs                                                       |

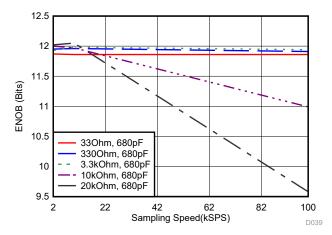

The following table shows a performance comparison between an 8-, 10-, 12-, and 14-bit ADC with respect to sampling speed and effective number of bits (ENOB) when a sensor output with an output impedance of  $10k\Omega$  is directly interfaced with the ADC input. As expected, the ENOB degrades with higher sampling rates because the acquisition time decreases.

| Sampling<br>Speed (ksps) | ADS7040 (8-bit ADC) ENOB ( $R_{TH}$ = 10k $\Omega$ , $C_{FLT}$ = 1.5nF) | ADS7041 (10-bit ADC)<br>ENOB ( $R_{TH}$ = 10k $\Omega$ ,<br>$C_{FLT}$ = 1.5nF) | ADS7042 (12-bit ADC)<br>ENOB (R <sub>TH</sub> = 10kΩ, C <sub>FLT</sub> = 1.5nF) | ADS7056 (14-bit ADC)<br>ENOB ( $R_{TH} = 10k\Omega$ , $C_{FLT} = 680pF$ ) |

|--------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 10                       | 7.93                                                                    | 9.87                                                                           | 10                                                                              | 12.05                                                                     |

| 100                      | 7.92                                                                    | 9.85                                                                           | 9.97                                                                            | 10.99                                                                     |

| 500                      | 7.88                                                                    | 9.68                                                                           | 9.95                                                                            | 8.00                                                                      |

#### Performance Achieved at Different Throughput Rates with Different Source impedance

The following figure provides the ENOB achieved from the ADS7056 at different throughout with different input impedances. Note that all the results for were taken without an ADC driver amplifier.

#### www.ti.com

#### **Design Featured Devices:**

| Device  | Key Features                                                                                              | Link                              | Other Possible Devices |

|---------|-----------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|

| ADS7040 | 8-bit resolution, SPI, 1-Msps sample rate, single-<br>ended input, AVDD/Vref input range 1.6V to<br>3.6V. | http://www.ti.com/product/ADS7040 | Similar Devices        |

| ADS7041 | 10-bit resolution, SPI, 1Msps sample rate, single-ended input, AVDD/Vref input range 1.6V to 3.6V.        | http://www.ti.com/product/ADS7041 | Similar Devices        |

| ADS7042 | 12-bit resolution, SPI, 1-Msps sample rate, single-ended input, AVDD/Vref input range 1.6V to 3.6V.       | http://www.ti.com/product/ADS7042 | Similar Devices        |

| ADS7056 | 14-bit resolution, SPI, 2.5-Msps sample rate, single-ended input, AVDD/Vref input range 1.6V to 3.6V.     | http://www.ti.com/product/ADS7056 | Similar Devices        |

**NOTE:** The ADS7042 and ADS7056 use the AVDD as the reference input. A high-PSRR LDO, such as the TPS7A47, should be used as the power supply.

#### Link to Key files

Source Files for Interfacing Sensor Output Directly with SAR ADCs (http://www.ti.com/lit/zip/sbac178)

For direct support from TI Engineers use the E2E community:

e2e.ti.com

Other Links

www.ti.com/adcs www.ti.com/opamp

SBAA251-November 2017

## Low-Power Sensor Measurements: 3.3-V, 1-ksps, 12-bit, Single-Ended, Dual-Supply Circuit

#### Reed Kaczmarek

| Input                     | ADC Input                | Digital Output ADS7042                 |

|---------------------------|--------------------------|----------------------------------------|

| V <sub>inMin</sub> = 0V   | AIN_P = 0V, AIN_M = 0V   | 000 <sub>H</sub> or 0 <sub>10</sub>    |

| V <sub>inMax</sub> = 3.3V | AIN_P = 3.3V, AIN_M = 0V | FFF <sub>H</sub> or 4096 <sub>10</sub> |

| Power Supplies                       |  |  |  |  |

|--------------------------------------|--|--|--|--|

| AVDD V <sub>ee</sub> V <sub>dd</sub> |  |  |  |  |

| 3.3V -0.3V 4.5V                      |  |  |  |  |

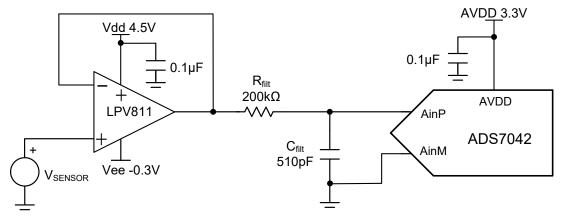

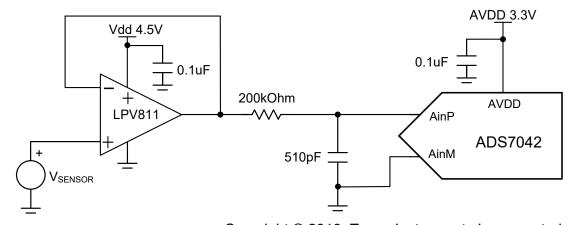

#### **Design Description**

**INSTRUMENTS**

This design shows an low-power amplifier being used to drive a SAR ADC that consumes only nW of power during operation. This design is intended for systems collecting sensor data and require a low-power signal chain which only burns single-digit µW of power. *PIR sensors*, *gas sensors*, and *glucose monitors* are a few examples of power-sensitive systems that benefit from this SAR ADC design. The values in the component selection section can be adjusted to allow for different data throughput rates and different bandwidth amplifiers. *Low-Power Sensor Measurements: 3.3 V, 1 ksps, 12-bit Single-Ended, Single Supply* shows a simplified version of this circuit where the negative supply is grounded. The –0.3-V negative supply in this example is used to achieve the best possible linear input signal range. See *SAR ADC Power Scaling* for a detailed description of trade-offs in low-power SAR design.

Copyright © 2017, Texas Instruments Incorporated

#### **Specifications**

| Specification                        | Calculated          | Simulated | Measured |

|--------------------------------------|---------------------|-----------|----------|

| Transient ADC Input Settling (1ksps) | < 0.5 × LSB = 402µV | 41.6µV    | N/A      |

| AVDD Supply Current (1ksps)          | 230nA               | N/A       | 214.8nA  |

| AVDD Supply Power (1ksps)            | 759nW               | N/A       | 709nW    |

| VDD OPAMP Supply Current             | 450nA               | N/A       | 431.6nA  |

| VDD OPAMP Supply Power               | 2.025µW             | N/A       | 1.942µW  |

| AVDD + VDD System Power (1ksps)      | 2.784µW             | N/A       | 2.651µW  |

#### **Design Notes**

- 1. Determine the linear range of the op amp based on common mode, output swing, and linear open loop gain specification. This is covered in the component selection section.

- 2. Select a COG (NPO) capacitor for Cfilt to minimize distortion.

- 3. The *TI Precision Labs ADCs* training video series covers methods for selecting the charge bucket circuit Rfilt and Cfilt (see *Introduction to SAR ADC Front-End Component Selection*). These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here will give good settling and AC performance for the amplifier and data converter in this example. If you modify the design you will need to select a different RC filter.

#### www.ti.com

#### **Component Selection**

- 1. Select a low-power op amp:

- Supply current < 0.5μA</li>

- Gain bandwidth product > 5kHz (5 times the sampling rate)

- Unity gain stable

- LPV811 450-nA supply current, 8-kHz gain bandwidth product, unity gain stable

- 2. Find op amp maximum and minimum output for linear operation:

$$V_{ee} + 0V < V_{out} < V_{dd} - 0.9V \quad \text{from LPV811} \quad V_{cm} \quad \text{specification}$$

$$V_{ee} + 10 mV < V_{out} < V_{dd} - 10 mV \quad from \quad LPV811 \quad Vout \quad swing \quad specification$$

$$V_{ee} + 0.3V < V_{out} < V_{dd} - 0.3V$$

from LPV811 AoI linear region specification

3. Typical power calculations (at 1ksps) with expected values. See *SAR ADC Power Scaling* for a detailed description of trade-offs in low-power SAR design:

$$P_{AVDD} = I_{AVDD\_AVG} \times AVDD = 230nA \times 3.3V = 759nW$$

$$P_{LPV811} = I_{LPV811} \times (V_{dd} - V_{ee}) = 450 \text{nA} \times (4.5 V - (-0.3 V)) = 2.16 \mu W$$

$$P_{total} \!=\! P_{AVDD} \!+\! P_{LPV811} \!=\! 759 nW + 2.16 \mu W \!=\! 2.919 \mu W$$

4. Typical power calculations (at 1ksps) with measured values:

$$P_{AVDD} = I_{AVDD} AVG \times AVDD = 214.8nA \times 3.3V = 708.8nW$$

$$P_{LPV811} = I_{LPV811} \times (V_{dd} - V_{ee}) = 431.6 nA \times (4.5 V - (-0.3 V)) = 2.071 \mu W$$

$$P_{total} = P_{AVDD} + P_{LPV811} = 708.8 nW + 2.071 \mu W = 2.780 \mu W$$

5. Find Rfilt and Cfilt to allow for settling at 1ksps. Refer to *Refine the Rfilt and Cfilt Values* (a *Precision Labs* video) for the algorithm to select Rfilt and Cfilt. The final value of 200kΩ and 510pF proved to settle to well below ½ of a least significant bit (LSB).

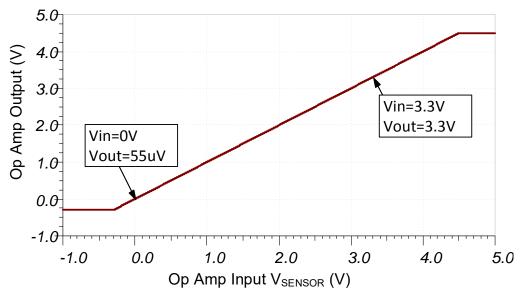

#### **DC Transfer Characteristics**

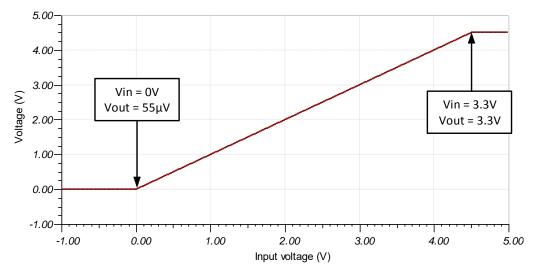

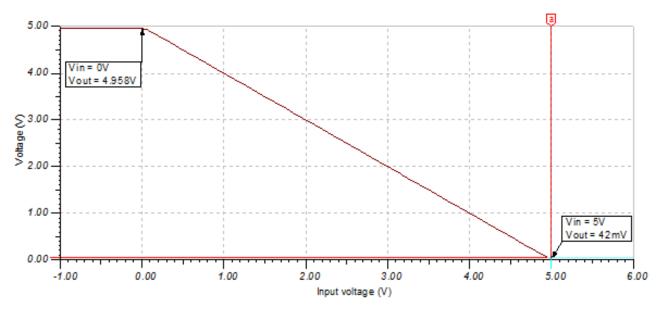

The following graph shows a linear output response for inputs from 0 to 3.3V. The full-scale range (FSR) of the ADC falls within the linear range of the op amp. Refer to *Determining a SAR ADC's Linear Range when using Operational Amplifiers* for detailed theory on this subject.

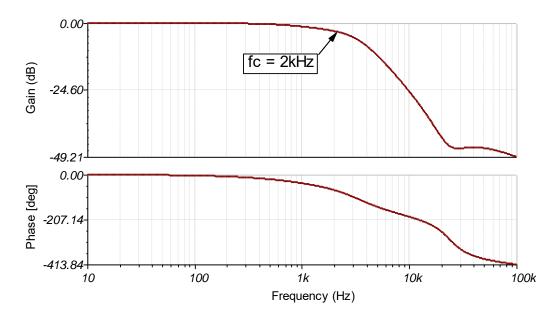

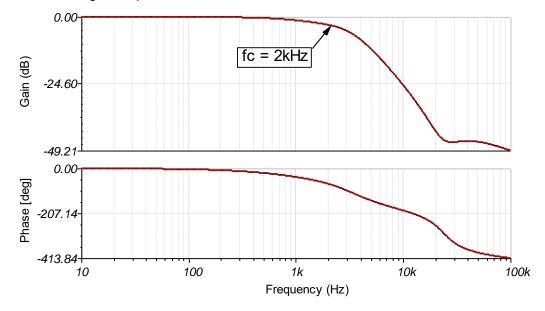

#### **AC Transfer Characteristics**

The bandwidth simulation includes the effects of the amplifier output impedance and the RC charge bucket circuit ( $R_{\rm filt}$ ). The bandwidth of the RC circuit is shown in the following equation to be 1.56kHz. The simulated bandwidth of 2kHz includes effects from the output impedance interacting with the impedance of the load. See *TI Precision Labs - Op Amps: Bandwidth 1* for more details on this subject.

$$f_c = \frac{1}{2 \times \pi \times R_{\text{filt}} \times C_{\text{filt}}} = \frac{1}{2 \times \pi \times (200 \text{k}\Omega) \times (510 \text{pF})} = 1.56 \text{kHz}$$

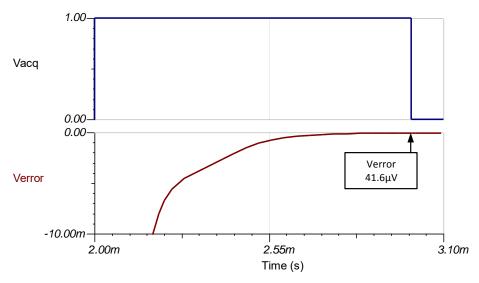

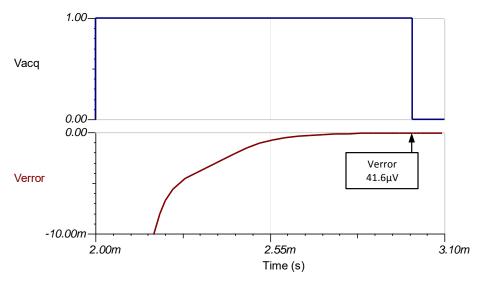

#### **Transient ADC Input Settling Simulation**

The following simulation shows settling to a 3-V DC input signal. This type of simulation shows that the sample and hold kickback circuit is properly selected to within ½ of an LSB (402µV). Refer to *Introduction to SAR ADC Front-End Component Selection* for detailed theory on this subject.

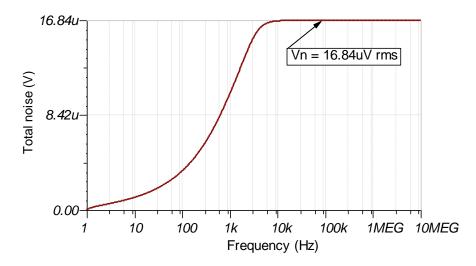

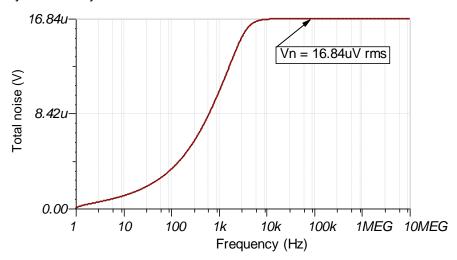

#### **Noise Simulation**

This section walks through a simplified noise calculation for a rough estimate. We neglect resistor noise in this calculation as it is attenuated for frequencies greater than 10kHz.

$$\begin{split} f_{\text{C}} &= \frac{1}{2 \times \pi \times \mathsf{R}_{\text{filt}} \times \mathsf{C}_{\text{filt}}} = \frac{1}{2 \times \pi \times 200 \text{k}\Omega \times 510 \text{pF}} = 1560 \text{Hz} \\ \mathsf{E}_{\text{n}} &= \mathsf{e}_{\text{n}811} \times \sqrt{\mathsf{K}_{\text{n}} \times f_{\text{C}}} = \frac{340 \text{nV}}{\sqrt{\text{Hz}}} \times \sqrt{1.57 \times 1560 \text{Hz}} = 16.8 \mu \text{V} \end{split}$$

Note that the calculated and simulated values match well. Refer to *Calculating the Total Noise for ADC Systems* for detailed theory on this subject.

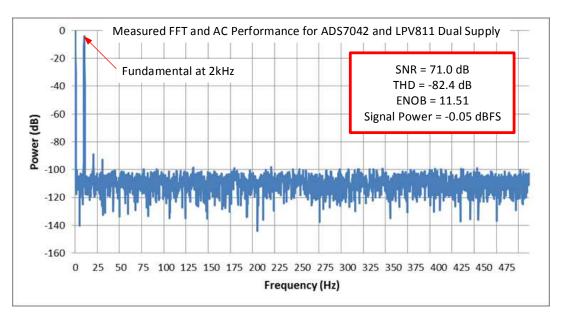

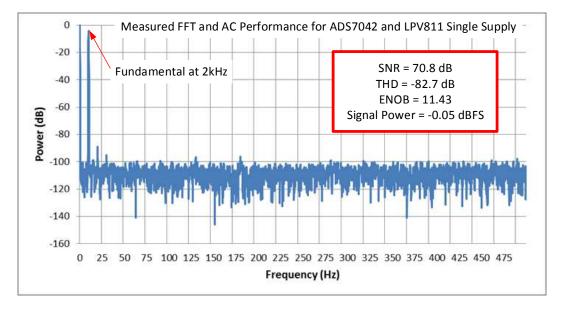

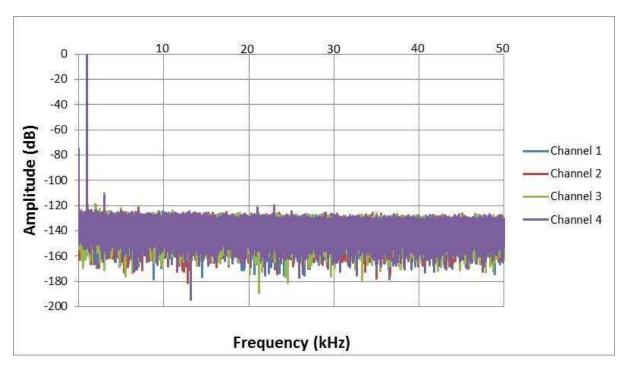

#### **Measure FFT**

This performance was measured on a modified version of the ADS7042EVM with a 10-Hz input sine wave. The AC performance indicates SNR = 71.0dB, THD = -82.4dB, and ENOB (effective number of bits) = 11.51, which matches well with the specified performance of the ADC, SNR = 70dB and THD = -80dB. This test was performed at room temperature. See *Introduction to Frequency Domain* for more details on this subject.

#### **Design Featured Devices**

| Device                 | Key Features                                                                                               | Link                              | Other Possible Devices   |

|------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|

| ADS7042 <sup>(1)</sup> | 12-bit resolution, SPI, 1-Msps sample rate, single-ended input, AVDD reference input range 1.6 V to 3.6 V. | http://www.ti.com/product/ADS7042 | Links to similar devices |

| LPV811 <sup>(2)</sup>  | 8-kHz bandwidth, rail-to-rail output, 450-nA supply current, unity gain stable                             | http://www.ti.com/product/LPV811  | Links to similar devices |

<sup>(1)</sup> The ADS7042 uses the AVDD as the reference input. A high-PSRR LDO, such as the TPS7A47, should be used as the power supply.

#### Link to Key Files (TINA)

Design files for this circuit - http://www.ti.com/lit/zip/sbam342

#### For direct support from TI Engineers use the E2E community:

http://e2e.ti.com/

#### TI Precision Labs Training Series community:

TI Precision Labs - https://training.ti.com/ti-precision-labs-overview

#### Other Links

www.ti.com/adcs

www.ti.com/opamp

<sup>(2)</sup> The LPV811 is also commonly used in low-speed applications for sensors. Furthermore, the rail-to-rail output allows for linear swing across the entire ADC input range.

SBAA253-February 2018

### Low-Power Sensor Measurements: 3.3V, 1ksps, 12-bit Single-Ended, Single Supply

#### Reed Kaczmarek

| Input         | ADC Input                | Digital Output ADS7042                 |

|---------------|--------------------------|----------------------------------------|

| VinMin = 0 V  | AIN_P = 0V, AIN_M = 0V   | 000 <sub>H</sub> or 0 <sub>10</sub>    |

| VinMax = 3.3V | AIN_P = 3.3V, AIN_M = 0V | FFF <sub>H</sub> or 4096 <sub>10</sub> |

| Power Supplies |    |      |

|----------------|----|------|

| AVDD Vee Vdd   |    |      |

| 3.3V           | 0V | 4.5V |

#### **Design Description**

This design shows an ultra-low power amplifier being used to drive a SAR ADC that consumes only nanoWatts of power during operation. This design is intended for collecting sensor data by providing overall system-level power consumption on the order of single-digit microWatts. *PIR sensors*, *gas sensors*, and *glucose monitors* are a few examples of possible implementations of this SAR ADC design. The values in the *component selection* section can be adjusted to allow for different data throughput rates and different bandwidth amplifiers. *Low-Power Sensor Measurements: 3.3V, 1ksps, 12-bit Single-Ended, Dual Supply* shows a more sophisticated version of this circuit where the negative supply is connected to a small negative voltage (–0.3V). The single-supply version has degraded performance when the amplifier output is near zero volts. However, in most cases the single-supply configuration is preferred for its simplicity.

Copyright © 2018, Texas Instruments Incorporated

#### **Specifications**

| Specification                        | Calculated        | Simulated | Measured |

|--------------------------------------|-------------------|-----------|----------|

| Transient ADC Input Settling (1ksps) | < 0.5·LSB = 402µV | 41.6µV    | N/A      |

| AVDD Supply Current (1ksps)          | 230nA             | N/A       | 214.8nA  |

| AVDD Supply Power (1ksps)            | 759nW             | N/A       | 709nW    |

| VDD OPAMP Supply Current             | 450nA             | N/A       | 431.6nA  |

| VDD OPAMP Supply Power               | 2.025µW           | N/A       | 1.942µW  |

| AVDD + VDD System Power (1ksps)      | 2.784µW           | N/A       | 2.651µW  |

#### **Design Notes**

- 1. Determine the linear range of the op amp based on common mode, output swing, and linear open loop gain specification. This is covered in the *component selection* section.

- 2. Select COG capacitors to minimize distortion.

- 3. Use 0.1% 20ppm/°C film resistors or better to minimize distortion.

- 4. The TI Precision Labs ADCs training video series covers methods for selecting the charge bucket circuit Rfilt and Cfilt. These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here will give good settling and AC performance for the amplifier and data converter in this example. If you modify this design you will need to select a different RC filter. Refer to the Introduction to SAR ADC Front-End Component Selection training video for an explanation of how to select the RC filter for best settling and AC performance.

www.ti.com

#### **Component Selection**

- 1. Select a low-power operational amp:

- Supply current < 0.5µA</li>

- Gain bandwidth product > 5kHz (5 times the sampling rate)

- Unity gain stable

- For this cookbook, the LPV811 was selected. It has a 450-nA supply current, 8-kHz gain bandwidth product, and is unity gain stable.

- 2. Find op amp maximum and minimum output for linear operation

$$\label{eq:Vee+0V} \begin{split} V_{ee} + 0V < V_{out} < V_{dd} - 0.9V & \text{ from LPV811 Vcm specification} \\ V_{ee} + 10\text{mV} < V_{out} < V_{dd} - 10\text{mV} & \text{ from LPV811 Vout swing specification} \\ V_{ee} + 0.3V < V_{out} < V_{dd} - 0.3V & \text{ from LPV811 AoI linear region specification} \end{split}$$

$0.3V < V_{in} < 3.4V$  Combined worst case

NOTE: The linear range of the LPV811 is 300mV above ground. This means to design a system to guarantee a full linear range from 0V to 3.3V (full-scale range (FSR) of ADS7042), then a negative supply is required. This design shows that full-measured SNR and THD specifications of the ADS7042 are met without using a negative supply voltage. This testing was only at room temperature and for a more robust system; Low-Power Sensor Measurements: 3.3V, 1ksps, 12-bit Single-Ended, Dual Supply shows this design using a negative supply instead of ground.

3. Typical power calculations (at 1ksps) with expected values:

$$\begin{split} P_{AVDD} = I_{AVDD\_Avg} \cdot AVDD = 230 nA \cdot 3.3V = 759 nW \\ P_{LPV811} = I_{LPV811} \cdot (V_{dd} - V_{ee}) = 450 nA \cdot (4.5V - 0V) = 2.025 \mu W \\ P_{total} = P_{AVDD} + P_{LPV811} = 759 nW + 2.025 \mu W = 2.794 \mu W \end{split}$$

4. Typical power calculations (at 1ksps) with measured values:

$$\begin{split} P_{AVDD} = I_{AVDD\_Avg} \cdot AVDD = 214nA \cdot 3.3V = 709nW \\ P_{LPV811} = I_{LPV811} \cdot (V_{dd} - V_{ee}) = 431.6nA \cdot (4.5V - 0V) = 1.942\mu W \\ P_{total} = P_{AVDD} + P_{LPV811} = 709nW + 1.942\mu W = 2.651\mu W \end{split}$$

5. Find Rfilt and Cfilt to allow for settling at 1ksps. Refine the Rfilt and Cfilt Values (a Precision Labs video) showing the algorithm for selecting Rfilt and Cfilt. The final value of  $200 \text{k}\Omega$  and 510 pF proved to settle to well below ½ of a least significant bit (LSB).

#### **DC Transfer Characteristics**

The following graph shows a linear output response for inputs from 0 to 3.3V. The FSR of the ADC falls within the linear range of the op amp.

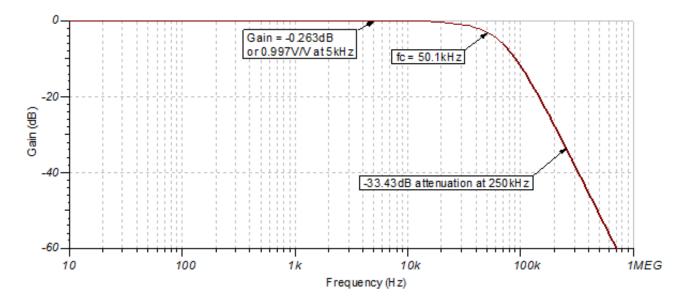

#### **AC Transfer Characteristics**

The bandwidth is simulated to be 7.02kHz at the gain of 0dB which is a linear gain of 1. This bandwidth will allow for settling at 1ksps.

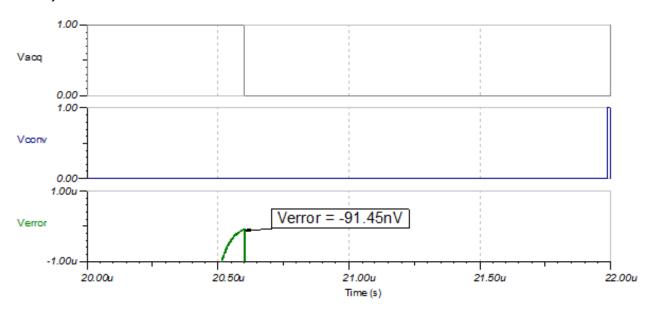

#### **Transient ADC Input Settling Simulation**

The following simulation shows settling to a 3-V DC input signal. This type of simulation shows that the sample and hold kickback circuit is properly selected to within ½ of a LSB (402µV). Refer to *Introduction to SAR ADC Front-End Component Selection* for detailed theory on this subject.

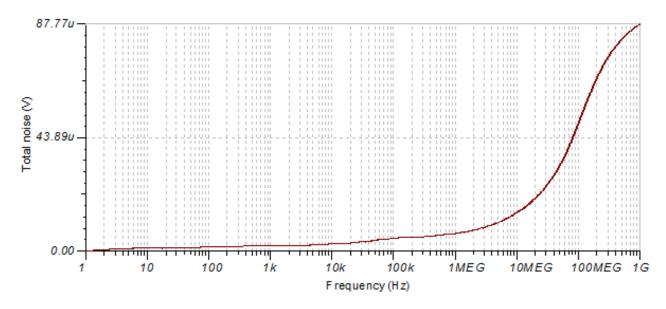

#### **Noise Simulation**

This section details a simplified noise calculation for a rough estimate. We neglect resistor noise in this calculation as it is attenuated for frequencies greater than 10kHz.

$$\begin{split} f_C &= \frac{1}{2 \cdot \pi \cdot R_{filt} \cdot C_{filt}} = \frac{1}{2 \cdot \pi \cdot (200 k\Omega) \cdot (510 pF)} = 1560 \text{ . 3Hz} \\ E_n &= e_{n811} \cdot \sqrt{2 \cdot K_n \cdot f_C} = (340 nV \ / \sqrt{Hz}) \cdot \sqrt{1.57 \cdot (1560 Hz)} = 16 \text{ . 8} \mu V \end{split}$$

Note that calculated and simulated match well. Refer to *Calculating the Total Noise for ADC Systems* for detailed theory on this subject.

#### **Measure FFT**

This performance was measured on a modified version of the ADS7042EVM-PDK. The AC performance indicates SNR = 70.8dB, THD = -82.7dB, and ENOB (effective number of bits) = 11.43, which matches well with the specified performance of the ADC of SNR = 70dB.

#### www.ti.com

#### **Design Featured Devices**

| Device                 | Key Features                                                                                           | Link                              | Other Possible Devices   |

|------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|

| ADS7042 <sup>(1)</sup> | 12-bit resolution, SPI, 1-Msps sample rate, single-ended input, AVDD, Vref input range 1.6 V to 3.6 V. | http://www.ti.com/product/ADS7042 | Links to similar devices |

| LPV811 <sup>(2)</sup>  | 8 kHz bandwidth, Rail-to-Rail output, 450 nA supply current, unity gain stable                         | http://www.ti.com/product/LPV811  | http://www.ti.com/opamps |

The ADS7042 uses the AVDD as the reference input. A high-PSRR LDO, such as the TPS7A47, should be used as the power supply.

#### Link to Key Files

Tina Files for Low Power Sensor Measurements - http://www.ti.com/lit/zip/sbam341

For direct support from TI Engineers use the E2E community:

e2e.ti.com

Other Links

www.ti.com/adcs

<sup>(2)</sup> The LPV811 is also commonly used in low speed applications for sensors. Furthermore, the rail-to-rail output allows for linear swing across all of the ADC input range.

SBAA242-December 2017

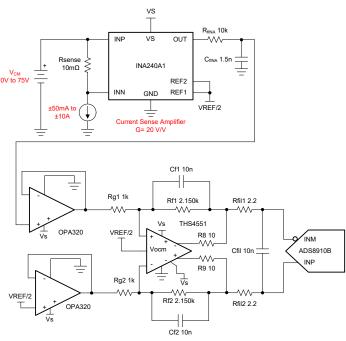

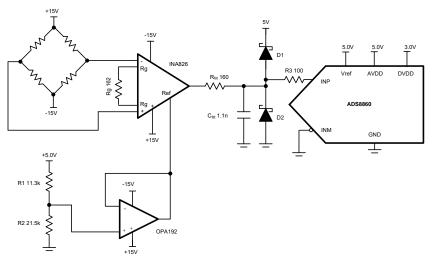

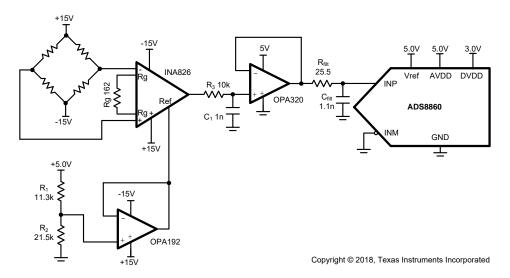

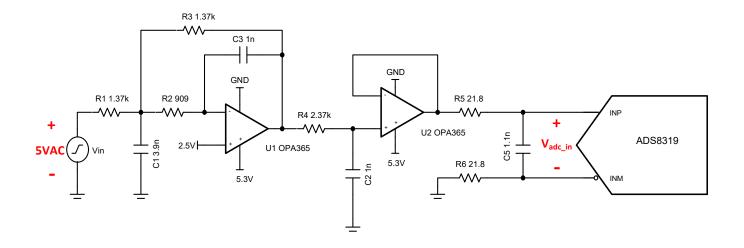

### High-Voltage Battery Monitor Circuit: ±20 V, 0-10 kHz, 18-Bit Fully Differential

Bryan McKay, Arthur Kay

| Input         | ADC Inp                   | ut                                                            | Digital Output ADS8910                        |  |  |

|---------------|---------------------------|---------------------------------------------------------------|-----------------------------------------------|--|--|

| VinMin = –20V | VoutDif = 4.8V, VoutP = 4 | I.9V, VoutN = 0.1V 1EB85 <sub>H</sub> or 125829 <sub>10</sub> |                                               |  |  |

| VinMax = 20V  | VoutDif = -4.8V, VoutP =  | 0.1V, VoutN = 4.9V                                            | V 2147B <sub>H</sub> or –125829 <sub>10</sub> |  |  |

|               | Power Supplies            |                                                               |                                               |  |  |

| Vcc           | Vee                       | Vref                                                          | Vcm                                           |  |  |

| 5.3 V         | 0 V                       | 5 V                                                           | 2.5 V                                         |  |  |

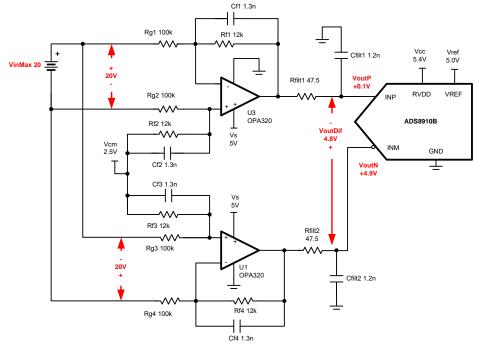

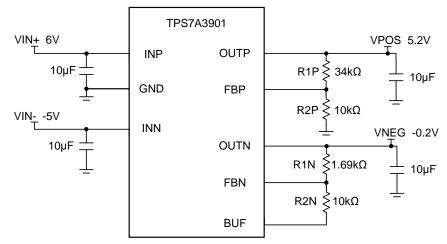

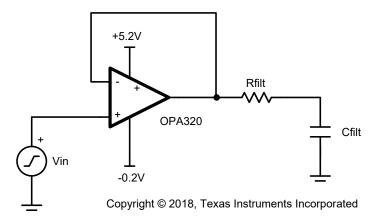

#### **Design Description**

This design translates an input bipolar signal of ±20V into a fully differential ADC differential input scale of ±4.8V, which is within the output linear operation of amplifiers. The values in the component selection section can be adjusted to allow for different input voltage levels.

This circuit implementation is applicable in accurate voltage measurement applications such as Battery Maintenance Systems, Battery Analyzers, Battery Testing Equipment, ATE, and Remote Radio Units (RRU) in wireless base stations.

Copyright © 2017, Texas Instruments Incorporated

#### **Specifications**

| Specification                | Calculated       | Simulated   | Measured   |

|------------------------------|------------------|-------------|------------|

| Transient ADC Input Settling | < 0.5LSB or 19µV | 6.6µV       | N/A        |

| Noise                        | 20.7µV rms       | 20.65μV rms | 30.8μV rms |

| Bandwidth                    | 10.2kHz          | 10.4kHz     | 10.4kHz    |

#### **Design Notes**

- 1. Determine the linear range of the op amp based on common mode, output swing, and linear open-loop gain specification. This is covered in the *component selection* section.

- 2. For capacitors in the signal path, select COG type to minimize distortion. In this circuit Cf1, Cf2, Cf3, Cf4, Cfilt1, and Cfilt2 need to be COG type.

- 3. Use 0.1% 20ppm/°C film resistors or better for good gain drift and to minimize distortion.

- 4. Precision labs video series covers methods for error analysis. Review the *Statistics Behind Error Analysis* for methods to minimize gain, offset, drift, and noise errors.

- 5. The *TI Precision Labs ADCs* training video series covers methods for selecting the charge bucket circuit R<sub>filt</sub> and C<sub>filt</sub>. These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here will give good settling and AC performance for the amplifier, gain settings, and data converter in this example. If the design is modified, select a different RC filter. Refer to *Introduction to SAR ADC Front-End Component Selection* for an explanation of how to select the RC filter for best settling and AC performance.

#### **Component Selection**

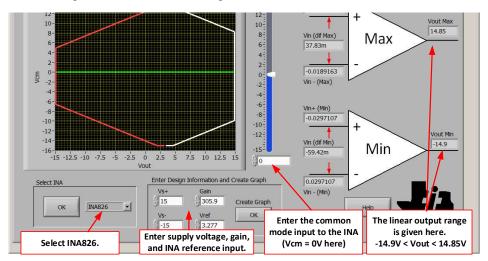

1. The general equation for this circuit.

$$V_{outMinOpa} = \frac{V_{outDifMin}}{2} + V_{cm}$$

$$V_{outMaxOpa} = \frac{V_{outDifMax}}{2} + V_{cm}$$

$$Gain_{dif} = 2 \times \frac{R_f}{R_g}$$

2. Find op amp maximum and minimum output for linear operation.

$$-0.1\,V < V_{cm} < 5.1V$$

from OPA320 Vcm specification

$$0.035 \, V < V_{out} < 4.965 \, V$$

from OPA320 Vout swing specification

$$0.1 \, \text{V} < \text{V}_{\text{out}} < 4.9 \, \text{V}$$

Combined worst case

3. Rearrange the equation from part 1 and solve for VoutDifMin and VoutDifMax. Find maximum and minimum differential output voltage based on combined worst case from step 2.

$$V_{outDifMax} = 2 \cdot V_{outMaxOpa} - 2 \cdot V_{cm} = 2 \cdot (4.9 \text{ V}) - 2 \cdot (2.5 \text{ V}) = 4.8 \text{ V}$$

$$V_{outDifMax} = 2 \cdot V_{outMinOpa} - 2 \cdot V_{cm} = 2 \cdot (0.1 \text{ V}) - 2 \cdot (2.5 \text{ V}) = -4.8 \text{ V}$$

4. Find differential gain based on results from step 3.

$$Gain = \frac{V_{outDifMax} - V_{outDifMin}}{V_{inDifMax} - V_{inDifMin}} = \frac{(4.8 \text{ V}) - (-4.8 \text{ V})}{(20 \text{ V}) - (-20 \text{ V})} = 0.24$$

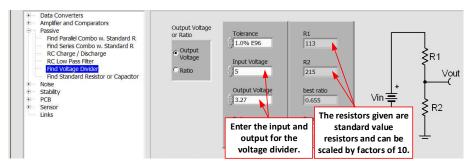

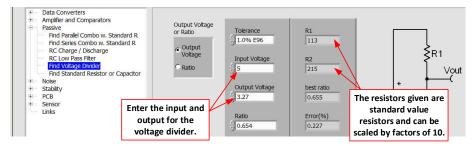

5. Find standard resistor values for differential gain. Use *Analog Engineer's Calculator* ("Amplifier and Comparator\Find Amplifier Gain" section) to find standard values for Rf/Rg ratio.

$$\frac{\textit{Gain}_{dif}}{2} = \frac{\textit{R}_{f}}{\textit{R}_{Q}} = \frac{0.24}{2} = 0.12$$

$$\frac{R_f}{R_g} = 0.12 = \frac{12 \text{ k}\Omega}{100 \text{ k}\Omega} = 0.12$$

6. Find Cf for cutoff frequency.

$$f = \frac{1}{2 \cdot \pi \cdot C_f \cdot R_f} = \frac{1}{2 \cdot \pi \cdot (1.3nF) \cdot (12k\Omega)} = 10.2 \text{ kHz}$$

$$C_f = \frac{1}{2 \cdot \pi \cdot f_c \cdot R_f} = \frac{1}{2 \cdot \pi \cdot (10 \text{ kHz}) \cdot (12 \text{ k}\Omega)} = 1.326 \quad \text{nF or 1.3 nF for standard value}$$

$$f = \frac{1}{2 \cdot \pi \cdot C_f \cdot R_f} = \frac{1}{2 \cdot \pi \cdot (1.3 \, nF) \cdot (12 k\Omega)} = 10 \cdot 2kHz$$

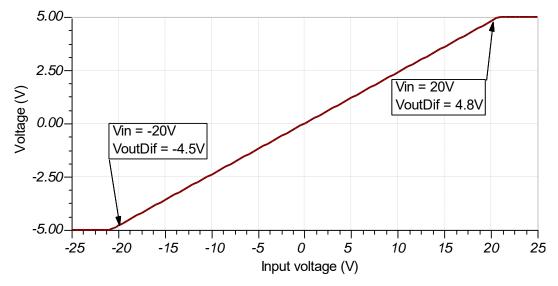

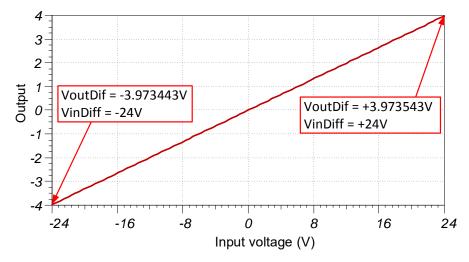

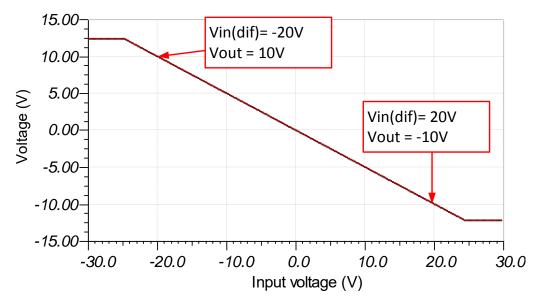

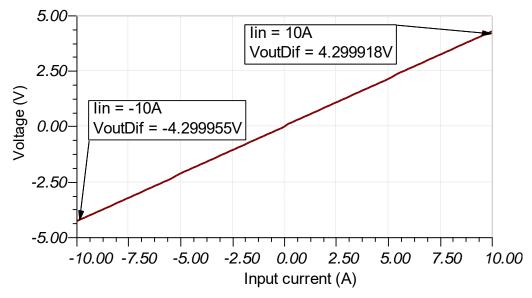

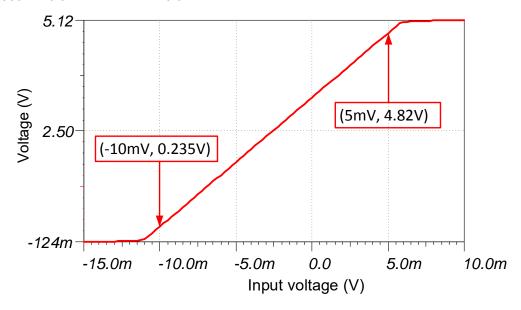

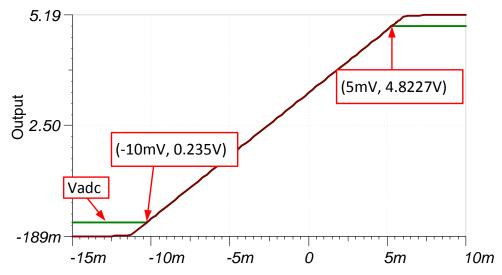

#### **DC Transfer Characteristics**

The following graph shows a linear output response for inputs from –20V to +20V. Refer to *Determining a SAR ADC's Linear Range when using Operational Amplifiers* for detailed theory on this subject.

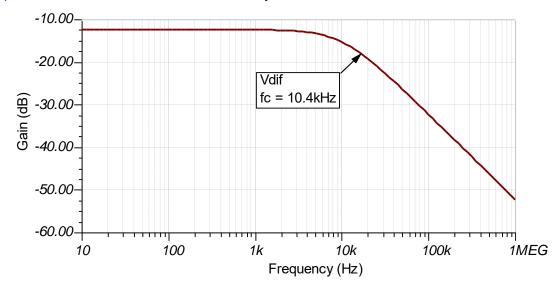

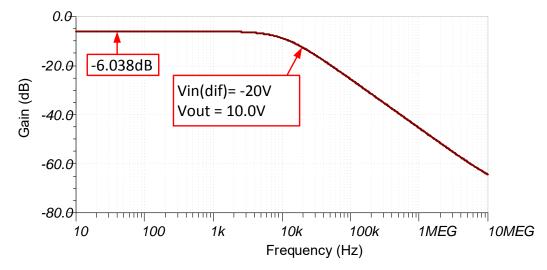

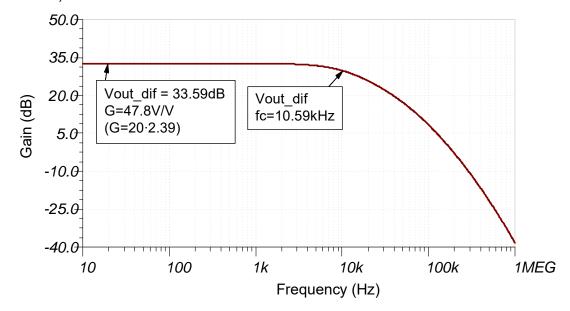

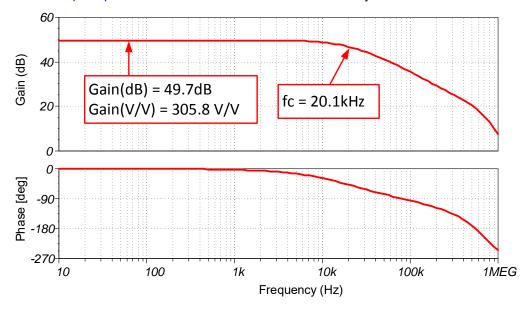

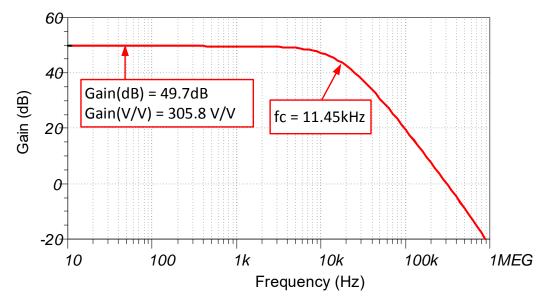

#### **AC Transfer Characteristics**

The bandwidth is simulated to be 10.4 kHz, and the gain is –12.4dB which is a linear gain of 0.12. See *Op Amps: Bandwidth 1* for more details on this subject.

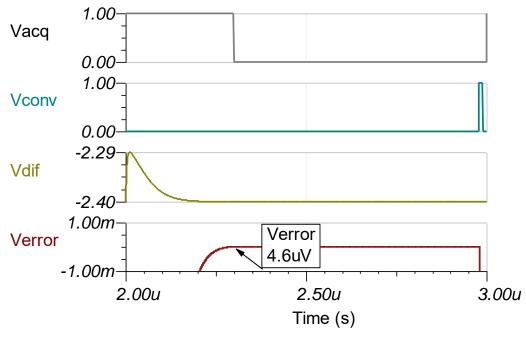

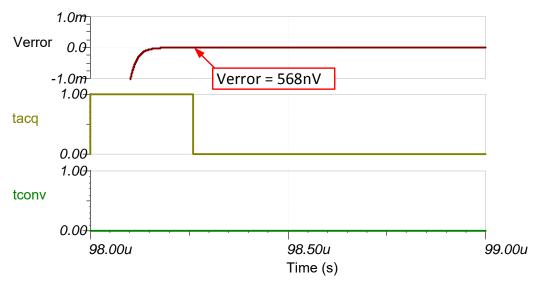

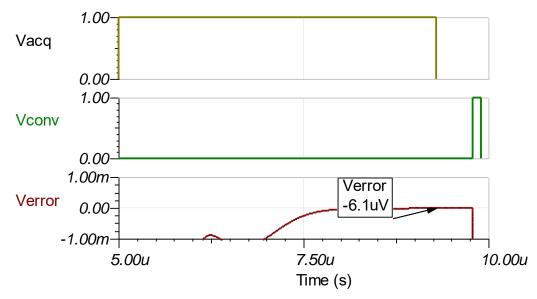

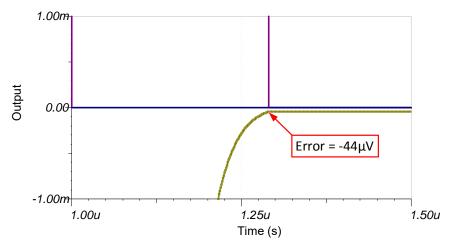

#### **Transient ADC Input Settling Simulation**

The following simulation shows settling to a –20V dc input signal. This type of simulation shows that the sample and hold kickback circuit is properly selected. Refer to *Introduction to SAR ADC Front-End Component Selection* for detailed theory on this subject.

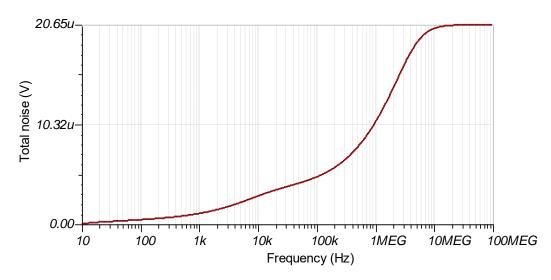

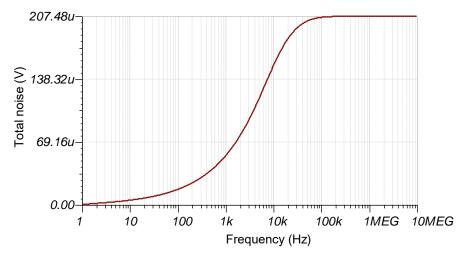

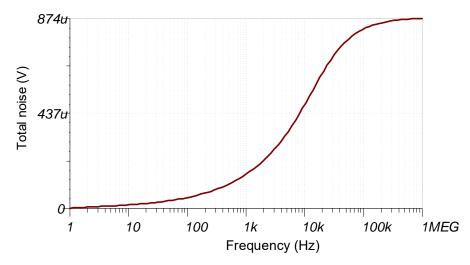

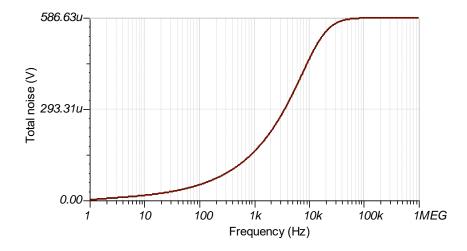

#### **Noise Simulation**

The following simplified noise calculation is provided for a rough estimate. We neglect resistor noise in this calculation as it is attenuated for frequencies greater than 10kHz.

$$\begin{split} f_C &= \frac{1}{2 \cdot \pi \cdot R_{filt} \cdot C_{filt}} = \frac{1}{2 \cdot \pi \cdot (47.5\Omega) \cdot (1.2nF)} = 2.8 MHz \\ E_{n\_se} &= e_{n320} \cdot \sqrt{K_n \cdot f_c} = (7nV \ / \ \sqrt{Hz} \ ) \cdot \sqrt{\left(1.57\right) \cdot \left(2.8 MHz\right)} = 14.7 \mu V rms \quad \text{for a single ended input} \\ E_{n\_tot} &= \sqrt{E_{n\_se}^2 + E_{n\_se}^2} = \sqrt{\left(14.7 \mu V\right)^2 + \left(14.7 \mu V\right)^2} = 20.7 \mu V \quad rms \quad \text{Total noise for differential amplifier} \end{split}$$

Note that calculated and simulated match well. Refer to *Calculating the Total Noise for ADC Systems* for detailed theory on this subject.

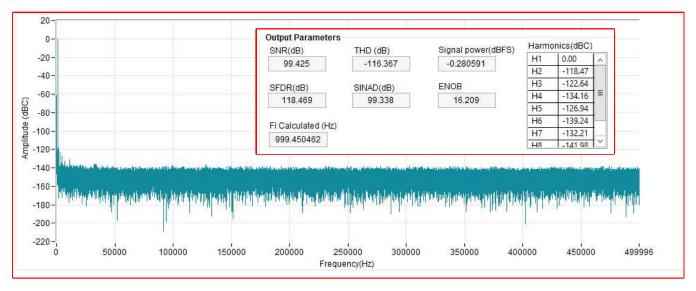

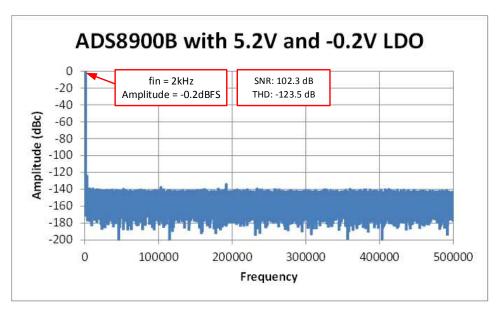

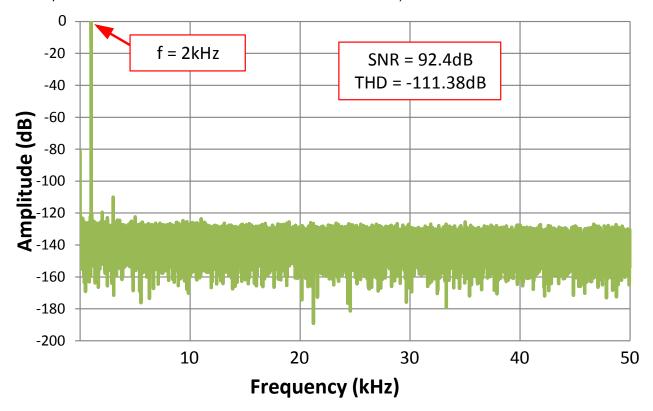

#### **Measure FFT**

This performance was measured on a modified version of the ADS8910BEVM. The AC performance indicates SNR = 99.4dB, and THD = -116.4dB. See *Introduction to Frequency Domain* for more details on this subject.

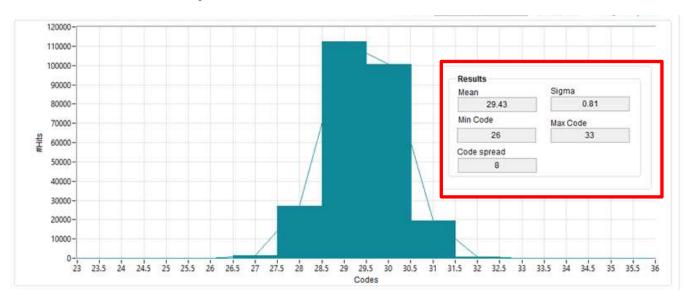

#### **Noise Measurement**

The following measured result is for both inputs connected to ground. The histogram shows the system offset and noise. The standard deviation in codes is given by the EVM GUI (0.81), and this can be used to calculate the RMS noise ( $30.9\mu V$  rms) as shown in the following equation.

$$LSB = \frac{FSR}{2^N} = \frac{10~V}{2^{18}} = 38.14 \mu V$$

$$E_{n\_measured} = E_{nSigma} \cdot LSB = (0.81) \cdot (34.14 \quad \mu V) = 30.9 \mu Vrms$$

#### **Design Featured Devices**

| Device                | Key Features                                                                                                                        | Link                               | Other Possible Devices   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------|

| ADS8910B (1)          | 18-bit resolution, 1-Msps sample rate, Integrated reference buffer, fully differential input, Vref input range 2.5V to 5V.          | http://www.ti.com/product/ADS8900B | Parametric Search        |

| OPA320 <sup>(2)</sup> | 20-MHz bandwidth, Rail-to-Rail with Zero Crossover Distortion, VosMax = 150 $\mu$ V, VosDriftMax = 5 $\mu$ V, C, en = 7 $\mu$ V/rHz | http://www.ti.com/product/OPA320   | http://www.ti.com/opamps |

| REF5050 (3)           | 3 ppm/°C drift, 0.05% initial accuracy, 4µVpp/V noise                                                                               | http://www.ti.com/product/REF5050  | http://www.ti.com/vref   |

<sup>(1)</sup> The REF5050 can be directly connected to the ADS8910B without any buffer because the ADS8910B has a built in internal reference buffer. Also, the REF5050 has the required low noise and drift for precision SAR ADC applications. The OPA320 is also commonly used in 1Msps SAR applications as it has sufficient bandwidth to settle to charge kickback transients from the ADC input sampling. Furthermore, the zero crossover distortion rail-to-rail input allows for linear swing across most of the ADC input range.

#### Link to Key Files for High Voltage Battery Monitor

Design files for this circuit (http://www.ti.com/lit/zip/sbac171)

#### For direct support from TI Engineers use the E2E community:

e2e.ti.com/

Other Links

www.ti.com/adcs

www.ti.com/precisionadc

<sup>(2)</sup> The REF5050 can be directly connected to the ADS8910B without any buffer because the ADS8910B has a built in internal reference buffer. Also, the REF5050 has the required low noise and drift for precision SAR ADC applications. The OPA320 is also commonly used in 1Msps SAR applications as it has sufficient bandwidth.

<sup>(3)</sup> The REF5050 can be directly connected to the ADS8910B without any buffer because the ADS8910B has a built in internal reference buffer. Also, the REF5050 has the required low noise and drift for precision SAR ADC applications. The OPA320 is also commonly used in 1Msps SAR applications as it has sufficient bandwidth.

#### SBAA246-January 2018

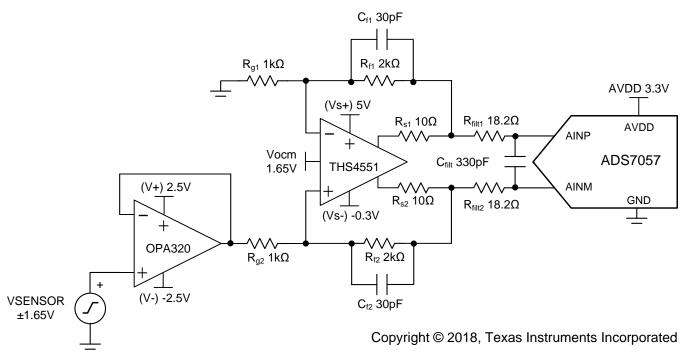

## Single-Ended-to-Differential Circuit Using an Op Amp and Fully Differential Amplifier (FDA) for Bipolar Signals

Evan Sawyer

| Input                       | ADC Input                | Digital Output ADS7057                  |

|-----------------------------|--------------------------|-----------------------------------------|

| V <sub>in</sub> Min = -3.3V | AINP = 0V<br>AINM = 3.3V | 2000 <sub>H</sub><br>8192 <sub>10</sub> |

| V <sub>in</sub> Max = 3.3V  | AINP = 3.3V<br>AINM = 0V | 1FFF <sub>H</sub><br>8191 <sub>10</sub> |

| Power Supplies |    |      |  |

|----------------|----|------|--|

| AVDD GND DVDD  |    |      |  |

| 3.3V           | 0V | 1.8V |  |

#### **Design Description**

This design is intended to demonstrate how to convert a bipolar, single-ended signal into a unipolar, fully-differential signal and drive a differential ADC (for more information on these and other signal types, please refer to the *TI Precision Labs* training titled *SAR ADC Input Types*). Compared to a single-ended device, a fully-differential ADC has twice the dynamic range which improves the AC performance of the converter. Many common systems, for example *Sonar Receivers*, *Flow Meters*, and *Motor Controls*, benefit from the higher performance of a differential ADC. The equations and explanation of component selection in this design can be customized based on system specifications and needs. For more information on a similar design using a unipolar input signal, see the cookbook circuit titled *Single-Ended to Differential Signal Conversion for Unipolar Inputs*.

#### **Specifications**

| Specification                             | Calculated                 | Simulated    |

|-------------------------------------------|----------------------------|--------------|

| Transient ADC Input Settling (at 250ksps) | < 0.5 · LSB = 201µV        | 134.7μV      |

| Conditioned Signal Range (at 250ksps)     | > 99% ADC FSR = ><br>6.53V | 6.60V        |

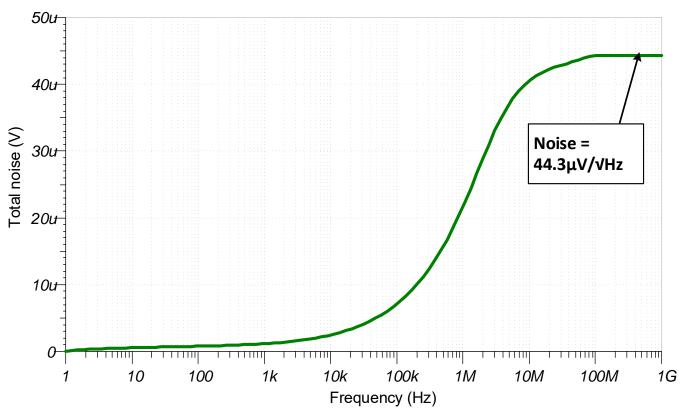

| Noise                                     | 43.8µV / √Hz               | 44.3µV / √Hz |

#### **Design Notes**

- 1. The ADS7057 was selected because of its throughput (2.5Msps), size (2.25mm²) and low-latency (successive approximation register, or SAR, architecture).

- 2. Determine the linear range of the fully-differential amplifier (ADC driver) based on common mode, output swing, and linear open-loop gain specification. This is covered in the component selection section.

- 3. Determine the linear range of the op amp (signal conditioning) based on common mode, output swing, and linear open-loop gain specification. This is covered in the component selection section.

- 4. Select COG (NPO) capacitors for C<sub>filt</sub>, to minimize distortion.

- 5. For best performance, consider using a 0.1% 20ppm/°C film resistor, or better, to minimize distortion.

- 6. The TI Precision Labs ADCs training video series covers methods for selecting the charge bucket circuit R<sub>filtx</sub> and C<sub>filt</sub>. These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here will give good settling and AC performance for the amplifier and data converter in this example. If the design is modified, a different RC filter must be selected. Refer to Introduction to SAR ADC Front-end Component Selection (a TI Precision Labs training video) for an explanation of how to select the RC filter for best settling and AC performance.

#### **Component Selection**

- 1. Select a fully-differential amplifier capable of driving the ADC: THS4551 – Low noise, precision, 150MHz, fully-differential amplifier

- Wide input common-mode voltage:

$$V_{s-} - 0.1 V < V_{cm} < V_{s+} - 1.3 V$$

Linear output (requirement: 0V to 3.3V at each output):

$$V_{s-} + 0.22V < V_{out} < V_{s+} - 0.22V$$

2. Select a wide bandwidth operational amplifier:

OPA320 - Precision, zero-crossover, 20MHz, RRIO, operational amplifier

- Gain bandwidth product > 12.5MHz (> 5 times the sampling rate)

- Input common-mode voltage (requirement: ±1.65V):

$$V_{-} - 0.1V < V_{cm} < V_{+} + 0.1V$$

Linear output:

$$V_{-} + 0.03V < V_{out} < V_{+} - 0.03V$$

$$V_{-} + 0.2V < V_{out} < V_{+} - 0.2V$$

Combined worst-case linear range (calculated from supplies used with OPA320):

$$-2.3V < V_{out} < 2.3V$$

NOTE: The operational amplifier is used to protect the sensor from any charge kickbacks that occur when the ADC connects or disconnects the sampling capacitor. This amplifier may not be needed if the sensor has a high output impedance. A negative rail is used for both the OPA320 and THS4551 based on the assumption that the sensor is operating with a negative rail. This also ensures the highest performance from the ADC by providing the full scale input range.

- 3. Select  $R_{fx}$  and  $R_{ax}$

- The combination of  $R_{fx}$  and  $R_{qx}$  sets the gain of the system. With an input range of  $\pm 1.65 V$  and an ADC full scale of ±3.3V, a gain of 2 was selected for this system.

- The values of  $R_{fx}$  = 2k and  $R_{ax}$  = 1k were selected to both provide the desired gain as well as limit the current through the feedback network, thus minimizing power consumption of the system.

- Select R<sub>sx</sub>

- It is important to connect small resistors at the output of the amplifier, in this case  $10\Omega$ , to flatten the output impedance and improve stability of the system.

- 5. Select R<sub>filtx</sub> and C<sub>filt</sub> values for settling of 250-kHz input signal and sample rate of 2.5Msps:

- Refine the R<sub>filt</sub> and C<sub>filt</sub> Values is a TI Precision Labs video showing the methodology for selecting  $R_{filtx}$  and  $C_{filt}$ . The final value of 18.2 $\Omega$  and 330pF proved to settle to well below  $\frac{1}{2}$  of a least significant bit (LSB) within the acquisition window.

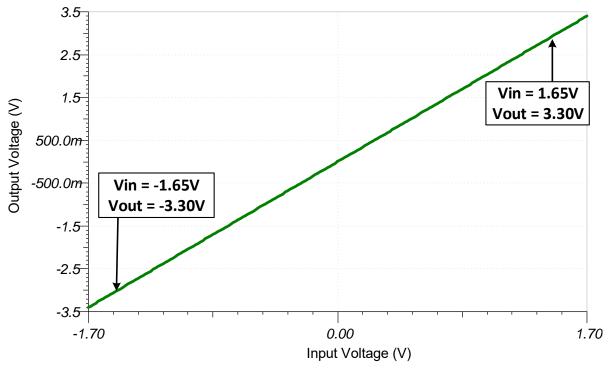

#### **DC Transfer Characteristics**

The following graph shows the simulated output for a ±1.65-V input. The analog front end has a linear output of ±3.3V which matches the full-scale range (FSR) of the ADC (with AVDD = 3.3V).

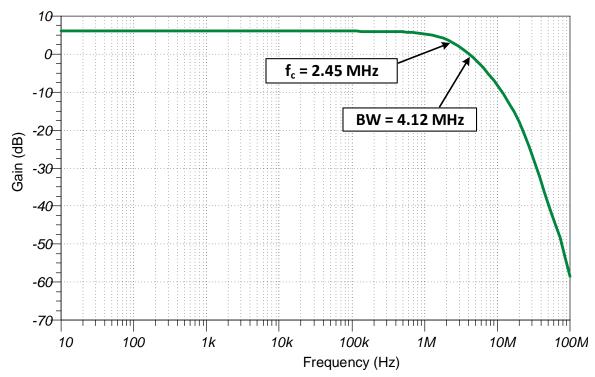

#### **AC Transfer Characteristics**

The bandwidth of the analog front end is simulated to be 4.12MHz at the gain of 0dB which is a linear gain of 1. This bandwidth will allow the inputs of the ADC to adequately settle for a 250-ksps input signal.

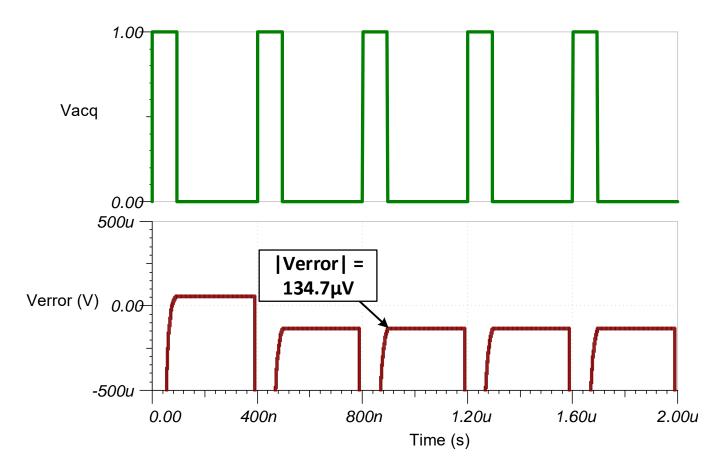

#### **Transient ADC Input Settling Simulation**

The following simulation shows the ADC sample and hold capacitor settling for a 3.3-V DC input signal. This simulation shows that the analog front end is able to drive the ADC with a large step input (from 0V to 3.3V) so it settles to within  $\frac{1}{2}$  of an LSB (approximately 200 $\mu$ V) in the allotted acquisition time (95ns). Refer to Introduction to SAR ADC Front-End Component Selection for detailed theory on this subject, and follow the link at the end of this design to download these simulation files.

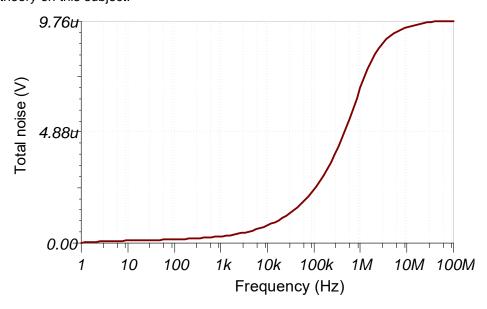

#### **Noise Simulation**

This section walks through a simplified noise calculation, providing a rough estimate to compare with the simulated result. The resistor noise is included in this calculation as it is a significant portion of the overall noise of the system. Note that the resistor noise can be reduced by using smaller value resistors, but at the expense of increased power consumption through the feedback network.

$$\begin{split} & f_c = \frac{1}{2 \times \pi \times R_{filt} \times C_{filt}} = \frac{1}{2 \times \pi \times 2k\Omega \times 30 \, pF} = 2.65 MHz \\ & E_n = e_{OPA320} \times \sqrt{2 \times K_n \times f_c} = \left( 7nV \, / \, \sqrt{Hz} \right) \times \sqrt{2 \times 1.57 \times 2.65 MHz} = 20.2 \, \mu V \, / \, \sqrt{Hz} \\ & E_{n\_OPA320} = E_n \times Gain = 20.2 \, \mu V \, / \, \sqrt{Hz} \times 2 = 40.4 \, \mu V \, / \, \sqrt{Hz} \\ & E_{n\_THS4551} = e_{nTHS4551} \times \sqrt{2 \times K_n \times f_c} = \left( 3.3 nV \, / \, \sqrt{Hz} \right) \times \sqrt{2 \times 1.57 \times 2.65 MHz} = 9.52 \, \mu V \, / \, \sqrt{Hz} \\ & E_{Rg} = \frac{\sqrt{4 \times k \times T \times R_g}}{1 \times 10^{-9}} \times \frac{R_g}{R_g} \times \sqrt{2} = \frac{\sqrt{4 \times 1.38 \times 10^{-23} \times (273.15 + 25) \times 1000}}{1 \times 10^{-9}} \times \sqrt{2} = 11.47 \, \mu V \, / \, \sqrt{Hz} \\ & E_{Rf} = \frac{\sqrt{4 \times k \times T \times R_g}}}{1 \times 10^{-9}} \times \sqrt{2} = \frac{\sqrt{4 \times 1.38 \times 10^{-23} \times (273.15 + 25) \times 2000}}{1 \times 10^{-9}} \times \sqrt{2} = 8.11 \, \mu V \, / \, \sqrt{Hz} \end{split}$$

$$\text{Total noise at output equation:}$$

$$E_{n} = \sqrt{E_{nOPA320}^{2} + E_{n\_THS4551}^{2} + E_{Rg}^{2} + E_{Rf}^{2}} \quad \sqrt{40.4^{2} + 9.52^{2} + 11.47^{2} + 8.11^{2}} \quad 43.8 \mu V / \sqrt{Hz}$$

Note that calculated and simulated match well. Refer to the TI Precision Labs - ADCs training video series for detailed theory on this subject.

#### www.ti.com

#### **Design Featured Devices**

| Device  | Key Features                                                                 | Link                              | Other Possible Devices |

|---------|------------------------------------------------------------------------------|-----------------------------------|------------------------|

| ADS7057 | 14 bit, 2.5 Msps, fully-differential input, SPI, 2.25mm <sup>2</sup> package | http://www.ti.com/product/ADS7057 | Similar Devices        |

| THS4551 | 150MHz, 3.3nV/√Hz input voltage noise, fully-differential amplifier          | http://www.ti.com/product/THS4551 | Similar Devices        |

| OPA320  | Precision, zero-crossover, 20MHz, 0.9pA lb, RRIO, operational amplifier      | http://www.ti.com/product/OPA320  | Similar Devices        |

NOTE: The ADS7057 uses the AVDD as the reference input. A high-PSRR LDO, such as the TPS7A47, should be used as the power supply.

#### Link to Key files (TINA):

Design files for this circuit (http://www.ti.com/lit/zip/sbac181)

#### Link to Related Cookbooks:

Single-Ended to Differential Signal Conversion for Unipolar Input

#### For direct support from TI Engineers use the E2E community:

e2e.ti.com

#### TI Precision Labs Training Series community:

TI Precision Labs - https://training.ti.com/ti-precision-labs-overview

#### Other Links:

www.ti.com/adcs www.ti.com/opamp

# High-Input Impedance, True Differential, Analog Front End (AFE) Attenuator Circuit for SAR ADCs

Luis Chioye

| Input Voltage (OPA197 Buffers)                       | THS4551 Output, ADC Input                      | ADS8912B Digital Output                  |

|------------------------------------------------------|------------------------------------------------|------------------------------------------|

| VinP = -12V, $VinN = +12V$ , $VinMin (Dif) = -24V$   | VoutDif = -4.00V, VoutP = 0.25V, VoutN = 4.25V | 238E3 <sub>H</sub> -116509 <sub>10</sub> |

| VinP = +12V, $VinN = -12V$ , $VinMax$ (Dif) = $+24V$ | VoutDif = +4.0V, VoutP = 4.25V, VoutN = 0.25V  | 1C71C <sub>H</sub> +116508 <sub>10</sub> |

| Supplies and Reference     |      |       |    |       |      |

|----------------------------|------|-------|----|-------|------|

| HVDD HVSS Vcc Vee Vref Vcm |      |       |    | Vcm   |      |

| +15V                       | -15V | +5.0V | 0V | +4.5V | 2.5V |

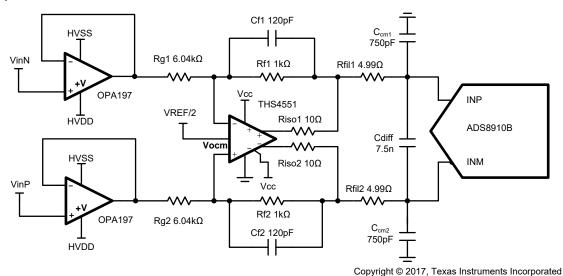

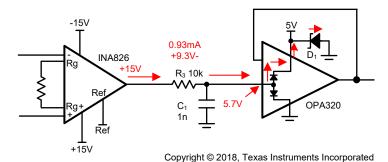

# **Design Description**

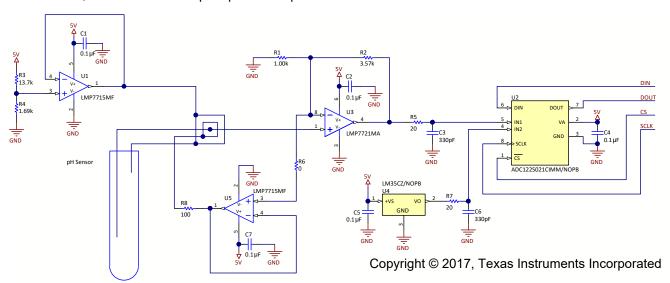

This analog front end (AFE) and SAR ADC data acquisition solution can measure true differential voltage signals in the range of  $\pm 24$ V (or absolute input range VinP =  $\pm 12$ V, VinN =  $\pm 12$ V) offering high-input impedance supporting data rates up to 500ksps with 18-bit resolution. A precision, 36-V rail-to-rail amplifier with low-input bias current is used to buffer the inputs of a fully-differential amplifier (FDA). The FDA attenuates and shifts the signal to the differential voltage and common-mode voltage range of the SAR ADC. The values in the *component selection* section can be adjusted to allow for different input voltage levels.

This circuit implementation is used in accurate measurement of true differential voltage in *Application-Specific Test Equipment*, *Data Acquisition (DAQ) cards*, and *Analog Input Modules* used in *Programmable Automation Control (PAC)*, *Discrete Control System (DCS)*, and *Programmable Logic Control (PLC)* applications.

#### **Specifications**

| Specification                          | Goal                | Calculated            | Simulated             |

|----------------------------------------|---------------------|-----------------------|-----------------------|

| Transient ADC Input Settling (500ksps) | << 1 LSB; << 34μV   | N/A                   | 0.5µV                 |

| Noise (at ADC Input)                   | 10μV <sub>RMS</sub> | 9.28μV <sub>RMS</sub> | 9.76μV <sub>RMS</sub> |

| Bandwidth                              | 1.25MHz             | 1.25MHz               | 1.1MHz                |

#### **Design Notes**

- Verify the linear range of the op amp (buffer) based on the common mode, output swing specification for linear operation. This is covered in the *component selection* section. Select an amplifier with low input bias current.

- 2. Find ADC full-scale range and common-mode range specifications. This is covered in the *component* selection.

- 3. Determine the required attenuation for the FDA based on the input signal amplitude, the ADC full-scale range and the output swing specifications of the FDA. This is covered in the *component selection* section.

- 4. Select COG capacitors to minimize distortion.

- 5. Use 0.1% 20ppm/°C film resistors or better for good accuracy, low gain drift, and to minimize distortion.

- 6. Understanding and Calibrating the Offset and Gain for ADC Systems covers methods for error analysis. Review the link for methods to minimize gain, offset, drift, and noise errors

- 7. Introduction to SAR ADC Front-End Component Selection covers methods for selecting the charge bucket circuit Rfilt and Cfilt. These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here will give good settling and AC performance for the amplifier, gain settings, and data converter in this example. If the design is modified, a different RC filter must be selected. Refer to the Precision Labs videos for an explanation of how to select the RC filter for best settling and AC performance.

# Component Selection and Settings for Buffer Amplifier and FDA

1. Verify the buffer amplifier input range for linear operation:

Select Supplies

$$(V -) = -15V$$

,  $(V +) = +15V$  to allow VinP =  $\pm 12V$  VinN =  $\pm 12V$  range  $(V -) - 0.1V < V_{cm} < (V +) - 3V$  from OPA197 common-mode voltage specification  $-15.1V < V_{cm} < +12V$  allows required  $\pm 12V$  input voltage range

2. Verify the buffer amplifier output range for linear operation:

$$(V-)+0.6V < V_{out} < (V+)-0.6V$$

from OPA197 Aol specification for linear operation

- -14.4V<V<sub>out</sub><14.4V allows required±12Voutput voltage range

- 3. Find ADC full-scale input range. In this circuit,  $V_{REF} = 4.5V$ :

$$ADC_{Full-Scale Range} = \pm V_{REF} = \pm 4.5V$$

from ADS8910B datasheet

4. Find the required ADC common-mode voltage:

$$V_{CM} = \frac{+V_{REF}}{2}$$

+2.25V from ADS8910B datasheet, therefore set FDA VCOM = 2.25V

5. Find FDA absolute output voltage range for linear operation:

0.23 < V<sub>out</sub> < 4.77V from THS4551 output low/high specification for linear operation

However, the positive range is limited by  $ADC_{Full-Scale\ Range}$   $\pm 4.5V$ , therefore

$$0.23V < V_{out} < 4.5V$$

where  $V_{outMin} = 0.23V$ ,  $V_{outMax} = 4.5V$

6. Find FDA differential output voltage range for linear operation. The general output voltage equations for this circuit follow:

$$V_{outMin}$$

$\frac{V_{outDifMin}}{2} + V_{cm}$  and  $V_{outMax}$   $\frac{V_{outDifMax}}{2} + V_{cm}$

Re-arrange the equations and solve for  $V_{\text{outDifMin}}$  and  $V_{\text{outDifMax}}$

Find maximum differential output voltage range based on worst case:

$$V_{outDifMax} = 2 \cdot V_{outMax} - 2 \cdot V_{cm} = 2 \cdot (4.5V) - 2 \cdot (2.25V) = 4.5V$$

$$V_{outDifMin} = 2 \cdot V_{outMin} - 2 \cdot V_{cm} = 2 \cdot (0.23V) - 2 \cdot (2.5V) = -4.04V$$

Based on combined worst case, choose  $V_{outDifMin} = -4.04V$  and  $V_{outDifMax} = +4.04V$

7. Find the FDA differential input voltage range:

$$V_{inDifmax} = V_{inPmax} - V_{inNmin} = +12V - (-12V) = +24V$$

$$V_{inDifmin} = V_{inPmin} - V_{inNmax} = -12V - (+12V) = -24V$$

8. Find FDA required attenuation ra

$$Gain_{FDA} \quad \frac{V_{outDifMax} - V_{outDifMin}}{V_{inDifMax} - V_{inDifMin}} \quad \frac{\left(+4.04V\right) - \left(-4.04V\right)}{\left(+24V\right) - \left(-24V\right)} \quad 0.166\frac{V}{V} \approx \frac{1}{6}\frac{V}{V}$$

9. Find standard resistor values to set the attenuation:

$$Gain_{FDA}$$

$\frac{R_f}{R_g}$   $\frac{1}{6}V/V \Rightarrow \frac{R_g}{R_f}$   $\frac{1.00k\Omega}{6.04k\Omega}$   $\frac{1}{6.04}V/V$

10. Find

$$\mathbf{C}_f$$

for cutoff frequency  $f_c$ ,  $\mathbf{R}_{\mathrm{fINA}} = 1 \mathrm{k}\Omega$ :

$$C_f = \frac{1}{2 \cdot \pi \cdot f_c \cdot R_{\mathrm{fINA}}} = \frac{1}{2 \cdot \pi \cdot \left(1.25 MHz\right) \cdot \left(1 \mathrm{k}\Omega\right)} = 127 \, pF \, or \, 120 \, pF \, standard \, value$$

# **DC Transfer Characteristics**

The following graph shows a linear output response for differential inputs from +24V to -24V.

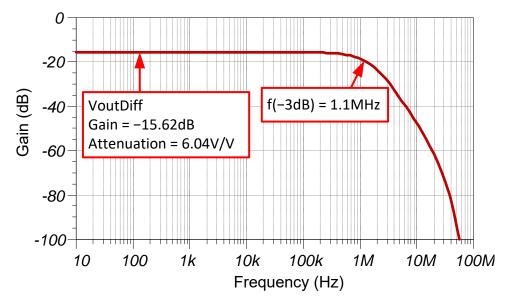

#### **AC Transfer Characteristics**

The simulated bandwidth is approximately 1.1MHz and the gain is -15.62dB which is a linear gain of approximately 0.166V/V (attenuation ratio 6.04V/V).

#### **Noise Simulation**

Simplified Noise calculation for rough estimate:

$$f_c = \frac{1}{2 \cdot \pi \cdot R_f \cdot C_f} = \frac{1}{2 \cdot \pi \cdot (1k\Omega) \cdot (120pF)} = 1.33MHz$$

Noise contribution of OPA197 buffer referred to ADC input

$$\begin{split} E_{nOPA197} &= e_{nOPA197} \cdot \sqrt{K_n \cdot f_c} \cdot Gain_{FDA} \\ E_{nOPA197} &= \left(5.5nV \, / \, \sqrt{Hz}\right) \cdot \sqrt{1.57 \cdot 1.33MHz} \cdot 0.166V \, / \, V = 1.319 \mu V_{RMS} \end{split}$$

Noise of THS4551 FDA referred to ADC input

Noise gain:

$$NG = 1 + R_f / R_g = 1 + \frac{1.00k\Omega}{6.04k\Omega} = 1.166V / V$$

$$e_{noFDA} = \sqrt{(e_{nFDA} \cdot NG)^2 + 2(i_{nFDA} \cdot R_f)^2 + 2(4kTR_f \cdot NG)}$$

$$e_{noFDA} = \sqrt{(3.4nV / \sqrt{Hz} \cdot 1.166V / V)^2 + 2(0.5pA / \sqrt{Hz} \cdot 1k\Omega)^2 + 2(16.56 \cdot 10^{-18} \cdot 1.166V / V)}$$

$$e_{noFDA} = 7.40nV / \sqrt{Hz}$$

$$E_{nFDA} = e_{noFDA} \cdot \sqrt{K_n \cdot f_c} = (7.40nV / \sqrt{Hz}) \cdot \sqrt{1.57 \cdot 1.33MHz} = 9.28\mu V_{RMS}$$

$$Total \ Noise = \sqrt{E_{nFDA}^2 + E_{nOPA197}^2} = \sqrt{(9.28\mu V_{RMS})^2 + (1.32\mu V_{RMS})^2} = 9.37\mu V_{RMS}$$

Note that calculated and simulated match well. Refer to *Calculating the Total Noise for ADC Systems* for detailed theory on this subject.

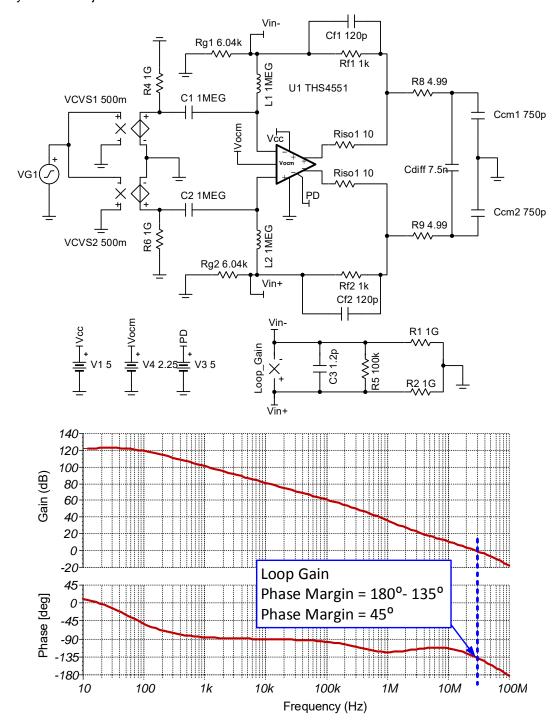

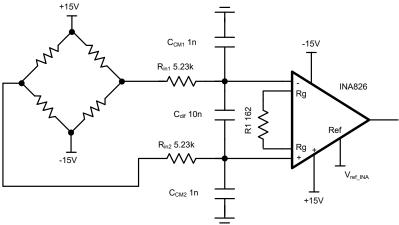

# **Stability Simulation**

The following circuit is used in TINA to measure loop gain and verify phase margin using AC transfer analysis in TINA. Resistors  $R_{\rm ISO} = 10\Omega$  are used inside the feedback loop to increase phase margin. The circuit has 45 degrees of phase margin. Refer to *TI Precision Labs - Op Amps: Stability 4* for detailed theory on this subject.

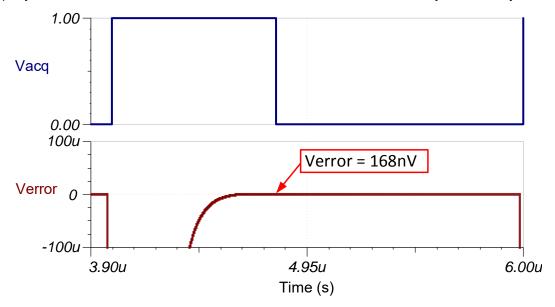

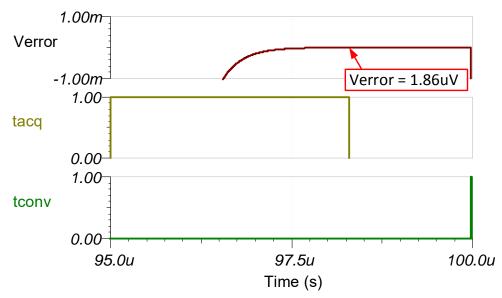

# **Transient ADC Input Settling Simulation**

The following simulation shows settling to a 24-V DC differential input signal with the OPA197 buffers inputs set at +12V and –12V. This type of simulation shows that the sample and hold kickback circuit is properly selected. Refer to *Refine the Rfilt and Cfilt Values* for detailed theory on this subject.

# **Design Featured Devices**

| Device                  | Key Features                                                                                                                 | Other Possible Devices  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ADS8912B <sup>(1)</sup> | 18-bit resolution, 500-ksps sample rate, integrated reference buffer, fully-differential input, Vref input range 2.5V to 5V. | Link to similar devices |

| THS4551                 | FDA, 150-MHz bandwidth, Rail-to-Rail Output, VosDriftMax = $1.8\mu$ V/°C, $e_n$ = $3.3$ nV/rtHz                              | Link to similar devices |

| OPA197                  | 36V, 10-MHz bandwidth, Rail-to-Rail Input/Output, VosMax = ±250µV, VosDriftMax = ±2.5µV/°C, bias current = ±5pA              | Link to similar devices |

| REF5045                 | VREF = 4.5V, 3 ppm/°C drift, 0.05% initial accuracy, 4μVpp/V noise                                                           | Link to similar devices |

<sup>(1)</sup> The REF5045 can be directly connected to the ADS8912B without any buffer because the ADS8912B has a built in internal reference buffer. Also, the REF5045 has the required low noise and drift for precision SAR applications. The THS4551 provides the attenuation and common-mode level shifting to the voltage range of the SAR ADC. In addition, this FDA is commonly used in high-speed precision fully-differential SAR applications as it has sufficient bandwidth to settle to charge kickback transients from the ADC input sampling. The OPA197 is a 36-V operational amplifier that provides a very high input impedance front end, buffering the FDA inputs

# Link to Key Files

Source files for this design - http://www.ti.com/lit/zip/sbac183

For direct support from TI Engineers use the E2E community:

e2e.ti.com

TI Precision Labs Training Series community:

TI Precision Labs - https://training.ti.com/ti-precision-labs-overview

SBAA244-February 2018

# Circuit to Increase Input Range on an Integrated Analog Front End (AFE) SAR ADC

# Cynthia Sosa

| Input         | ADC Input     | Digital Output ADS7042 |

|---------------|---------------|------------------------|

| VinMin = –40V | AIN-xP = -10V | -131072 <sub>10</sub>  |

|               | AIN-xGND = 0V | 20000 <sub>H</sub>     |

| VinMax = 40V  | AIN-xP = 10V  | 131071 <sub>10</sub>   |

|               | AIN-xGND = 0V | 1FFFF <sub>H</sub>     |

| Power Supplies |      |  |

|----------------|------|--|

| AVDD DVDD      |      |  |

| 5V             | 3.3V |  |

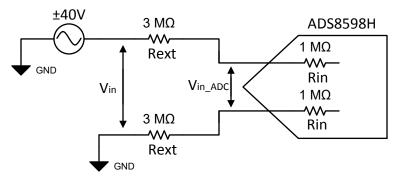

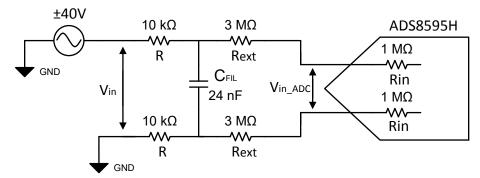

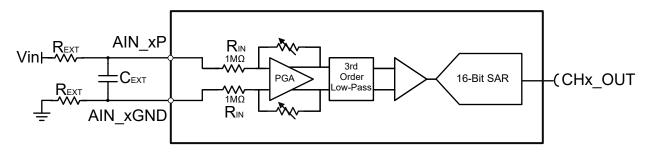

# **Design Description**

This cookbook design describes how to expand the input range of a SAR ADC with an integrated analog front end (AFE) and decrease the loss of accuracy by implementing a two-point calibration method. This design uses the ADS8598H at the full scale range of ±10V and expands the accessible input range to ±40V. This allows for a wider input range to be used without extra analog circuitry to step down the voltage; instead a simple voltage divider is used to interact with the AFE of the device to step down the voltage near the device input. A calibration method can be implemented to eliminate any error that could occur.

A similar cookbook design, Reducing Effects of External RC Filter on Gain and Drift Error for Integrated AFE: ±10 V, up to 200kHz, 16 bit, explaining how to measure introduced drift from external components can prove to also be helpful in this application. Increasing the input range that the ADC can measure proves useful in end equipment such as: Multi Function Relays, AC Analog Input Modules, and Control Units for Rail Transport.

# **Specifications**

| Specification | Measured Accuracy Without Calibration | Measured Accuracy With Calibration |

|---------------|---------------------------------------|------------------------------------|

| ±40V          | 0.726318%                             | 0. 008237%                         |

# **Design Notes**

- 1. Use low-drift resistors to decrease any error introduced due to temperature drift, such as 50 ppm/°C with 1% tolerance or better. Note that as resistor values increase to  $1M\Omega$  and beyond, low-drift precision resistors can become more expensive.

- 2. An input filter is frequently required for this configuration. Placing it directly after the large input impedance can cause errors because of the capacitor leakage. If an input filtering capacitor is needed, an alternate schematic is shown in this design.

#### **Component Selection**

The internal impedance of the device is  $1M\Omega$ , the external resistor is selected based on the desired extended input range (Vin), in this case  $\pm 40V$ . This external resistor forms a voltage divider with the internal impedance of the device, stepping down the input voltage within the ADC input range of  $\pm 10V$ .

1. Rearrange the voltage divider equation to solve for the external resistor value. This same equation can later be used to calculate the expected Vin<sub>ADC</sub> value from the input voltage.

$$V_{in\_ADC}$$

$V_{in} \cdot \frac{R_{in}}{R_{in} + R_{ext}}$

$R_{ext}$   $\frac{V_{in} \cdot R_{in}}{V_{in\_ADC}} - R_{in}$

2. Solve for the external resistor value for the desired extended input voltage. Vin =  $\pm 40$ V, Rin = 1M  $\Omega$

$$R_{ext} = \frac{40V \cdot 1M\Omega}{10V} - 1M\Omega$$

The input can be extended to a variety of ranges, depending on what external resistor value is used.

| Vin | Rext  |

|-----|-------|

| ±40 | 3ΜΩ   |

| ±30 | 2ΜΩ   |

| ±20 | 1ΜΩ   |

| ±12 | 200kΩ |

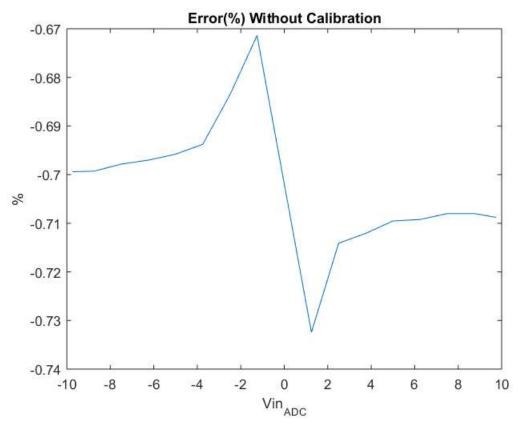

#### **Non Calibrated Measurements**

Different DC input values ranging through the full ±40-V scale were used to measure the ADC voltage input and the accuracy of the measurement. The percent error of the value was calculated using the following equation:

Error(%)

$$\frac{Vin_{ADC} - Vout_{ADC}}{Vin_{ADC}} \cdot 100$$

# **Two-Point Calibration**

Calibration can be applied in order to eliminate the reading error introduced by the external resistor. The two-point calibration applies and samples two test signals at 0.25V from the full scale input range within the linear range of the ADC. These sample measurements are then used to calculate the slope and offset of the linear transfer function. Calibration will eliminate both the gain error introduced by the external resistor and the internal device gain error.

1. Apply test signal at 9.75V:

| Vmin   | Measured Code |

|--------|---------------|

| -9.75V | -128689       |

2. Apply test signal at -9.75V:

| Vmin   | Measured Code |

|--------|---------------|

| -9.75V | 128701        |

3. Calculate slope and offset calibration coefficients:

$$\begin{split} m & \quad \frac{Code_{max} - Code_{min}}{V_{max} - V_{min}} \quad \frac{128701 - (-128689)}{9.75V - (-9.75V)} \quad 13199.487 \\ b & = Code_{min} - m \cdot V_{min} \quad -128689 - 13199.487 \cdot (-9.75V) = 5.998 \end{split}$$

4. Apply calibration coefficients to all subsequent measurements:

$$Vin_{ADC\_Calibrate} = \frac{Code-b}{m} = \frac{128701-6}{13199.487} = 9.5000$$

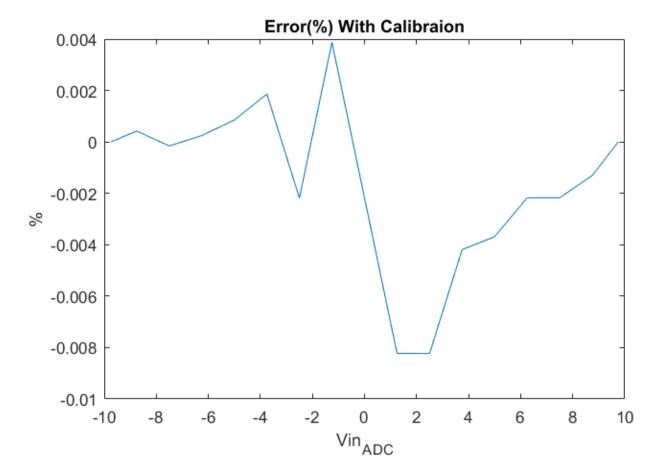

#### **Two-Point Calibration Measurements**

Calibration Coefficients

m = 13199.487; b = 5.998

When calibration is applied the readings error is dramatically reduced.

# **Alternate Schematic With Filter Capacitor**

Due to the high-value resistors used, introducing a capacitor would lead to significant impact in readings, such as increase drift experienced. This is because of the capacitor leakage. This leakage will vary over time and temperature and will generate errors that are difficult to calibrate out. If an input filter is needed, the alternate schematic can be used to implement it. The capacitor is placed with a balanced resistor-capacitor filter before the external resistors in relation to the input signal.

# **Alternate Schematic With Filter Capacitor - Component Selection**

External anti-aliasing RC filters reduce noise and protect from electrical overstress. A balanced RC filter configuration is required for better common-mode noise rejection; matching external resistors are added to both the negative and positive input paths. These external resistors should also be low-drift resistors as stated in the *Design Notes*.

1. Choose a value of R based on the desired cutoff frequency. This example uses a cutoff frequency of 320Hz, and a resistor value of  $10k\Omega$ .

$$R = 10k\Omega$$

2. Select C<sub>FIL</sub>

$$C_{FIL} \quad \frac{1}{2 \cdot \pi \cdot f_c \cdot 2 \cdot R} \quad \frac{1}{2 \cdot \pi \cdot 320 \text{Hz} \cdot 2 \cdot 10 \text{k}\Omega} \quad 24.8 \text{nF}$$

Nearest standard capacitor value available, C<sub>FII</sub> = 24 nF

#### **Design Featured Devices**

| Device   | Key Features                                                                                 | Link      | Other Possible Devices |

|----------|----------------------------------------------------------------------------------------------|-----------|------------------------|

| ADS8598H | 18-bit high-speed 8-channel simultaneous-sampling ADC With bipolar inputs on a single supply | Datasheet | Parametric Search      |

#### For direct support from TI Engineers use the E2E community:

e2e.ti.com

Other Links

www.ti.com/adcs

www.ti.com/precisionadc

SBAA247-January 2018

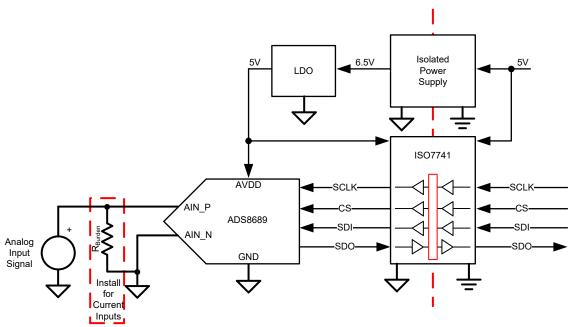

# Circuit for Driving High-Voltage SAR ADCs for High-Voltage, True Differential Signal Acquisition

Dale Li

| Input             | ADC Input   | Digital Output ADS7042                     |

|-------------------|-------------|--------------------------------------------|

| VinDiffMin = –20V | CH_x = +10V | 7FFF <sub>H</sub> , or 32767 <sub>10</sub> |

| VinDiffMax = +20V | CH_x = -10V | 8000 <sub>H</sub> , or 32768 <sub>10</sub> |

| Power Supplies |      |                        |                        |

|----------------|------|------------------------|------------------------|

| AVDD           | DVDD | V <sub>cc</sub> (HVDD) | V <sub>ss</sub> (HVSS) |

| 5.0V           | 3.3V | +15V                   | -15V                   |

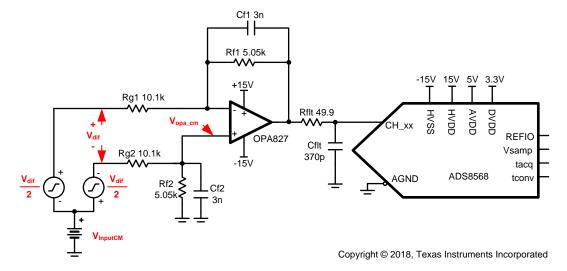

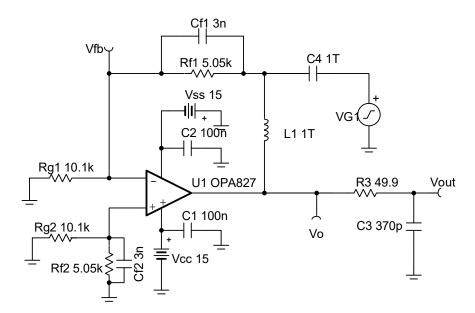

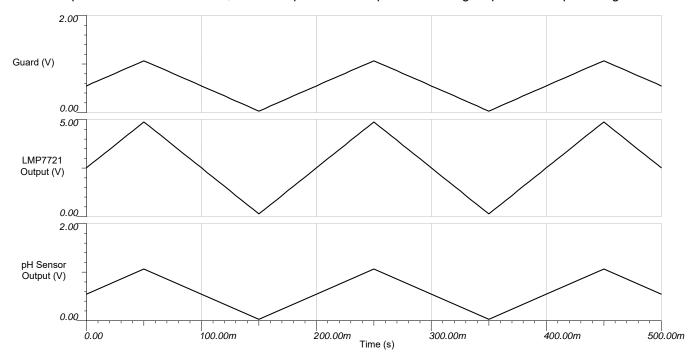

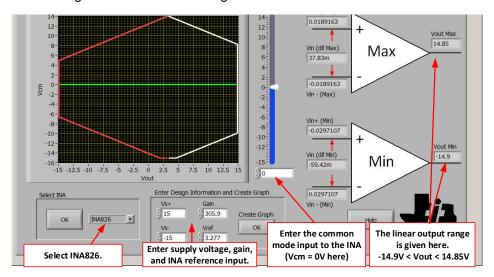

# **Design Description**

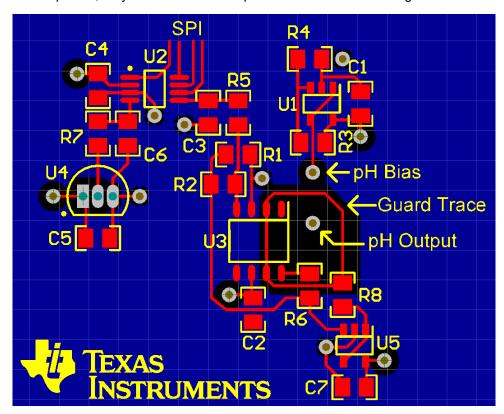

This design shows a solution to drive high-voltage SAR ADC to implement data capture for high-voltage fully differential signal which may have a wide common-mode voltage range depended on amplifier's power supply and input signal's amplitude. A general high-voltage precision amplifier performs the differential to single-ended conversion and drives high-voltage SAR ADC single-ended input scale of ±10V at highest throughput. This type of application is popular in end equipment such as: *Multi-Function Relays*, *AC Analog Input Modules*, and *Control Units for Rail Transport*. The values in the *component selection* section can be adjusted to allow for different level differential input signal, different ADC data throughput rates, and different bandwidth amplifiers.

# **Specifications**

| Specification                              | OPA827 Calculated  | OPA827 Simulated    | OPA192 Calculated  | OPA192 Simulated   |

|--------------------------------------------|--------------------|---------------------|--------------------|--------------------|

| Common Mode Input Range (with Vdif = ±20V) | ±26V               | ±26V                | ±35V               | ±35V               |

| Transient ADC Input Settling Error         | < 1/2LSB (< 152µV) | 0.002 LSB (0.568µV) | < 1/2LSB (< 152µV) | 0.006 LSB (1.86μV) |

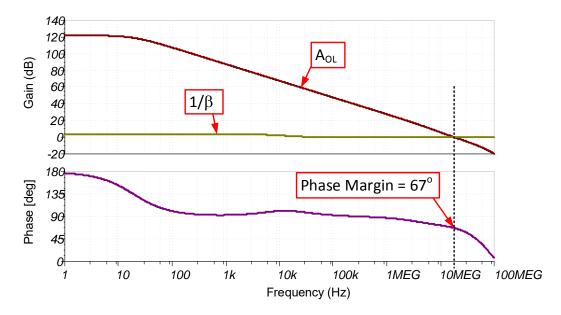

| Phase Margin of driver                     | > 45°              | 67.1°               | > 45°              | 68.6°              |

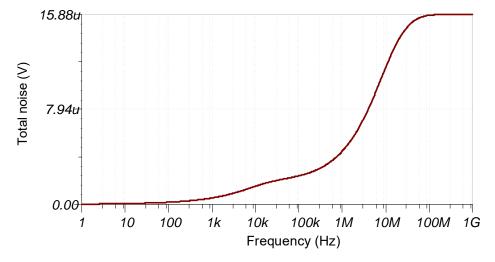

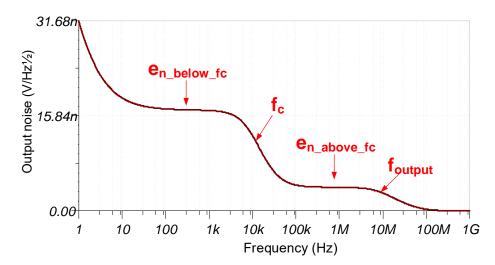

| Noise (at ADC Input)                       | 14.128µVrms        | 15.88µVrms          | 5.699µVrms         | 6.44µVrms          |

# **Design Notes**

- 1. Determine the amplifier gain based on the differential input signal level, the ADC's configuration for input range. This is covered in the *component selection* section.

- 2. Determine amplifier's linear range based on common mode voltage, input swing, and power supplies. This is covered in the *component selection* section.

- 3. In this design circuit, the common-mode voltage of the input signal can be any value in the range of V<sub>InputCM</sub>. The derivation of this range is provided in the *component selection* section for the OPA827 and OPA192.

- 4. Select COG capacitors to minimize distortion.

- 5. Use 0.1% 20ppm/°C film resistors or better for good accuracy, low gain drift, and to minimize distortion. Review Statistics Behind Error Analysis for methods to minimize gain, offset, drift, and noise errors.

- 6. Refer to Introduction to SAR ADC Front-End Component Selection for an explanation of how to select Rfilt and Cfilt for best settling and AC performance. These component values are dependent on the amplifier bandwidth, data converter sampling rate, and data converter design. The values shown here provide good settling and AC performance for the amplifier and data converter in this example. If the design is modified, select a different RC filter.

#### **Component Selection**

1. Find the gain based on differential input signal and ADC full-scale input range.

$$Gain_{OPA} = \frac{\pm V_{ADC(range)}}{\pm V_{DifIn(range)}} = \frac{\pm 10V}{\pm 20V} = 0.5V / V$$

2. Find standard resistor values for differential gain. Use the *Analog Engineer's Calculator* ("Amplifier and Comparator\Find Amplifier Gain" section) to find standard values for Rf/Rg ratio.

$$Gain_{OPA} = \frac{R_f}{R_G} = \frac{5.05 k \Omega}{10.1 k \Omega} = 0.5$$

3. Find the amplifier's maximum and minimum input for linear operation (that is, the common mode range of the amplifier,  $V_{cm\ amp}$ ). For this example, the OPA827 is used.

$$V_{-} + 3V < V_{cm\_opa} < V_{+} - 3V$$