# **MCU F05 Platform Flash-ECC Module**

The flash electrically erasable programmable read-only memory (Flash EEPROM, or Flash) module is a type of nonvolatile memory which has fast read access times but slower write and erase times. Flash EEPROM performs erasing by sector, rather than word at a time as in regular EEPROM.

| Торі | ic                       | Page |

|------|--------------------------|------|

|      |                          |      |

| 1    | Revision History         | 2    |

| 2    | Overview                 | 3    |

| 3    | Functional Block Diagram | 5    |

| 4    | Operation                | 7    |

| 5    | Control Registers.       | 33   |

|      |                          |      |

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments.

This revision supersedes all previous versions.

## 1 Revision History

| Date    | Version  | Author       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4/15/04 | Rev 0.10 | Charles Tsai | Initial Draft                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4/20/04 | Rev 0.11 | Charles Tsai | Memory mapped ECC bank to 4Mbyte offset as a<br>mirror image.<br>During OTP sector read access the ECC is bypassed.<br>Allowed any two different sectors to be excluded from<br>ECC checking.<br>Added diagnostic mode to verify ECC logic.<br>ECC logic can be removed during netlist synthesis.<br>Non-0101 value to enable ECC logic.<br>Any flash memory access which does not decode to<br>any bank will generate an illegal address signal. |

| 4/22/04 | Rev 0.12 | Charles Tsai | Change default bank access wait state value to 1 after reset.<br>Added Section 7, <i>Manufacturing Test</i>                                                                                                                                                                                                                                                                                                                                       |

| 4/26/04 | Rev 0.13 | Charles Tsai | Global low power mode with SYS_LPM=1 will put the<br>entire flash module in sleep mode.<br>Clarification of the manufacturing test section<br>Clarify that both ECC logic and diagnostic mode can<br>be enabled at the same time.                                                                                                                                                                                                                 |

| 5/11/04 | Rev 0.14 | Charles Tsai | Change the ECC bank from 64-bit to 16-bit datawidth.                                                                                                                                                                                                                                                                                                                                                                                              |

| 8/12/04 | Rev 0.15 | Charles Tsai | Remove ECCBANKID[3:0] register<br>Reset value of EDACEN is 0101 for disable ECC. All<br>other combinations are ECC enabled.<br>Support byte and half word write to register file.<br>Improve readability                                                                                                                                                                                                                                          |

## 2 Overview

The MCU F05 Platform Flash-ECC is generally used to provide permanent program/data storage or factory calibration data; and can be programmed and electrically erased many times to allow for faster code development. The built-in EDAC (Error Detection And Correction) circuit allows flash memory faults to be either detected or corrected.

Flash EEPROM differs from standard EERPOM in that all bits in a flash sector are erased in bulk, whereas standard EEPROM is erased a word at a time.

## 2.1 Features

□ Supports multiple flash banks for program and data storage.

- Contains up to 8 banks (including ECC bank) of up to 16 Megabits each

- □ Error detection and correction capability

- □ Two sectors can be selected for exclusion from ECC checking

- □ Enables simultaneous read access on a bank while performing a write or erase operation on any one of the remaining banks.

- Supports erase and program suspend, which allows software to fetch data from the flash bank currently being erased or programmed.

- □ Supports automating flash erase and programming through integrated state machine

- □ Allows up to 32 sectors per flash bank

- □ Provides optional set of four 32-bit protection keys.

- □ Provides built-in power mode control logic.

- Support flash memory replacement by an external RAM for emulation

## 2.2 Definition of Terms

Terms used in this document have the following meanings:

BAGP (bank active grace period): Time (in SYSCLK cycles) from the most recent flash access of a particular bank until that bank enters fallback power mode. This reduces power consumption by the flash: however, it can also increase access time.

- Charge pump: Voltage generators and associated control (logic, oscillator, and bandgap, for example).

- CSM (command state machine): One of the three state machines present in the flash module.

- □ Fallback power mode: The power mode (active, standby or sleep, depending on which mode is selected) into which a bank or the charge pump falls back each time the active grace period expires.

- Flash bank: A group of flash sectors which share input/output buffers, data paths, sense amplifiers, and control logic. Flash bank can store both program instructions and data.

- □ ECC: Error Correction Code.

- □ ECC bank: Similar to flash bank but only store the ECC words.

- Flash module: Flash banks, charge pump, power and mode control logic, data path, wait logic, and write/erase state machines.

- MCU F05 Platform Flash-ECC: Flash module and CPU interface which includes pipeline logic and protection logic.

- OTP (one-time programmable): A program-only-once flash sector (cannot be erased)

- PAGP (pump active grace period): Time (in SYSCLK cycles) from when the last of the banks have entered fallback power mode until the pump enters a fallback power mode. This can reduce power consumption by the flash; however, it can also increase access time.

- Pipeline mode: The mode in which flash is read 64 bits at a time, giving faster apparent access times.

- Sector: A contiguous region of flash memory which must be erased simultaneously due to physical construction constraints.

- □ Standard read mode: The mode assumed when the pipeline mode is not enabled and flash is read no more than 32 bits at a time.

## 3 Functional Block Diagram

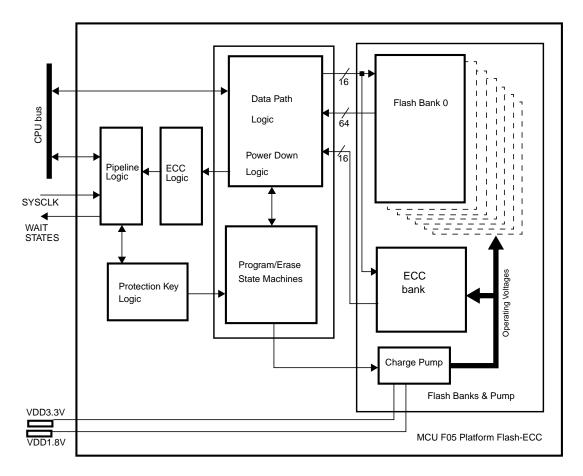

The MCU F05 Platform Flash-ECC consists of several major functional elements as shown in Figure 1.

Figure 1. F05 Platform Flash-ECC Functional Block Diagram

Up to eight banks (including ECC bank) of flash can be present in a single flash module. The present design supports up to 32 sectors per bank.

State machines in the flash module perform program, erase, and verify operations. The state machines permit the use of simpler program/erase/ verify software algorithms.

A single charge pump can supply all required voltages for up to eight flash banks. The MCU F05 Platform Flash-ECC requires 1.8V and 3.3V power

supplies for normal operation. Program and erase operations do not require any additional power supply.

The pipeline logic speeds up the apparent read access time of the flash module.

Programming the power-down logic correctly can produce significant power savings. The power-down registers control the power mode for each bank individually as well as for the charge pump.

The entire module is protected from unauthorized erasures or writes when the optional four 32-bit protection key words are used.

## 4 Operation

The following sections discuss various issues related to reset, reading, erasing, programming, power mode, protection, and wait state generation.

## 4.1 Reset State

The reset state exhibits the following properties:

- 1) Wait states are set to 1

- 2) Pipeline mode default is device specific

- 3) The OTP sector is turned off

- 4) All levels of protection are enabled

- 5) Power modes are set to Active (no power savings)

Your boot code must initialize the wait states and the desired pipeline mode to achieve the best possible system performance.

## 4.2 Flash Read Modes

In addition to *standard read mode*, the flash module also has *pipeline mode*, which affects the technique used to fetch the next memory word. Using this mode correctly increases clock speeds and CPU throughput.

#### 4.2.1 Standard Read Mode

Standard read mode is defined as the mode in effect when pipeline mode is inactive. The number of wait states used in standard read mode is user programmable within the flash control register FMBAC2.7:0.

#### 4.2.2 Pipeline Mode

In *pipeline mode*, two words are read in parallel from the flash core. Storing these two words in pipeline data buffers increases the bandwidth of the data coming out of the flash core, which provides effectively zero wait states on as many accesses as possible.

In pipeline mode, the flash data is always latched into the pipeline buffer first, then read from the pipeline buffer to the CPU. Pipeline mode removes the flash memory access time from the critical timing path, which allows the clock frequency to be higher.

Pipeline mode is enabled by setting the ENPIPE bit within the flash control register FMREGOPT.0. The pipeline mode default is device specific.

7

## 4.3 Memory Error Detection

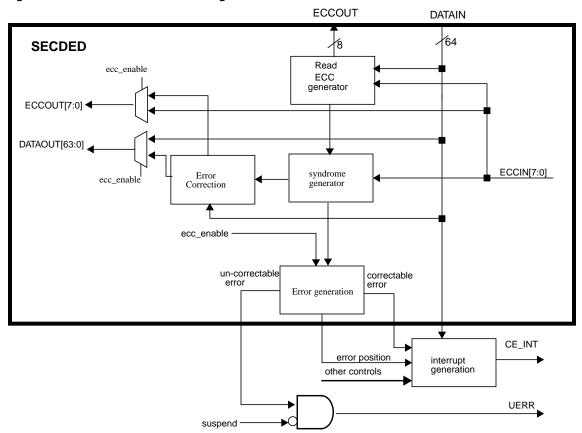

Platform F05 Flash module can contain an embedded SECDED (<u>Single Error</u> <u>C</u>orrection and <u>D</u>ouble <u>Error</u> <u>D</u>etection) circuit. SECDED when enabled provides capability to screen out memory faults and correct the fault. SECDED requires a total of eight ECC (<u>Error</u> <u>C</u>orrection <u>C</u>ode) check bits for each 64 bit of data to be stored in the flash memory. Data read out of flash memory pass through SECDED. During read operation, SECDED generates eight ECC bits based on the 64 bit read data value. These eight calculated ECC bits are then XORed with the pre-determined check bits associated with the read data. The 8-bit output is the syndrome. The syndrome is decoded to determine one of three conditions:

No error occurred

□ A correctable error occurred

□ A non-correctable error occurred

ECC is encoded based on modified Hamming code.

Figure 1–20. illustrates a SECDED block diagram.

**Note**: Since ECC is calculated for an entire 64-bit data, a non-64 bit read such as a byte read or a half-word read will still force the entire 64-bit data to be read and calculated.

**Note**: Depending on the device requirement the SECDED circuit can be included or removed during netlist synthesis

Figure 2. SECDED Block Diagram

## 4.3.1 ECC Flash Bank Overview

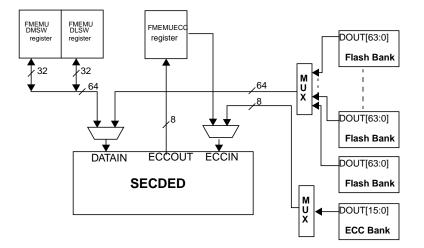

ECC words are stored in a separate flash bank. With a given flash configuration the last bank can be designated as an ECC bank. For example, if there are four flash banks then bank 4 can be designated as an ECC bank. ECC bank has 16-bit datawidth while all other flash banks have 64-bit datawidth. Therefore, reading ECC bank will return two ECC words. The correct ECC word is multiplexed out by flash wrapper during ECC syndrome generation.

### Figure 3. SECDED DATAIN and ECCOUT signal mapping

Several attributes are associated with ECC bank depending if ECC feature is enabled.

When ECC feature is enabled (EDACEN=! 0101),

- I flash wrapper reads both the addressed flash bank and the ECC bank

- CPU can directly read from ECC bank as if reading any other non-ECC bank but SECDED is bypassed.

- □ ECC logic is bypassed if reading from OTP sector.

When ECC feature is disabled (EDACEN=0101),

- I flash wrapper only reads the addressed flash bank without reading the designated ECC bank.

- the designated ECC bank can be used as regular data bank to store 16-bit data during non-pipeline mode.

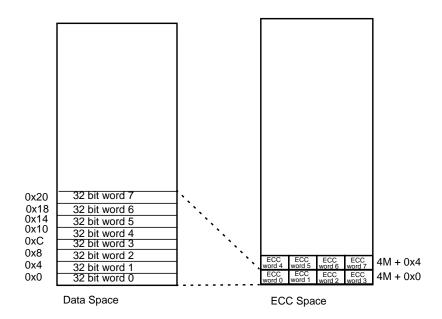

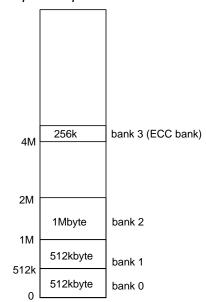

#### 4.3.2 ECC Memory Map

ECC data are memory mapped in the CPU's address space. It is mapped to 4M bytes offset from the flash memory base address. Each 64-bit data has its corresponding ECC word mapped to an address in the ECC space. Refer to Section Figure 4. for illustration.

## Figure 4. ECC Word Memory Mapping in CPU Address Space

- Notes: 1) ECC word 0 is memory mapped at byte address 4M+0. ECC word 1 is memory mapped at byte address 4M+1 and so on so forth.

- 2) ECC word 0 checks the 64-bit data word consisting of 32-bit word 0 and 32-bit word 1

- 3)

This ECC space starting address at 4Mbytes is a fixed location which allow software development to maintain compatibility. Mapping ECC bank to 4Mbyte starting address can be disabled via FMEDACCTRL1.11 control bit. When disabled, reading from the memory space at 4Mbytes will force the flash wrapper to generate an illegal address signal.

Only 16-bit read and 8-bit read are supported when reading from ECC space. During both 16-bit read and 8-bit read, the flash wrapper will duplicate ECC word x and ECC word x+1 on both the upper and lower 16 bit of the CPU read data bus. Flash wrapper can not support 32-bit read becaue the ECC memory bank is physically only 16-bit.

## Operation

Figure 5. ECC Bank Memory Map Example

Note: The base address of each bank must be a multiple of its bank size.

#### ain din 😽 👍 Μ To SECDED υ dout Х bank 0 (xx:0) (yy:0) right shift 3 bits CPU address Bank address ain ECC space decode din 4/64 right shift 1 bits right shift 1 bits dout bank N M ain din 🕂 Х М To SECDED U dout Х bank N+1 HRDATA[31:16] (ECC bank) HRDATA[15:0] HWDATA[31:16] Μ FSM U HWDATA[15:0] Х

## Figure 6. Bank Address Generation

**Note**: To prevent empty spaces from forming in the ECC bank the memory space occupied by the data banks should be contiguous.

#### 4.3.3 Illegal Address Generation

Any un-implemented flash space not decoded to a flash bank will cause an illegal address signal to be generated. The illegal address signal forces the CPU to take either data or instruction abort.

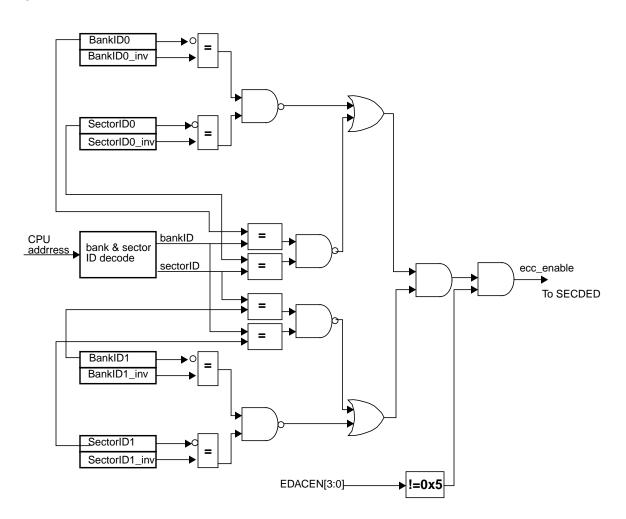

## 4.3.4 Disabling ECC

Globally the ECC logic is enabled and disabled by an 4-bit EDACEN register. When the four bits are 0101, the ECC logic is disabled. Any non-0101 combination value stored in the EDACEN register will enable the ECC logic. It is advisable to enable ECC logic with 0xA value stored in the EDACEN to prevent any soft error from disabling ECC logic. At any given time two different sectors (excluding the ECC bank) can be disabled from ECC checking. This is realized by specifying the bank/sector to be excluded and its inverse value in the sector disable register.

| 31   | 30       | 29   | 28 | 27    | 26      | 25    | 24 | 23 | 22      | 21 | 20 | 19 | 18       | 17 | 16 |

|------|----------|------|----|-------|---------|-------|----|----|---------|----|----|----|----------|----|----|

| Bank | (ID1_inv | erse |    | Secto | rID1_in | verse |    | I  | BankID1 |    |    | S  | SectorID | 1  |    |

| 15   | 14       | 13   | 12 | 11    | 10      | 9     | 8  | 7  | 6       | 5  | 4  | 3  | 2        | 1  | 0  |

| Bank | dD0_inv  | erse |    | Secto | rID0_in | verse |    | I  | BankID0 |    |    | S  | SectorID | 0  |    |

Table 1.Sector Disable Register

The sector disable register allows two different sectors to be specified for exclusion from ECC checking. Each sector to be excluded consists of two portions: the bank/sector ID value and its inverse value. Only when the programmed bank/sector ID value and its calculated inverted value matches the programmed inverse value will the sector selected be excluded from ECC checking. After reset the sector register is reset to all zeros which means that no sector is excluded from ECC checking.

## Figure 7. ECC\_ENABLE Generation

#### 4.3.5 Programming ECC Bank

ECC bank is programmed and erased the same way as other flash data banks. During programming, the bank ID must be specified along with the intended address/data are given to the flash wrapper. During erasure both the bank ID and the intended address are given to the flash wrapper. Platform F05 Flash-ECC wrapper contains an embedded FSM which carries out the operations. For details refer to Section 4.4, *Flash Commands*.

## 4.3.6 ECC Generation Algorithm

Platform F05 Flash-ECC wrapper uses modified Hamming code theory to generate ECC check bits. The ECC code word allow the gross-error condition of all zeros and all ones from memory to be detected.

| Table 2. | ECC encoding |

|----------|--------------|

|----------|--------------|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   | P | Part | ici | pat | ing | D | ata | bit | s |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|-----|-----|-----|---|-----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 6 | 6 | 6 | 6 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 4 | 4    | 4   | 4   | 4   | 4 | 4   | 4   | 4 | 4 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 2 | 2 | 2 |

| 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8    | 7   | 6   | 5   | 4 | 3   | 2   | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 |

|   |   |   |   |   |   |   |   | Х | Х | Х | Х | х | Х | Х | х    | Х   | Х   | х   | Х | х   | х   | Х | х |   |   |   |   |   |   |   |   | х | х | Х | Х | х |

| Х | Х | Х | Х | Х | Х | Х | х |   |   |   |   |   |   |   |      |     |     |     |   |     |     |   |   | Х | Х | х | х | Х | Х | х | Х | х | х | Х | Х | х |

| Х | Х | Х | Х | Х | Х | Х | х |   |   |   |   |   |   |   |      | Х   | Х   | х   | Х | х   | х   | Х | х |   |   |   |   |   |   |   |   | х | х | Х | Х | х |

| Х | Х |   |   |   |   |   |   | Х | Х | Х | Х | х | Х |   |      | Х   | Х   |     |   |     |     |   |   | Х | Х | х | х | Х | Х |   |   | х | х |   |   |   |

|   |   | Х | Х | Х |   |   |   | Х | Х | Х |   |   |   | Х | х    |     |     | х   | Х | х   |     |   |   | Х | Х | х |   |   |   | х | Х |   |   | Х | Х | х |

| Х |   | Х |   |   | Х | Х |   | Х |   |   | Х | Х |   |   | Х    | Х   |     | х   |   |     | Х   | Х |   | Х |   |   | Х | Х |   |   | Х | Х |   | Х |   |   |

|   |   |   | Х |   | Х |   | Х |   | Х |   | Х |   | Х | Х | Х    |     |     |     | Х |     | Х   |   | Х |   | Х |   | Х |   | Х | Х | Х |   |   |   | Х |   |

| Х |   | Х | Х |   | Х |   |   | Х | Х |   | Х |   |   |   | х    | Х   |     | х   | х |     | х   |   |   | Х | Х |   | х |   |   |   | Х |   | Х |   |   | х |

|   |   |   |   |   |   |   |   |     |   | Pa | arti | icip | oat | ing | J D | ata | bi | ts |   |   |   |   |   |   |   |   |   |                     |                        |

|---|---|---|---|---|---|---|---|-----|---|----|------|------|-----|-----|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---------------------|------------------------|

| 2 | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1   | I | 1  | 1    | 1    | 1   | 1   | 1   | 1   | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Parity <sup>2</sup> | Checkbits <sup>1</sup> |

| 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 9 8 | 3 | 7  | 6    | 5    | 4   | 3   | 2   | 1   | 0  | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                     |                        |

| Х | Х | х |   |   |   |   |   |     |   |    |      |      |     |     |     |     |    |    |   | х | Х | Х | х | х | Х | Х | Х | Odd                 | ECC[7]                 |

| Х | Х | х |   |   |   |   |   |     |   |    |      |      |     |     |     |     |    |    |   | х | Х | Х | х | х | Х | Х | Х | Odd                 | ECC[6]                 |

| Х | Х | Х |   |   |   |   |   |     |   |    |      | Х    | Х   | Х   | Х   | Х   | х  | Х  | х |   |   |   |   |   |   |   |   | Odd                 | ECC[5]                 |

|   |   |   | Х | Х | X | X | X | )   | < |    |      | Х    | Х   |     |     |     |    |    |   | х | Х | Х | Х | х | Х |   |   | Odd                 | ECC[4]                 |

|   |   |   | Х | Х | X |   |   |     |   | х  | х    |      |     | Х   | Х   | Х   |    |    |   | х | Х | Х |   |   |   | Х | Х | Odd                 | ECC[3]                 |

| х | Х |   | Х |   |   | X | X | 1   |   |    | х    | Х    |     | Х   |     |     | х  | Х  |   | х |   |   | Х | х |   |   | Х | Odd                 | ECC[2]                 |

| X |   | Х |   | Х |   | X |   | >   | < | х  | х    |      |     |     | Х   |     | х  |    | x |   | Х |   | Х |   | Х | Х | Х | Even                | ECC[1]                 |

|   | х | х |   |   | X |   | X |     | ( | х  |      |      | Х   |     |     | Х   |    | Х  | Х |   |   | Х |   | Х | Х | Х |   | Even                | ECC[0]                 |

Notes: 1) Each ECC[x] bit represents the parity bit for the corresponding data bits marked with x in the same row.

The ECC check bit is generated as either an XOR(Even) or an XNOR(Odd) of the data bits marked with x in the same row.

|        |        |   |        |        |        |        |        |        |        |        |        |        |        |        |        | _      |        | _      |        |        |        |        |        |        |        |   |        |        |        |        |        |   |        |   |        |        |

|--------|--------|---|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---|--------|--------|--------|--------|--------|---|--------|---|--------|--------|

|        |        |   |        |        |        |        |        |        |        |        |        |        |        |        |        | Da     | ta     | Err    | or     | Bit    |        |        |        |        |        |   |        |        |        |        |        |   |        |   |        |        |

| 6<br>3 | 6<br>2 | - | 6<br>0 | 5<br>9 | 5<br>8 | 5<br>7 | 5<br>6 | 5<br>5 | 5<br>4 | 5<br>3 | 5<br>2 | 5<br>1 | 5<br>0 | 4<br>9 | 4<br>8 | 4<br>7 | 4<br>6 | 4<br>5 | 4<br>4 | 4<br>3 | 4<br>2 | 4<br>1 | 4<br>0 | 3<br>9 | 3<br>8 | 3 | 3<br>6 | 3<br>5 | 3<br>4 | 3<br>3 | 3<br>2 | 3 | 3<br>0 |   | 2<br>8 | 2<br>7 |

| 3      |        | I | 0      | 9      | 0      | '      | 0      | 5      | 4      | 3      | 2      | I      | U      | 9      | 0      | '      | 0      | 5      | 4      | 3      | 2      | I      | 0      | 9      | 0      | 1 | 0      | 5      | 4      | 3      | 2      | I | 0      | 9 | 0      | 4      |

|        |        |   |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |   |        |        |        |        |        |   |        |   |        |        |

| 0      | 0      | 0 | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 0      | 0      | 0 | 0      | 0      | 0      | 0      | 0      | 1 | 1      | 1 | 1      | 1      |

| 1      | 1      | 1 | 1      | 1      | 1      | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1 | 1      | 1      | 1      | 1      | 1      | 1 | 1      | 1 | 1      | 1      |

| 1      | 1      | 1 | 1      | 1      | 1      | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 0      | 0      | 0 | 0      | 0      | 0      | 0      | 0      | 1 | 1      | 1 | 1      | 1      |

| 1      | 1      | 0 | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      | 1      | 1      | 1      | 0      | 0      | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1 | 1      | 1      | 1      | 0      | 0      | 1 | 1      | 0 | 0      | 0      |

| 0      | 0      | 1 | 1      | 1      | 0      | 0      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 1      | 0      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 1      | 1 | 0      | 0      | 0      | 1      | 1      | 0 | 0      | 1 | 1      | 1      |

| 1      | 0      | 1 | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 0 | 1      | 1      | 0      | 0      | 1      | 1 | 0      | 1 | 0      | 0      |

| 0      | 0      | 0 | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1      | 0 | 1      | 0      | 1      | 1      | 1      | 0 | 0      | 0 | 1      | 0      |

| 1      | 0      | 1 | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 0      | 1      | 0      | 0      | 0      | 1      | 1      | 0      | 1      | 1      | 0      | 1      | 0      | 0      | 1      | 1      | 0 | 1      | 0      | 0      | 0      | 1      | 0 | 1      | 0 | 0      | 1      |

| Table 3. | Syndrome | Decode to | Bit in Error |

|----------|----------|-----------|--------------|

|          | Synurome | Decoue io | D m m L m 0  |

|        |        |   |        |        |        |        |        |        |        |        | Da     | ta     | Err    | or     | Bit    |        |        |        |        |        |        |        |        |        |        |        |        | E      | СС     | Er     | roi    | r Bi   | it     |        |                  |         |

|--------|--------|---|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|---------|

| 2<br>6 | 2<br>5 |   | _      | 2<br>2 | 2<br>1 | 2<br>0 | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 0<br>9 | 0<br>8 | 0<br>7 | 0<br>6 | 0<br>5 | - 1    | 0<br>3 | 0<br>2 | 0<br>1 | 0<br>0 | 0<br>7 | 0<br>6 | -      | 0<br>4 | 0<br>3 | 0<br>2 | 0<br>1 | 0<br>0 |                  |         |

| 1      | 1      | 1 | 0      | 0      | 0      | 0      | -      | -      | -      | 0      | Ŭ      | •      | •      | -      | -      | 0      | •      | Ŭ      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 0      | -      |        | Ŭ      | Ŭ      | 0      | 0      | Bit[7]           |         |

| 1<br>1 |        | ' | 0      | Ŭ      | 0<br>0 | 0<br>0 | -      | -      | -      | 0      | Ŭ      | 0<br>1 | 1<br>0 | 1      | 1<br>0 | 1<br>0 | 1<br>0 | 1<br>0 | 1<br>0 | 1<br>0 | 0<br>0 | 1<br>0 | 0<br>1 | 0<br>0 | -      | 0<br>0 | 0<br>0 | 0<br>0 | Bit[6]<br>Bit[5] | (1,2,3) |

| 0      | 0      | - | •      | 1<br>1 | 1<br>1 | 1<br>0 | 1<br>0 | 1<br>0 | 0      | 0<br>1 | 1<br>0 | 1<br>0 | 0<br>1 | 0<br>1 | 0<br>1 | 0      | •      | Ŭ      | 1<br>1 | 1      | 1      | 1<br>0 | 1<br>0 | 1<br>0 | 0<br>1 | 0<br>1 | 0<br>0 | -      | -      | 1<br>0 | 0<br>1 | 0<br>0 | 0<br>0 | 0<br>0 | Bit[4]<br>Bit[3] | rome    |

| 1      |        | 0 | 1<br>0 | 0<br>1 | 0<br>0 | 1<br>1 | 1<br>0 | 0      | 0<br>1 | 1<br>1 | 1<br>0 | 0      | 1<br>0 | 0<br>1 | 0<br>0 | 1<br>1 | 1<br>0 | 0<br>1 | 1<br>0 | 0      | 0<br>0 |        | 1<br>0 | 0<br>1 | 0<br>1 | 1<br>1 | 0<br>0 | 0<br>0 | -      | -      | 0<br>0 | 1<br>0 | 0<br>1 | 0<br>0 | Bit[2]<br>Bit1]  | Syndro  |

| 0      | 1      | 1 | 0      | 0      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | 1      | 0      | 0      | 1      | 0      | 1      | 1      | 0      | 0      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 1      | Bit[0]           |         |

Notes: 1) Syndrome is a 8 bit value which decodes to the bit in error. The bit in error can be a bit among the 64 data bits or a bit among the 8 ECC check bits.

- 2) For example, if data bit 30 is in error then the syndrome would indicate as 11110001. If ECC check bit 5 is in error then syndrome would indicate as 00100000

- 3) Syndrome value of 00000000 indicates there is no error. Any other syndrome combinations not shown in the table are either double bit error or un-correctable multibit error

#### 4.3.7 No error occurred

This is the normal condition. No further action is taken. Note that the error correction logic is always in the datapath there will be a negative impact on the flash speed regardless of error occurring or not.

#### 4.3.8 Single error correction

SECDED is capable to correct an erroneous bit if it determines the total number of error bits in the data code word is one. The syndrome is decoded and generates a signal to invert the failing bit. There are three types of interrupts for which SECDED can generate when a single-bit error is detected and corrected. They are:

Interrupt on zero fail

Interrupt on one fail

□ Interrupt on error profiling

**Note**: Regardless if the interrupt is enabled, a correctable error is always corrected if EDACEN is enabled.

#### 4.3.9 Interrupt on Zero Fail

The most common failure mechanism of flash memory is a data retention loss where electrons drain off of the floating gate and results in a zero changing into a one. The SECDED circuit can detect this type of failure. The failing bit can be reprogrammed without the need of erasing flash first, thus restoring the electrons to the floating gate. This effectively fixes the flash and reduces the possibility that later on, a non-correctable failure will occur. The address and failing bit of each correctable error is latched and an interrupt can be generated to signal the program that a failure occurred.

When "Error On Zero Fail Only Enable" bit is set, the "Error On Zero Fail Only" flag can interrupt the processor when an expected 0 value turning into a 1 value. The address and error position are frozen from being updated until the correctable error status flag is cleared by the host system.

**Note**: Instruction to clear the status flag should be placed at the end of the interrupt subroutine. This is to avoid the address and position registers latching new values during interrupt subroutine.

#### 4.3.10 Interrupt on One Fail

In the less likely event of data gain when a failing bit occurs resulting in a one turning into a zero the flash sector must be erased first before reprogramming.

When "Error On One Fail Only Enable" bit is set, the "Error On One Fail Only" flag can interrupt the processor only when an expected 1 value turning into a 0 value. The address and error position are frozen from being updated until the correctable status flag is cleared by the host system

To generate interrupt for both zero fail and one fail simply enable both "Error on Zero Fail Only" and "Error on One Fail Only" enable bits.

If both enable bits are disabled then no interrupt is generated but SECDED still detects and corrects any correctable error.

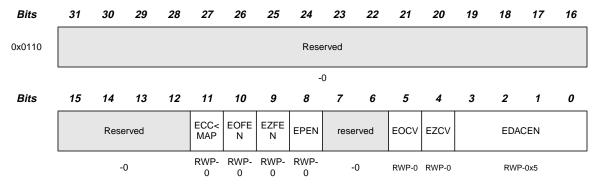

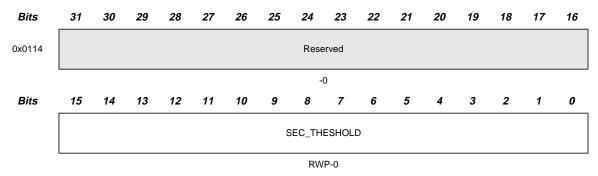

## 4.3.11 Profiling Mode

When profiling interrupt is enabled, each time a correctable error (either error on zero fail or error on one fail) is detected by the SECDED logic the correctable error occurrence counter (SEC\_OCCUR) is incremented. A profiling interrupt is generated when the correctable error occurrence counter is equal to the threshold value. The threshold value is stored in a 16 bit threshold (SEC\_THRESHOLD) register. The error occurrence counter is frozen when SUSPEND is high.

An error can be either a hard error or soft error. If the number of correctable error reaches a large threshold value in a short period of time then it is a high possibility that the error is a hard error. Although a hard single-bit error is correctable, it does increase the risk that additional soft error on the same word can cause a non-correctable failure.

## 4.3.12 Interrupt Request Generation

When the SECDED logic block detects a correctable error, the associated error address and error position are immediately stored into registers. During pipeline mode when data are pre-fetched in advanced of an CPU fetch the interrupt is not generated until the word is requested by CPU. When the addressed word is requested by CPU, the associated error interrupt status flag (Error on Zero Fail or Error on One Fail) is set and the interrupt request is generated if the word was detected to have error.

During pipeline mode the error address and position registers may be overridden with new values if the earlier word detected with error is not requested by CPU and another error is detected for the subsequent bank reads. This means that the address and position are overridden as long as the error status flag is not set. Once an error status flag bit is set the error address and position are frozen until the associated error status flag is cleared by CPU.

If profiling is enabled then any correctable error detected will increment the error counter. The counter is incremented immediately when an error is detected regardless if the faulted word is later accessed or not by CPU.

## 4.3.13 Non-correctable error detection

When there are more than one error bit detected, the SECDED generates a un-correctable error signal on UERR output pin to system module. During an non-correctable error the data is unchanged. The address location of which the un-correctable error is detected is saved in an error address register. This

register is frozen from being updated until it is read by the CPU. The UERR will set a un-correctable error interrupt flag inside system module. Abort is not generated for a non-correctable error due to timing impact on HOLDREQ generation. Inside system module a programmable error counter will make sure that the un-correctable error interrupt is handled within a proper time by the CPU. If the error counter times out then a system reset is issued to the CPU.

When an un-correctable error is detected, the error address is immediately saved to the un-correctable error register. The error signal is not generated to System module until the word is requested by CPU. Once the error signal is generated the un-correctable error address register is frozen until it is read by CPU. Similar to correctable error address register the un-correctable error address register can be overridden with new value if the previous detected un-correctable data word is not requested by CPU and another uncorrectable error is detected by SECDED logic.

#### 4.3.14 EEPROM emulation

Three features assist using the flash memory for EEPROM emulation. The first feature is that writing to a 64-bit data register will generate the proper 8-bit check bits in the check bit register. The data register and check bit register are memory mapped and can be accessed through flash wrapper's VBUS interface. Since the VBUS interface is 32-bit and therefore takes two 32-bit writes to input a 64-bit data. Any write to any one of these two registers will trigger a check bit generation.

During the cycle when data register is written to obtain the corresponding check bit value the CPU is waited for one clock cycle if ECC\_ENABLE signal is active since instruction fetch can take place at the same cycle.

Second, by setting the "Zero Condition Valid" flag, reading a zeroed 64-bits of memory with an associated zeroed 8-bit check bits will not create an error. This allows the programmer to zero out used portions of the flash when the table is to be moved to a new block.

Third, by setting the "One Condition Valid" flag, the check bits were chosen to allow for the valid state of all data bits one and all check bits one. This allows reading erased memory locations without creating an error.

#### 4.3.15 System Emulation

During emulation when SUSPEND signal is high the data read from memory is still passed to SECDED for correction if ECC\_ENABLE is active. If a correctable error is detected then it is corrected but error interrupt is not generated and error occurrence counter is not incremented if in profiling mode. If an un-correctable error is detected then the raw data is returned without generating un-correctable error signal.

#### 4.3.16 Diagnostic Mode

Flash wrapper can be put in diagnostic mode to verify SECDED logic. There are two diagnostic modes supported by the wrapper. The diagnostic mode is entered via DIAGMODE[1:0] control bits. Diagnostic mode can be enabled while ECC logic is also enabled for normal bank read. Flash wrapper will arbitrate for the usage of ECC logic if conflict occurs between normal bank read checking and diagnostic checking.

| Table 4. | DIAGMODE Encoding |

|----------|-------------------|

|----------|-------------------|

| DIAGMO | DDE[1:0] | Description                                  |

|--------|----------|----------------------------------------------|

| 0      | 0        | Default after reset. Diagnostic disabled.    |

| 0      | 1        | Diagnostic enabled. Data correction mode.    |

| 1      | 0        | Diagnostic enabled. Syndrome reporting mode. |

| 1      | 1        | Reserved                                     |

When diagnostic mode is disabled with DIAGMODE=00, the user can still write to the 64-bit EEPROM emulation data register. The corresponding check-bit is calculated and captured into ECC check-bit register. Write to ECC check-bit register has no effect.

When in diagnostic data correction mode with DIAGMODE=01, the 64-bit EEPROM emulation data register and the 8-bit ECC check-bit register are used to enter diagnostic data to exercise the SECDED logic. User can apply a diagnostic 64-bit data word with an error in any bit location and compare against a known checkword stored in the ECC check-bit register. When the correctable error is detected, the corrected data is saved back to the 64-bit data register and apply a corresponding 8-bit check word with an error in any bit location, The corrected check word is saved back to the ECC check-bit register. The error position register is also updated to indicate the bit position in error. For single bit correctable error the diagnostic correctable error status bit DCERR is set when a correctable error status bit DUERR is set when an uncorrectable error is detected. Status bits should be cleared by the user before applying a new diagnostic data.

When in diagnostic syndrome reporting mode with DIAGMODE=10, the resulting syndrome calculated by SECDED is captured into ECC check-bit register. The syndrome can be read by the user and compare with a known

syndrome value. Diagnostic data is not corrected and the error position register is not updated.

**Note**: Diagnostic data results in error detected during diagnostic mode does not set any interrupt status flag and does not generate any interrupt request or error signal.

During either diagnostic mode a correct sequence of writes to the data register and ECC check-bit register is required. The data register consists of both a 32-bit MSW (most significant word) and a 32-bit LSW (least significant word). The diagnostic is triggered by a write to the ECC check-bit register. When ECC check bit register is written, the 64-bit data word and the 8-bit check word are passed to the SECDED logic. Writing to either the MSW or LSW data word does not trigger the diagnostic event.

## 4.4 Flash Commands

The MCU F05 Platform Flash-ECC should be programmed, erased and verified only by using the F05 Flash API Library Functions. These functions are written, compiled and validated by Texas Instruments. The information provided in this document is intended to help explain how these functions work. It is not intended to provide sufficient detail for implementing programming or erasing functions.

The flash module contains a Command State Machine (CSM) to perform program, erase, and validate operations. The CSM supports the commands shown in Table 5. At the end of a system reset, the CSM is in Idle mode. The completion of any command also returns the CSM to Idle mode.

| Table 5. | Flash Command Summary |

|----------|-----------------------|

|----------|-----------------------|

| Command<br>Operand | Description                | Write Cycles Required |

|--------------------|----------------------------|-----------------------|

| 0x0010             | Program                    | 2                     |

| 0x0020             | Erase Sector               | 2                     |

| 0x0040             | Clear Status Register      | 1                     |

| 0x0080             | Suspend (program or erase) | 1                     |

| 0x0200             | Resume Programming         | 1                     |

| 0x0400             | Resume Erasing             | 1                     |

| 0x0800             | Program OTP                | 2                     |

| 0x1000             | Validate Sector            | 2                     |

Command writes (as well as OTP reads) can be performed only when pipeline mode is off. This is necessary to prevent data stored in the pipeline buffers from becoming inconsistent with the data stored in memory.

The program, erase, and validate sector commands require two write cycles, whereas the remaining commands require only one write cycle.

After a program, erase, or validate sector command has been written to the flash module, the module waits indefinitely for the second write cycle to latch the address and/or data; therefore, the valid data write cycle must have valid data, whether it immediately follows the command or not.

The control port can be used to read or write registers, or bank reads can be performed between the command and the data for the program or erase command.

The BUSY status bit becomes active upon receipt of any command except for the clear status command.

After an erase or program command has been issued, the operation cannot be aborted except by resetting the flash module. The operation can, however, be allowed to complete or be suspended. A suspended operation, likewise, can only be aborted by resetting the flash module.

#### 4.4.1 CPU Operations Required for Executing Commands

Before the MCU F05 Platform Flash-ECC can execute a command, the host CPU must do the following:

- Select the desired bank to be programmed by writing BANK[2:0] of FMMAC2

- 2) Select one or more bits in FMBSEA or FMBSEB to disable Level 1 protection for the particular sector to be erased/written

- 3) Write the correct four 32-bit FMPKEY words (if applicable)

- 4) Clear the READOTP bit in the FMREGOPT register

- 5) Write an operand, as shown in Table 5, to any location in flash memory which initiates the operation

For operations that apply to specific address locations (program, erase, and validate) the host must also:

6) Write the desired data half-word to the appropriate address in the selected flash bank

After these operations have been completed in sequence, the command is performed. These flash commands are described in the following sections in more detail.

#### 4.4.2 Program Sector Command

If not already set up, the host must follow the procedure outlined in Section 4.4.1 above. Writing the program operand, as shown in Table 5, to any location in flash memory initiates the program operation. This must be followed by writing the desired data half-word to the appropriate address in the selected flash bank.

#### Note: Program Data to the Flash Module in Half-Words

All data programmed into the MCU F05 Platform Flash-ECC must be done one half-word (16 bits) at a time.

The flash module checks the sector protection status and, if allowed, proceeds to program and verify the data. Once the command is received, the busy flag is held active.

While the busy flag is active, the flash module responds only to the suspend command. If an attempt is made to read a bank being programmed, invalid data is returned. Reads may be performed correctly on other banks. If the program operation is suspended and the suspended bank is read, then only data other than the address that was being programmed should be assumed valid.

If the program operation is suspended, the busy flag becomes inactive within  $2.0\mu s$  of receiving the suspend command.

During the program operation,  $3.3V V_{DD}$  must remain within the appropriate range; otherwise, the error flag 3VSTAT is set in the status register FMMSTAT.3.

When the program command is complete, the user should parse the Status register to verify that the command was successful. Upon completion, the flash module resets the CSM state to Idle mode; therefore, the program command must be reissued before another half-word is written to flash memory.

#### 4.4.3 Erase Sector Command

If it is not already set up, the host must follow the procedure outlined in Section 4.4.1. Writing the erase operand, as shown in Table 5, to any location in flash memory, initiates the erase operation. This is followed by writing any data to the selected sector address (an address anywhere within the sector to be erased), in the flash memory.

The flash module checks the sector enable status and, if allowed, proceeds to erase and verify the data. Once the command is received, the busy flag is held active.

While the busy flag is active, the flash module responds only to the suspend command. If an attempt is made to read a bank being erased, invalid data is returned. Reads can be performed on other banks. If the erase operation is suspended and the suspended bank is read, then the entire sector's data is assumed invalid. Read data from other sectors and banks is invalid due to the partial erasure of this sector.

If the erase operation is suspended, the busy flag becomes inactive within 2.0μs of receiving the suspend command.

Upon completion of the erase command, the user should parse the Status register to verify that the command was successful.

During the erase operation,  $3.3V V_{DD}$  must remain within the appropriate range; otherwise, the error flag 3VSTAT is set in the status register FMMSTAT.3.

When the erase operation is complete, the flash module resets the CSM state to Idle mode; therefore, the erase command must be reissued before another sector can be erased.

#### 4.4.4 Suspend/Resume Commands

The suspend command allows erase or program operations, whichever is active, to be suspended so other operations can be performed on the affected bank. It is also possible to suspend a program operation so that a sector in a different bank can be erased, or suspend an erase operation so that information may be programmed in a different bank. The suspend command is acted upon only if the BUSY bit of FMMSTAT is high and the flash module is performing an erase or program operation. Issuing a suspend command when BUSY is low has no effect on the flash module.

#### Note: Flash Module Ignores All But Suspend Command When BUSY Bit is High

If a command other than suspend is issued while the BUSY bit is high, it is ignored.

It is possible to suspend an operation at certain points in the operation of the state machine so that the operation actually finishes and the suspend flags are never set. Issuing a resume command when suspend is not active has no effect on the flash module.

Only one operation can be active at a time. Also, a program operation cannot be initiated while a previous program operation is suspended, and an erase operation cannot be initiated while a previous erase operation is suspended. The flash module ignores any command that violates these conditions.

#### 4.4.5 Clear Status Command

The Status register allows the user to determine whether an erase/program operation is successfully completed, in progress, suspended, or failed.

If not already set up, the host must follow the procedure outlined in Section 4.4.1. Writing the clear status operand, as shown in Table 5, to any location in flash memory, executes the clear status operation.

If the BUSY bit is low, this operation clears the following status bits: SLOCK (sector locked), CSTAT (command status), 3VSTAT (3.3V  $V_{DD}$  status), INVDAT (invalid program data) in the FMMSTAT register.

#### 4.4.6 Program OTP Command

The flash module may have one or more OTP sectors, up to one OTP sector per flash bank. A minimum of one is required for production and test purposes. Each OTP sector contains 2K bytes. The bits can be programmed via the program OTP command. Once the command is issued, the bank identifier, address within the OTP sector, and the data must be specified.

The program OTP flow is the same as the program half-word flow. It can be suspended and resumed.

### 4.4.7 Validate Sector Command

A validate sector command has been provided to enable the host to determine if a sector contains depleted bits. A depleted bit may occur only in the unlikely event that an erase operation has been started, but not completed. The following conditions could leave depleted bits in a sector:

□ An erase is in progress when power is removed

□ An erase suspend is active when power is removed

□ A flash module reset interrupts an erase operation

□ A flash module reset occurs while an erase suspend is active

After a flash module reset, including power up, the host should perform a validation check on sectors which may have been corrupted to check that no sectors contain depleted bits. It is not required to check sectors which are not programmed in the field, as they cannot have depleted bits. It is, however, possible for depleted bits in one sector to cause bits in another sector to read incorrectly; therefore, it is vital that depleted bits be corrected.

### Note: There Is No Suspend for the Validate Sector Command

The validate sector command cannot be suspended.

## 4.5 Data Security

Data security against either accidental or deliberate access by unauthorized agents is built into the flash module in two levels of data security: Level 1 security allows each sector to be individually protected from any access other than read; level 2 security protects the entire module from non-read access using four optional 32-bit protection keys.

#### 4.5.1 Sector Enable

Sector enable (registers BSEA and BSEB) is a means of preventing data from being modified within a sector. Since the flash module may store permanent and/or semi-permanent program code and/or data this capability is provided. A sector is protected if data within that sector is prevented from being modified (the sector-enable bit for that sector is cleared). Currently the MCU F05 Platform Flash-ECC supports a maximum of 32 sectors per bank.

Flash memory can be programmed or erased only if the specified sector is enabled. If the sector is protected, then the state machine of the flash module halts and sets the status bit SLOCK in FMMSTAT.0.

At power up, all of the sector-enable bits are initialized so that the flash memory location cannot be modified. Sector enable is a feature used only by the flash module when erasing or programming flash memory.

When an erase or program operation resumes from a suspended state, the sector-enable bit is checked again as though it were a new erase or program command.

## 4.5.2 Four-Word Protection Keys

If this option is present, the CPU reads the four stored protection keys out of the flash bank one at a time and into a register in the flash module. After the CPU loads each key from the bank to the control logic, the CPU must load an identical user key into the FMPKEY control register. The CPU must load and match all four keys before any program or erase command can be sent to the flash module.

To enable the module for programming, the CPU must load each stored key value from the bank to the control logic by performing a normal read access to one of the four protection key addresses in the Flash module. The CPU must then load the matching user key value into the FMPKEY register. This process is repeated until all four keys are loaded and matched. The control logic monitors which keys have been matched, so the CPU can not gain write access until it loads and matches all four keys at least once without any intervening mismatch.

If the CPU writes a mismatching key at any time (that is, if the user key does not match the key that was most recently loaded from the bank to the control logic), then all key match states are cleared and the CPU must *reload and rematch all four keys again* to gain write access to the module. This feature can be used to disable write access after programming is completed.

After the CPU has successfully loaded and matched all four keys, flash write access is enabled and the PROTL2DIS flag (FMBBUSY.15) is set until either

a device reset occurs or until the CPU writes a mismatching key to the FMPKEY register.

To store the key values, the CPU programs the key data into the bank by performing normal program and erase operations on these four protection key addresses. The key values are stored in the bank as ordinary data, so the CPU must provide the correct keys before it can perform any program or erasure of the key values.

When a new device is delivered to the customer, the keys will be all ones, so keys of all ones should be used to enable flash writes for the first time. Once the keys are changed in the Flash bank, the CPU must deliberately write a mismatching key value to FMPKEY in order to disable further programming until the new key values have been loaded and matched. In other words, the flash module remains enabled for the remainder of this programming session even though the keys have been modified in flash.

The difference between flash protection key read accesses and other reads is that the key data does not propagate to the CPU data bus *until the correct keys are written* and the user has taken all required steps to gain programming access. This is intended to prevent unauthorized discovery of the stored keys by reading them out via the CPU: only a user who already knows the keys can gain access to them.

The availability of this protection feature and the location of the four protection keys depend on the specific device being used (as specified in the specific TMS470R1x device data sheet). If this feature is not available, then the four protection key addresses in the module are available for normal memory access.

## 4.6 Automatic Power-down of Flash Banks

The flash module provides a mechanism to automatically power down flash banks after they have not been accessed for some user programmable time. Special timers automatically sequence the power up and power down of each bank independently of each other. The charge pump module has its own independent power up/down timers.

During global low power mode when SYS\_LPM=1 the flash module which includes the wrapper logic, banks, and pump module are put into sleep mode. If there is an operation such as a write then the flash module waits until the operation to finish before it enters sleep mode. Flash wrapper uses nLP\_RDY handshake signal to indicate it is ready.

When SYS\_LPM signal goes low again the banks and pump module will go through the normal power up sequence from sleep to active power state. CPU

access to the flash module during the power up sequence will be held in wait state.

### 4.6.1 Active Grace Period

Active grace period (AGP) is a feature which the host can use to optimize the flash module power consumption/access time trade-off. Faster access times are associated with higher power modes of operation. At one extreme, the power control logic could attempt to reduce power consumption by putting the banks and charge pump into a low-power mode immediately at the end of every flash access; however, if accesses are a few cycles apart, this can actually increase power consumption over if the flash had remained powered, because the banks and charge pump consume more power during flash startup and access.

Active grace periods (supported for each bank independently in addition to the charge pump module) allow the banks and/or charge pump to be maintained in active mode for a specified period following an access. This is done in anticipation of another read within the AGP time, to allow the subsequent read to have a faster access and spend less time dissipating power than if the bank went into one of the low power modes immediately. On the other hand, if the next access does not occur within the AGP time, the power control logic can automatically put the bank and/or charge pump into a low-power mode to reduce power consumption during long periods of inactivity.

AGP is realized by a set of host-programmable counters which keep the flash bank or charge pump in active mode until the counter expires, at which time the bank or charge pump reverts to its fallback power mode. See register descriptions for FMBAC1, FMBAC2, FMMAC1, FMMAC2, and FMPAGP.

The bank and/or charge pump are kept active in anticipation of another read. Assuming AGP is being utilized, the bank AGP counter is set, keeping the bank active, while an access is in progress. The counter begins counting when no more accesses are in progress. If the AGP timers have not timed out and another access occurs then there is a substantial performance gain compared to the access when the bank is not active (either the bank is in standby or Sleep mode). If the AGP counter times out, the bank or charge pump is put into a host programmable fallback power mode. The host can program the fallback power mode to be standby or sleep mode to reduce power consumption, or program it to be active mode to keep the bank active regardless of counter settings (default).

The ECC bank power control logic is identical to other banks in which different fallback power mode can be selected. It is possible to have flash data banks in different fallback power mode than the ECC bank. When an access is made to a flash bank, the flash wrapper power control logic will wait for both the

addressed bank and the ECC bank to become active before returning the data to the CPU if EDACEN is enabled.

The charge pump AGP counter remains in its initialized state when any one of the banks is active, including the AGP counter of the bank. The charge pump AGP counter begins counting when all banks have become inactive.

The bank and charge pump active grace period counters count at SYSCLK frequency.

#### 4.6.2 Power Mode Control

The primary contributors to flash module power consumption are the flash banks, and the charge pump. This section deals with how the flash wrapper handles the control of the different power modes of the flash banks and charge pump.

A couple of the components of the module power reduction have been discussed. These are the bank fallback power bits in the FMBAC1 register, the charge pump fallback power bits in the FMMAC2 register, and the BAGP and PAGP operation. The fallback power control bits contain the bank and charge pump modes, which become active upon time-out of the AGP counters described in Section 4.6.2. Any access to a flash bank causes the bank and charge pump to go into active mode, regardless of their current state. Also, any erase, program, or validate sector command causes the charge pump to become active.

If the charge pump is in sleep mode when the flash access begins, the power mode control logic automatically sequences the charge pump to standby mode, then to active mode. Also, if any bank is active or in standby mode, the charge pump is active, independent of the charge pump fallback power mode.

The host can override the power control functions of the flash module by setting all of the AGP counters to zero. In this case, the power mode control logic still sequences the pump through standby mode automatically if needed, and it activates the pump automatically if any bank is put into any power mode other than sleep mode.

## 4.7 Wait States

The number of wait states can vary depending on the type of read access performed. The different types of read accesses are defined below:

Initial Access - First address read after initialization of the flash. Typically after reset.

- Sequential Access Instruction accesses the very next flash address from the previous instruction's flash address.

- Random Access Instruction accesses a non-sequential flash address from the previous instruction's address.

Wait states are added to a read access when either the flash bank or charge pump are not active, or when the flash bank can not have data valid at the frequency demanded by the host. The flash module generates an internal ready signal for each bank based on the values in the wait state registers which depend on the status of the bank, the charge pump, and the data rate.

The bank has three wait state generators and the pump has two wait state counters. Both the bank and the charge pump have standby and sleep counters which are initialized when a transition is made from non-active mode to active mode. The bank also has a wait state counter to allow for a faster clock than the flash data rate. All wait state generators are clocked by the flash system clock.

The outputs of the charge pump counters and bank counters are combined. The resulting signal generates the wait states and ready signal of each bank when an access is in progress.

## 4.8 VDD3V Out of Range Check

The VDD3V out of range status bit informs the host if there was a low supply during an erase or program operation. A comparator in the charge pump module sets the 3VSTAT bit if the 3.3V supply is less than 2.4V for more than three SYSCLK cycles; otherwise it is cleared.

## 5 Control Registers

This section covers the MCU F05 Platform Flash-ECC control register memory map and a basic description of each register and its bits.

## 5.1 Memory Map

The MCU F05 Platform Flash-ECC uses several registers to control the various modes of operation, numbers of wait states, and bank selection. All user flash registers are shown in Table 6 and Table 7. The addresses shown are relative offsets from the base address, which depends upon the device being used. See the specific TMS470R1x device data sheet for the register base address.

| Offset<br>Address† | Register | 31 30<br>15              | 29<br>14 1              | 28<br> 3 12 |             |           |            | 24<br>8    | 23<br>7                     |       |             |             | 19<br>  3   | -        | 17<br>1 | 16<br>0 |

|--------------------|----------|--------------------------|-------------------------|-------------|-------------|-----------|------------|------------|-----------------------------|-------|-------------|-------------|-------------|----------|---------|---------|

|                    | FMRE-    |                          |                         |             |             |           |            | Re         | served                      |       |             |             |             |          |         |         |

| 0x0100             | GOPT     |                          | Reserved                |             |             |           |            |            |                             | SPOTP | RD<br>MRGN1 | RD<br>MRGN0 | READ<br>OTP | ENPIPE   |         |         |

| 0x0108             | FMBBUSY  | PROTL<br>2DIS            | 2DIS Reserved BOST[7:0] |             |             |           |            |            |                             |       |             |             |             |          |         |         |

| 0x010C             | FMPKEY   |                          | PKEY[31:16]             |             |             |           |            |            |                             |       |             |             |             |          |         |         |

| 0,0100             |          |                          | PKEY[15:0]              |             |             |           |            |            |                             |       |             |             |             |          |         |         |

|                    | FMEDACC  |                          |                         |             |             |           |            |            | eserved                     |       | 80          |             |             |          |         |         |

| 0x0110             | TRL1     | R                        | leserved                |             | ECC-<br>MAP | EOFEN     | EZF<br>EN  | EP<br>EN   | Reserv                      | ved   | EO<br>CV    | EZ<br>CV    |             | EDACE    | N[3:0]  |         |

| 0x0114             | FMEDACC  |                          |                         |             |             |           |            |            | eserved                     |       |             |             |             |          |         |         |

| 0,0114             | TRL2     |                          | SEC_THRESHOLD[15:0]     |             |             |           |            |            |                             |       |             |             |             |          |         |         |

| 0x0118             | FMEDAC-  |                          |                         |             |             |           |            |            | eserved                     |       |             |             |             |          |         |         |

| 0,0118             | CNT      |                          |                         |             |             |           |            | SEC_C      | DCCR[15:0                   | 0]    |             |             |             |          |         |         |

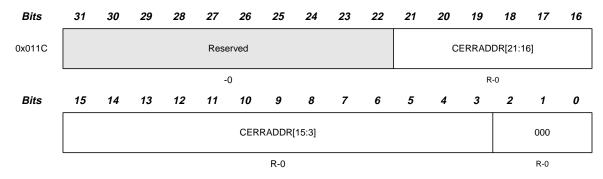

| 0x011C             | FMCER-   | Reserved CERRADDR[23:16] |                         |             |             |           |            |            |                             |       |             |             |             |          |         |         |

| 0,0110             | RADDR    |                          |                         |             |             |           |            | CERRA      | ADDR[15:                    | 0]    |             |             |             |          |         |         |

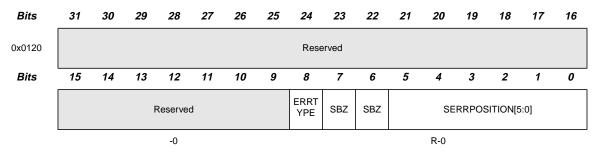

|                    | FMCER-   |                          |                         |             |             |           |            |            | eserved                     |       |             |             |             |          |         |         |

| 0x0120             | RPOSI-   | Reserved                 |                         |             |             |           |            | ERR<br>TYP | 0 0 SERRPOSITION[5:0]       |       |             |             |             |          |         |         |

|                    | TION     |                          |                         | Е           |             |           |            |            |                             |       |             |             |             |          |         |         |

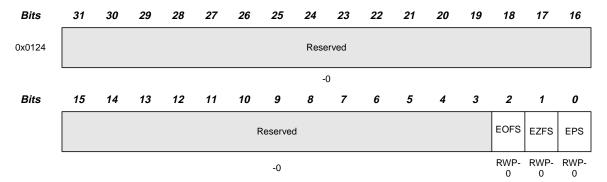

| 0x0124             | FMEDAC-  |                          |                         |             |             |           |            | R          | eserved                     |       |             |             |             | ЕО       |         | -       |

| 0.0124             | STATUS   |                          | Reserved                |             |             |           |            |            |                             |       |             |             | FS          | EZ<br>FS | EPS     |         |

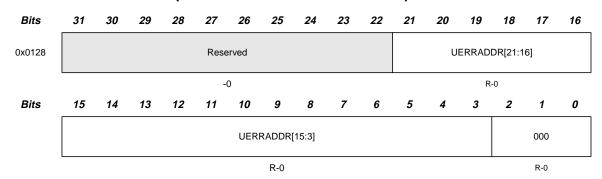

| 0x0128             | FMUER-   |                          |                         | R           | Reserved    |           |            |            |                             |       | ι           | JERRADE     | DR[23:16]   |          |         |         |

| 0x0128             | RADDR    |                          |                         |             |             |           |            | UERRA      | ADDR[15:                    | 0]    |             |             |             |          |         |         |

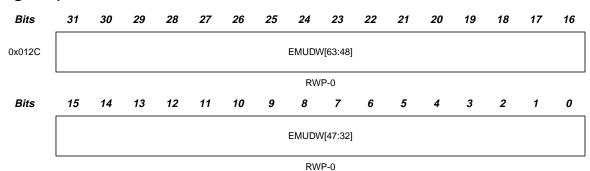

| 0x012C             | FMEMU    |                          |                         |             |             |           |            | EMU        | DW[63:48                    | ]     |             |             |             |          |         |         |

| 00120              | DMSW     |                          |                         |             |             |           |            | EMU        | DW[47:32                    | ]     |             |             |             |          |         |         |

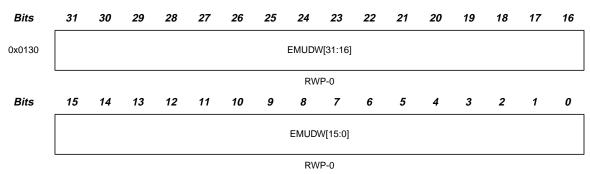

| 0x0130             | FMEMU    |                          |                         |             |             |           |            | EMU        | DW[31:16                    | ]     |             |             |             |          |         |         |

| 0.0130             | DLSW     |                          |                         |             |             |           |            | EMU        | DW[15:0]                    |       |             |             |             |          |         |         |

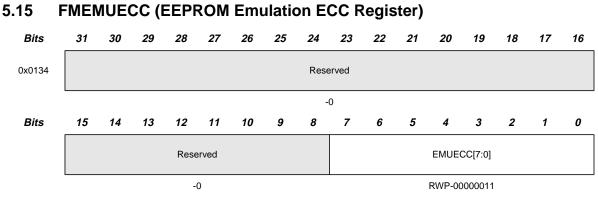

| 0x0134             | FMEMU    |                          |                         |             |             |           |            | R          | eserved                     |       |             |             |             |          |         |         |

| 0X0134             | ECC      |                          |                         | R           | Reserved    |           |            |            |                             |       |             | EMUEC       |             |          |         |         |

| 0x0138             | FMSEC-   | bankID1_inv              | verse[2:0]              |             | Sect        | orID1_inv | erse[4:0]  |            | bankID1[2:0] SectorID1[4:0] |       |             |             |             |          |         |         |

| 0,0130             | DIS      | bankID0_inv              | verse[2:0]              |             | Sect        | orID0_inv | erse[4:0]  |            | bankID0[2:0] SectorID0[4:0] |       |             |             |             |          |         |         |

| 00100              | FMDIAGC- |                          |                         |             |             |           |            |            | eserved                     |       |             |             |             |          |         |         |

| 0x013C             | TRL      |                          | R                       | eserved     |             |           | DU-<br>ERR | DCE<br>RR  | Reserved                    |       |             |             |             |          | DIAGM   | 10DE    |

| Offset<br>Address | Register | 15                                  | 14                    | 13 | 12 | 11 | 10 | 9    | 8   | 7   | 6          | 5     | 4          | 3     | 2     | 1    | 0 |

|-------------------|----------|-------------------------------------|-----------------------|----|----|----|----|------|-----|-----|------------|-------|------------|-------|-------|------|---|

| 0x0000            | FMBAC1   | BAGP BSTDBY                         |                       |    |    |    |    |      |     |     |            |       | BNKPWR     |       |       |      |   |

| 0x0004            | FMBAC2   | OTP<br>PROT<br>DIS                  | PROT BSLEEP WAIT WAIT |    |    |    |    |      |     |     |            |       | AIT        |       |       |      |   |

| 0x0008            | FMBSEA   |                                     | BSEA                  |    |    |    |    |      |     |     |            |       |            |       |       |      |   |

| 0x000C            | FMBSEB   |                                     | BSEB                  |    |    |    |    |      |     |     |            |       |            |       |       |      |   |

| 0x0010            | FMBRDY   | Reserved BANK Reserved RDY Reserved |                       |    |    |    |    |      |     |     | ł          |       |            |       |       |      |   |

| 0x0014            | FMPRDY   | Reserved PUMP<br>RDY                |                       |    |    |    |    |      |     |     | Reserved   |       |            |       |       |      |   |

| 0x0018            | FMMAC1   | PROTL1<br>DIS                       |                       |    |    |    |    |      |     |     |            |       |            |       |       |      |   |

| 0x001C            | FMMAC2   | PSTDBY PMPPWR BANK                  |                       |    |    |    |    |      |     |     |            |       |            |       |       |      |   |

| 0x0020            | FMPAGP   |                                     | PAGP                  |    |    |    |    |      |     |     |            |       |            |       |       |      |   |

| 0x0024            | FMMSTAT  | Reserved                            |                       |    |    |    |    | BUSY | ERS | PGM | INV<br>DAT | CSTAT | 3V<br>STAT | ESUSP | PSUSP | SLOC |   |

## Table 7.16-bit Flash Memory Registers

## 5.2 Register Access

The flash module control registers can only be read and/or written by the CPU while in privilege mode.

Byte, half-word and word writes are supported to all registers. Remember that half-word access and byte access are affected by big or little endian configuration.

Note: All reserved fields will read as zeros.

## 5.3 Option Control Register (FMREGOPT)

FMREGOPT is a word-access only register. It supports OTP sector access, margin testing, and pipeline mode. There is only one FMREGOPT register for the entire MCU F05 Platform Flash-ECC.

| Bit    | 31 5     | 4            | 3     | 2           | 1           | 0          |

|--------|----------|--------------|-------|-------------|-------------|------------|

| 0x0100 | Reserved | Reserve<br>d |       | RD<br>MRGN0 | READ<br>OTP | EN<br>PIPE |

|        | 0        | RWP-0        | RWP-0 | RWP-0       | RWP-0       | RWP-d      |

RW: Read/Write in all modes, U: Undefined, -0: Value after reset, -d: Device specific value

| Bits 31:5 | Reserved                                                                                                                                                                                                                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Read values are zeros. Writes have no effect.                                                                                                                                                                                                                                                                 |

| Bit 4     | Reserved                                                                                                                                                                                                                                                                                                      |

|           | This bit is reserved for TI's use. <b>Do not set this bit</b> as it will cause the user OTP sector to be disabled even when otherwise enabled by READOTP.                                                                                                                                                     |

| Bit 3     | RDMRGN1. Read Margin 1.                                                                                                                                                                                                                                                                                       |