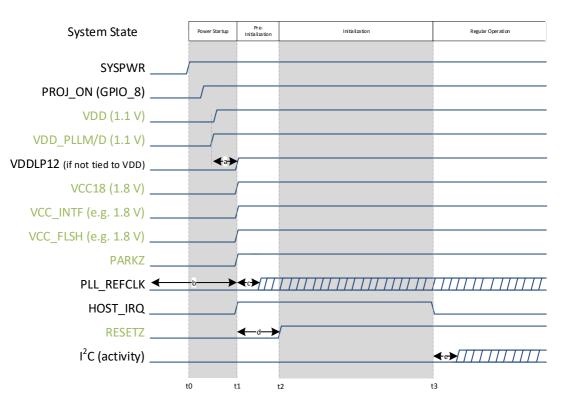

## System Power-Up Timing Diagram

t0: SYSPWR applied to the PMIC. All other voltage rails are derived from SYSPWR

t1: All supplies reach 95% of their specified nominal value.

t2: Point where RESETZ is deasserted (goes high). This indicates the beginning of the controller auto-initialization routine.

t3: HOST\_IRQ goes low to indicate initialization is complete.

a. VDDLP12 must be powered on after VDD if it is supplied from a separate source

b. PLL\_REFCLK is allowed to be active before power is applied

c. PLL\_REFCLK must be stable within 5ms of all power being applied. For external oscillator applications this is oscillator dependent, and for crystal applications this is crystal and controller oscillator cell dependent.

d. PARKZ must be high before RESETZ releases to support auto-initialization

e. I<sup>2</sup>C activity cannot start until HOST\_IRQ goes low to indicate auto-initialization is complete

Color Code: From PMIC (e.g. DLPA3000) From other source