# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8548E. This device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

## 2.1 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

Table 1. Absolute Maximum Ratings <sup>1</sup>

|                                                                                                                        | Characteristic                                                                                                  | Symbol                                   | Max Value                                                            | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply voltage                                                                                                    |                                                                                                                 | V <sub>DD</sub>                          | -0.3 to 1.21                                                         | V    | _     |

| PLL supply voltage                                                                                                     |                                                                                                                 | AV <sub>DD</sub>                         | -0.3 to 1.21                                                         | V    | _     |

| Core power supply for SerDes transceivers                                                                              |                                                                                                                 | SV <sub>DD</sub>                         | -0.3 to 1.21                                                         | V    | _     |

| Pad power supply for SerDes transceivers                                                                               |                                                                                                                 | XV <sub>DD</sub>                         | -0.3 to 1.21                                                         | V    | _     |

| DDR and DDR2 DRAM I/O voltage                                                                                          |                                                                                                                 | GV <sub>DD</sub>                         | -0.3 to 2.75<br>-0.3 to 1.98                                         | V    | _     |

| Three-speed Ethernet I/O voltage                                                                                       |                                                                                                                 | LV <sub>DD</sub> (for eTSEC1 and eTSEC2) | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | 3     |

|                                                                                                                        |                                                                                                                 | TV <sub>DD</sub> (for eTSEC3 and eTSEC4) | -0.3 to 3.63<br>-0.3 to 2.75                                         |      | 3     |

| PCI/PCI-X, DUART, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG I/O voltage |                                                                                                                 | OV <sub>DD</sub>                         | -0.3 to 3.63                                                         | V    | _     |

| Local bus I/O voltage                                                                                                  |                                                                                                                 | BV <sub>DD</sub>                         | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | _     |

| Input voltage                                                                                                          | DDR/DDR2 DRAM signals                                                                                           | MVIN                                     | -0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 4     |

|                                                                                                                        | DDR/DDR2 DRAM reference                                                                                         | MV <sub>REF</sub>                        | -0.3  to (GV <sub>DD</sub> /2 + 0.3)                                 | V    | _     |

|                                                                                                                        | Three-speed Ethernet I/O signals                                                                                | LV <sub>IN</sub><br>TV <sub>IN</sub>     | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 4     |

|                                                                                                                        | Local bus signals                                                                                               | BV <sub>IN</sub>                         | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | _    | _     |

|                                                                                                                        | DUART, SYSCLK, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG signals | OV <sub>IN</sub>                         | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 4     |

|                                                                                                                        | PCI/PCI-X                                                                                                       | OV <sub>IN</sub>                         | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 4     |

Table 1. Absolute Maximum Ratings <sup>1</sup> (continued)

| Characteristic            | Symbol           | Max Value  | Unit | Notes |

|---------------------------|------------------|------------|------|-------|

| Storage temperature range | T <sub>STG</sub> | -55 to 150 | °C   | _     |

#### Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 3. The 3.63 V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75 V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 4. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for this device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

**Table 2. Recommended Operating Conditions**

|                                                                                                                        | Characteristic                                                                                                       | Symbol                               | Recommended<br>Value                               | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply voltage                                                                                                    |                                                                                                                      | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    | _     |

| PLL supply volta                                                                                                       | ge                                                                                                                   | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supply for SerDes transceivers                                                                              |                                                                                                                      | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | _     |

| Pad power supply for SerDes transceivers                                                                               |                                                                                                                      | $XV_{DD}$                            | 1.1 V ± 55 mV                                      | V    | _     |

| DDR and DDR2 DRAM I/O voltage                                                                                          |                                                                                                                      | GV <sub>DD</sub>                     | 2.5 V ± 125 mV<br>1.8 V ± 90 mV                    | V    | _     |

| Three-speed Ethernet I/O voltage                                                                                       |                                                                                                                      | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                                                                                                        |                                                                                                                      | TV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | _    | 4     |

| PCI/PCI-X, DUART, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG I/O voltage |                                                                                                                      | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus I/O voltage                                                                                                  |                                                                                                                      | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | _     |

| Input voltage                                                                                                          | DDR and DDR2 DRAM signals                                                                                            | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                                                                                                        | DDR and DDR2 DRAM reference                                                                                          | MV <sub>REF</sub>                    | GND to GV <sub>DD</sub> /2                         | V    | 2     |

|                                                                                                                        | Three-speed Ethernet signals                                                                                         | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                                                                                                        | Local bus signals                                                                                                    | BV <sub>IN</sub>                     | GND to BV <sub>DD</sub>                            | V    | _     |

|                                                                                                                        | PCI, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

Table 2. Recommended Operating Conditions (continued)

| Characteristic             | Symbol | Recommended<br>Value | Unit | Notes |

|----------------------------|--------|----------------------|------|-------|

| Junction temperature range | Tj     | 0 to 105             | °C   | _     |

#### Notes:

- 1. This voltage is the input to the filter discussed in Section 21.2, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, which may be reduced from V<sub>DD</sub> by the filter.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. Caution: L/TV<sub>IN</sub> must not exceed L/TV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

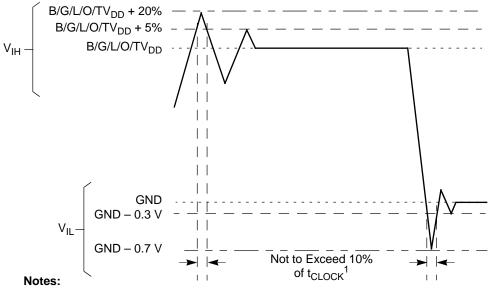

Figure 2 shows the undershoot and overshoot voltages at the interfaces of this device.

- 1. t<sub>CLOCK</sub> refers to the clock period associated with the respective interface:

- For I<sup>2</sup>C and JTAG, t<sub>CLOCK</sub> references SYSCLK. For DDR, t<sub>CLOCK</sub> references MCLK. For eTSEC, t<sub>CLOCK</sub> references EC\_GTX\_CLK125.

- For LBIU, t<sub>CLOCK</sub> references LCLK.

- For PCI, t<sub>CLOCK</sub> references PCI*n*\_CLK or SYSCLK. For SerDes, t<sub>CLOCK</sub> references SD\_REF\_CLK.

- 2. Note that with the PCI overshoot allowed (as specified above), the device does not fully comply with the maximum AC ratings and device protection guideline outlined in the PCI rev. 2.2 standard (section 4.2.2.3).

Figure 2. Overshoot/Undershoot Voltage for  $GV_{DD}/OV_{DD}/LV_{DD}/BV_{DD}/TV_{DD}$

The core voltage must always be provided at nominal 1.1 V. Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage. OV<sub>DD</sub> and LV<sub>DD</sub> based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced the externally supplied MV<sub>REF</sub> signal (nominally set to GV<sub>DD</sub>/2) as is appropriate for the SSTL2 electrical signaling standard.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7

### 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

**Programmable** Supply **Output Impedance Notes Driver Type** Voltage  $(\Omega)$ Local bus interface utilities signals 25  $BV_{DD} = 3.3 V$ 1 25  $BV_{DD} = 2.5 V$  $BV_{DD} = 3.3 V$ 45(default) 45(default)  $BV_{DD} = 2.5 V$  $OV_{DD} = 3.3 \text{ V}$ PCI signals 25 2 45(default)  $GV_{DD} = 2.5 V$ DDR signal 36 (half strength mode) DDR2 signal  $GV_{DD} = 1.8 V$ 3 36 (half strength mode) TSEC/10/100 signals 45  $L/TV_{DD} = 2.5/3.3 V$ DUART, system control, JTAG 45  $OV_{DD} = 3.3 V$ I<sup>2</sup>C 150  $OV_{DD} = 3.3 V$

**Table 3. Output Drive Capability**

#### Notes:

- 1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

- 2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

- 3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105$ °C and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1.  $V_{DD}$ ,  $AV_{DD\_}n$ ,  $BV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ ,  $SV_{DD}$ ,  $TV_{DD}$ ,  $XV_{DD}$

- 2. GV<sub>DD</sub>

All supplies must be at their stable values within 50 ms.

### **NOTE**

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

### **NOTE**

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 7