# Over Voltage Protection Circuit for Automotive Load Dump

National Semiconductor Application Note 1533 Tom Mathews December 2006

#### Introduction

Transient buss voltages are a serious danger to integrated circuits. The maximum voltage that an integrated circuit can handle depends upon its design process and can be particularly low for small geometry CMOS devices. Transient or persistent over voltage conditions that exceed an IC's absolute maximum voltage rating will permanently damage a device. The need for over voltage protection is particularly

common in automotive 12V and 24V systems where peak "load dump" transients can be as high as 60V. Some load protection approaches shunt input transient to ground using devices like avalanche diodes and MOVs. The difficulty with the shunt approach is that large amounts of energy may have to be absorbed. Shunt approaches can also be unattractive if there is a requirement to provide continuous protection while in an over voltage condition (as occurs with double battery).

#### The Circuit

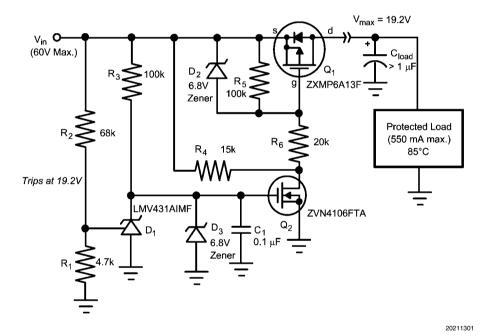

The circuit shown in *Figure 1* is a precision series disconnect that was designed to protect a switching regulator load that had an absolute maximum input voltage of 24V. The circuit is

designed from low cost discrete devices and uses a single National Semiconductor LMV431AIMF (\$0.22 in 1k qty.).

**FIGURE 1. Over Voltage Protection**

Since this circuit uses a PFET pass device  $(\mathbf{Q}_1)$ , there is little forward voltage drop or associated power loss.

The LMV431AIMF ( $D_1$ ) adjustable reference is ideal for this problem because it provides a low cost means to determine a precision trip point and maintain temperature stability that is not possible with a zener diode or with other approaches (1% for the A version, 0.5% for the B version). In order to preserve this precision, resistors  $R_1$  and  $R_2$  should be 1% tolerance or better.

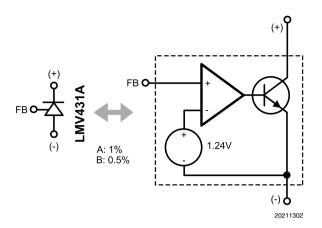

Adjustable references are often misunderstood. As in: "What's that third wire coming out of that diode?" There are

many flavors of adjustable reference. Some have different internal reference voltage and some have different gain polarity. They all have two basic (and very useful) components: A temperature stable, precision band gap reference, and a high gain error amplifier (used as a comparator in this circuit). Most devices have uni-polar output in the form of an open collector or emitter. *Figure 2* shows conceptually what is inside National Semiconductor's LMV431AIMF.

FIGURE 2. Adjustable Reference Concept

The input voltage is monitored by the LMV431 through voltage divider  $\rm R_1$  and  $\rm R_2$ . The circuit shown in *Figure 1* is set to trip at 19.2V but an arbitrary trip point can be selected and is determined with these equations:

$$V_{trip} = 1.24 \text{ x} \frac{R_1 + R_2}{R_1}$$

$$R_2 = R_1 \times \left( \frac{V_{trip}}{1.24} - 1 \right)$$

The output of the LMV431 pulls down when the reference pin exceeds 1.24V. The cathode of an LMV431 can pull down to a saturation point of about 1.2V. This is sufficient to turn  $\mathbf{Q}_2$  off.  $\mathbf{Q}_2$  was specifically selected to have a high gate threshold (>1.3V). Do not make substitution for Q2 without taking this into account.

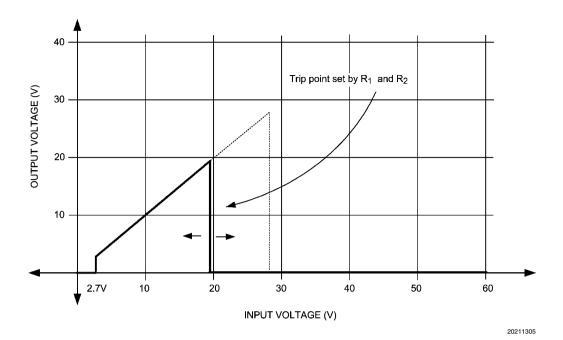

The device states for  $D_1$ ,  $Q_2$ , and  $Q_1$  are shown here in *Figure 3* for the case of a 19.2V trip point.

|               | LMV431<br>Q1 | NFET<br>Q2 | PFET<br>Q1 |

|---------------|--------------|------------|------------|

| < 2.7V        | OFF          | ?          | OFF        |

| 2.7V to 19.2V | OFF          | ON         | ON         |

| > 19.2V       | ON           | OFF        | OFF        |

20211304

FIGURE 3. Truth Table

The circuit's function is shown in *Figure 4*. The trip point can be anywhere in the 2.7V to 60V range. Below about 2.7V the circuit will enter the off state. This is because there is no longer sufficient input voltage to satisfy the gate to source thresholds of  $Q_1$  and  $Q_2$ .

www.national.com 2

**FIGURE 4. Circuit Function**

When in the off state, the circuit presents about 42 k $\Omega$  to the input (off state quiescent load). Zener diodes  $D_2$  and  $D_3$  are necessary to limit the maximum gate to source voltages seen by  $Q_1$  and  $Q_2$  (which cannot exceed 20V).  $D_3$  also prevents the cathode of  $D_1$  from exceeding its maximum of 35V. Resistor  $R_4$  provides a small amount of bias to  $Q_2$  in order to satisfy  $Q_2$ 's drain leakage in the off state. Note that the body diode in  $Q_1$  means that there is no protection to the load for reverse battery (negative input voltages). In order to protect against reverse battery, either a blocking diode or a second (back to back) PFET is required.

The circuit is designed to actuate quickly but reconnect more slowly. Capacitor  $\mathbf{C}_1$  rapidly discharges to ground through the

### **Response Time Measurement**

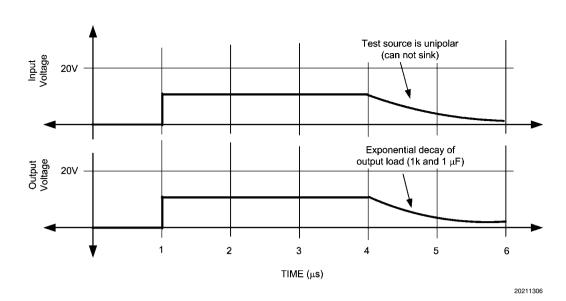

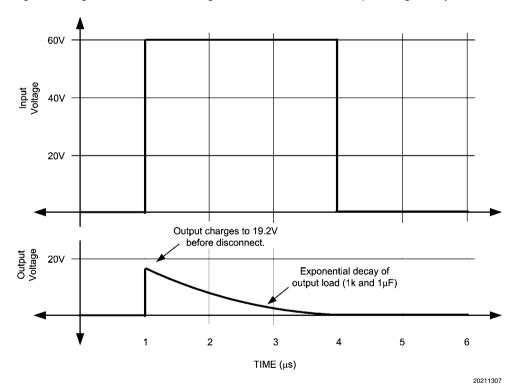

The response to a normal 12V ON and OFF cycle is shown in *Figure 5*. The off portion decays slowly because of the 1  $\mu$ F

LMV431 when over voltage is detected. When conditions return to normal, reconnect is delayed by the R3•C1 time constant. Most loads (usually regulators) contain large input capacitors which provide time for the disconnect circuit to engage by limiting the transient slew rate. The nature of the expected transient along with the available capacitance will determine the required response time. The shut off action of this circuit occurs in about 12 µsec. Maximum transient rise times are limited in proportion to this time interval by  $\rm C_{load}$ . This circuit was tested with a  $\rm C_{load}$  of 1 µF. Larger Cload is allowed and recommended if fast rising, low source impedance transients are expected.

Cload dissipating into the 1  $k\Omega$  test load. The driving waveform also shows this decay because the test source used could not sink current.

FIGURE 5. Normal 12V Operation

The response to an over voltage is shown in Figure 6. Note that the fast rising over voltage event has time to charge the

output to 19.2V where the circuit disconnects. After this, the disconnected output voltage decays into the 1 k $\Omega$  load.

FIGURE 6. Response to 60V step input,  $C_{load}$  = 1  $\mu\text{F}$

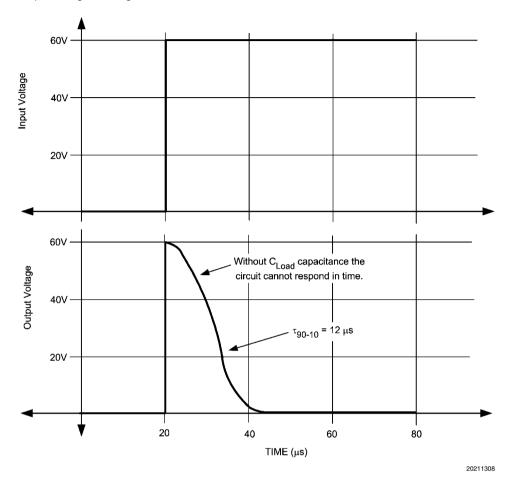

If the 1 $\mu$ F C $_{load}$  capacitor is removed the actuation speed of the disconnect can be observed. This is shown in *Figure 7*. Since the rise time of the input transient isn't limited by any capacitance the output voltage is charged to the full 60V be-

fore action is taken. For this reason,  $C_{\rm load}$  should be sized appropriately for the expected transient rise time and expected transient source impedance.

FIGURE 7. Raw response to 60V input, Cload = 0  $\mu$ F

5

# **Load Limits**

The 550 mA maximum allowed load is set by the thermal limits of Q1 at 85°C. When making this calculation, remember that

$R_{DS(ON)}, on$  is highest when the gate to source voltage is low. For larger loads replace Q1 with a 60V PFET with more thermal capacity (smaller  $\theta_{JA})$  or lower  $R_{DS(ON)}.$

# **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com  $% \left( 1\right) =\left( 1\right) \left( 1$

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560