Hi Experts.

Any chip on the previous CCXXX2 agama platform,

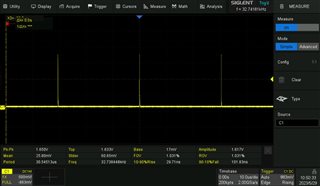

We all use the following program to do 32K test.

//IOCPortConfigureSet(20, IOC_PORT_AON_CLK32K, IOC_STD_OUTPUT);

//AONIOC32kHzOutputEnable();

//while(1);

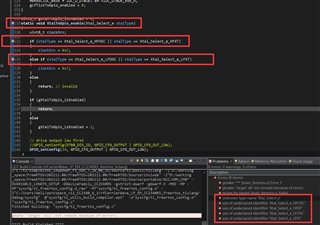

But in CC2340 SDK, there seems to be no AONIOC32kHzOutputEnable function.

Is there any change in the 32K test method in CC2340? Can you tell me how to test 32K in CC2340.

Thanks.