TI システムおよびアプリケーション・マネージャ アナン・カマス(Anant Kamath)

絶縁は、システムの2つの部分の間で信号と電力の伝達をゆるし行いながら、直流(DC)と不要な交流(AC)を阻止します。絶縁は、作業者や低電圧回路を高電圧から保護する他、ノイズ耐性の向上、通信サブシステム間におけるグランド電位差を処理するため、さまざまなアプリケーションで使用されています。

CMOSあるいはTTLレベルの入出力を持ったアイソレータは、デジタル・アイソレータと呼ばれます。デジタル・アイソレータを使用すると、アイソレータとの通信速度が遅い場合や、配線距離が数インチに制限されている場合に、同じPCB上の2つの異なる電圧ドメイン間を絶縁できます。

長い基板配線やケーブルおよびコネクタを介した高速データ通信には、CMOS信号よりも低電圧差動信号(LVDS)の方が適しています。LVDSには、CMOSに比べて低い消費電力や電磁放射、優れた信号整合性(終端処理された伝送経路による低反射)、高いノイズ耐性といった特長があります。絶縁と長い距離にわたる高速相互接続との組み合わせが必要な場合は、絶縁LVDSバッファにより、コンパクトでコスト効率の高いソリューションを実現できます。

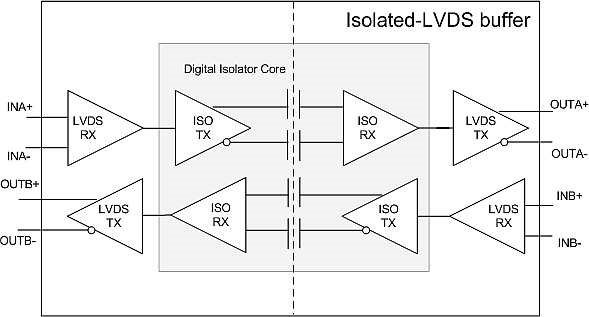

図1には、デュアル・チャネル絶縁LVDSバッファのブロック図の例を示しています。各チャネルは、デジタル・アイソレータ・コアによって接続されたLVDSレシーバとLVDSドライバで構成されています。

図1:デュアル・チャネル絶縁LVDSバッファのブロック図の例

絶縁LVDSアプリケーション

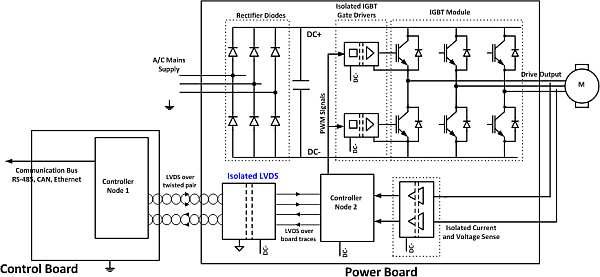

絶縁LVDSバッファは、2つの特定用途向け集積回路(ASIC)やFPGA間でのポイント・ツー・ポイント通信の設計に利用できます。たとえば、高電圧モータ制御アプリケーションでは、ノード1を安全な低電圧またはアース基準の基板上のコントローラとし、ノード2を高電圧にバイアスした電源基板上のコントローラとすることができます。図2に示すように、絶縁LVDSを使用して、高電圧回路と作業者が触れる可能性のある部品の間を絶縁で保護することができます。

LVDSリンクは、パルス幅変調(PWM)信号の集合を絶縁されたIGBT(絶縁ゲート・バイポーラ・トランジスタ)ゲート・ドライバに伝送するほか、インバータからの電圧や電流などの帰還も行います。そのため、絶縁LVDSリンクには高スループットが必要です。また、絶縁LVDSバッファが高電圧ドメインと低電圧ドメインの間にある唯一の保護バリアである場合、そのLVDSバッファには強化絶縁が必要になります。

図2:高電圧モータ・ドライブ・アプリケーションで使用される絶縁LVDS

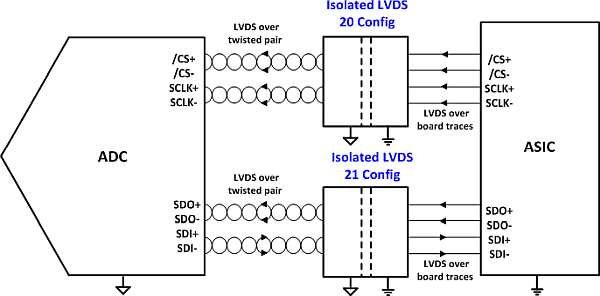

2つ目の例(図3)は、LVDSベースのシリアル・ペリフェラル・インターフェイス(SPI)の作成方法を表しています。この設計でのインターフェイスはアナログ/デジタル・コンバータ(ADC)とASICの間を接続するインターフェイスであり、テストおよび測定アプリケーションに使用されます。2つの絶縁LVDSバッファが使用されており、一方は21構成(各方向に1つのチャネル)、もう一方は20構成(両方のチャネルが同じ方向)となっています。このソリューションは、高電圧に対する保護だけでなく、ノイズと電磁干渉(EMI)への耐性や、グランド・ループ絶縁を備えています。たとえば、ADCで計測アプリケーションのACライン電圧のような高電圧を測定している場合、絶縁LVDSバッファには高い動作電圧と強化絶縁が必要です。

図3:ADCをASICから絶縁するためのSPIインターフェイス

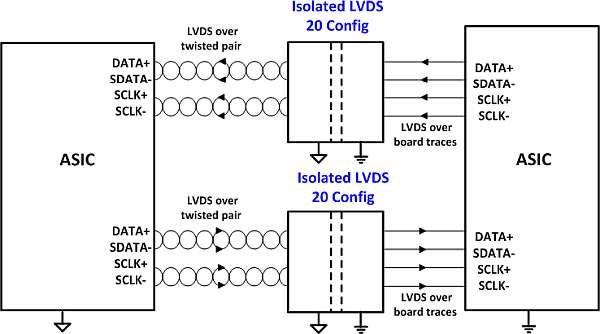

図4に示す3つ目の例は、2つのASIC間でのクロックとデータをベースにした汎用の双方向通信であり、2つの絶縁LVDSバッファを20構成で使用することにより実現しています。

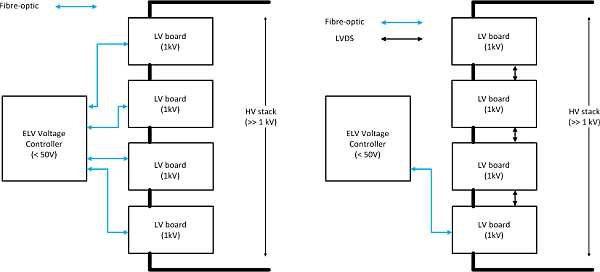

従来は光ファイバ通信に頼っていたようなアプリケーションでも、絶縁LVDSを使用して、高スループットと超高電圧強化絶縁の両方を実現することができます。このようなアプリケーションとしては、1000VRMSを大きく上回るシステム電圧を扱うモータ・ドライブなどがあります。図5に示す概念ブロック図では、高電圧(HV)(1000V超)出力を生成するために複数の低電圧(LV)基板(1000V未満)がスタック接続されています。

従来型の手法では、光ファイバ通信を使用してコントローラと各LV基板が通信し、光ファイバ・リンクによって強化絶縁が提供されています。図5は、システム・コストの削減を目的とした代替アーキテクチャを示しています。強化絶縁のために光ファイバ・チャネルを使用してコントローラと1つのLV基板が通信します。LV基板間の通信は、1000Vの機能絶縁をサポートする絶縁LVDSバッファを使用して行われます。

図5:出力1000V以上の高電圧システム内の光ファイバ通信を絶縁LVDSに置

主な要件と仕様

絶縁LVDSバッファの絶縁仕様は、最終的なアプリケーションと、障害状況下を含む動作時の絶縁バリアにかかる予測電圧によって異なります。これらの要件は、ACモータ・ドライブ向けIEC 61800-5-1安全規格やテストおよび測定アプリケーション向けIEC 61010-1安全規格のような、最終機器の電気的安全規格から導き出すことができます。

たとえば、絶縁LVDSバッファを1000VRMS定格のモータ・ドライブ・アプリケーションで強化絶縁に使用する場合、その絶縁LVDSバッファは4400VRMSで5秒の短時間過電圧仕様、12kVPKのサージまたはインパルス電圧、1500VPKの動作電圧、14mm以上の沿面距離と空間距離を満たす必要があります[1]。ICに使用されるパッケージ材料の比較トラッキング指数(CTI)も重要であり、絶縁する2つの側の間で反復的または継続的な高電圧を処理するアイソレータの能力が、これによって制限されたり強化されたりします。

絶縁LVDSをグランド・ループ絶縁のみに使用する場合は、数百Vの機能絶縁だけで十分です。

LVDSトランスミッタおよびレシーバの電気的特性は、TIA/EIA-644-A LVDS規格によって定められています。この規格に基づくトランスミッタ・ピンでのピーク差動出力は、100Ω抵抗で終端した場合に約400mVとなります。差動レシーバの感度は100mVです。TIA/EIA-644-A規格には、トランスミッタとレシーバの間のケーブル長に対する制限はありませんが、与えられたデータ信号速度での最大ケーブル長を求める方法が提示されています。設計者はケーブル内で発生する抵抗性の電圧降下、ジッタ、クロストークを考慮する必要があります。データ速度やケーブル特性によっては、数メートルやそれ以上の距離での通信も可能です。参考資料[2]で一部の実験データを紹介しています。

過酷な産業環境で使用される絶縁アプリケーションには、ノイズ耐性と同相過渡耐性が不可欠です。シールド付きツイストペア差動ケーブルを使用することで、LVDSラインを介した伝送の干渉耐性が強化されます。ただし、絶縁LVDSバッファで使用される絶縁コアにも同程度の耐性が必要です。電磁気やその他の外乱は、絶縁バリアを越えて同相ノイズとして発生します。同相過渡耐性(CMTI)は、絶縁コアの堅牢性を測るうえで優れた指標となります。

LVDS信号の主な利点は、トランスミッタでの差動動作から生じる電磁放射や出力スイングの小ささ、および同相ノイズを制御できる点です。この利点をシステム・レベルで維持するには、やはり、絶縁LVDSの絶縁コアの電磁放射が非常に小さくなければなりません。同様に、LVDS信号の低消費電力という利点を維持するには、高データ速度時でも絶縁コアでの消費電力を低く抑える必要があります。

サポートされる最大データ速度、アイソレータ経由での伝搬遅延、隣接チャネル間のスキューはどれも重要です。モータ制御アプリケーションには、50Mbps~100Mbpsのデータ速度が必要になる場合があります。SPIアプリケーションでは低伝搬遅延が重要であり、2つのLVDSチャネルを介してクロックとデータが伝送されるシステムでは伝搬遅延スキューが重要となります。

既存のソリューションにおける制限

従来型の高速、高電圧絶縁は、光ファイバ・リンクや、高電圧トランスおよびコンデンサを使用したカスタム設計、デジタル・アイソレータと非絶縁LVDSバッファの組み合わせによって実現されてきました。光ファイバ・リンクは高価で設計に組み込みにくい部品です。ディスクリートの高電圧トランスおよびコンデンサを使用したカスタム実装は、大きな基板面積を占め、消費電力が増大するほか、電磁気互換性(EMC)や信号の整合性を考慮した慎重な設計が必要とされ、動作電圧が高いと高価になります。デジタル・アイソレータと非絶縁LVDSバッファの組み合わせは基板面積を要し、チップ間の配線による信号の劣化もあります。完全に統合された絶縁LVDSバッファは、このような従来型の手法に対する低コストかつ洗練された代替ソリューションとして利用できます。

前述したようなアプリケーションの要件に対応するため、現在は新しい絶縁LVDSデバイスが市場で提供されています。たとえばTIでは、絶縁LVDSバッファのファミリである『ISO 7821LL』、『ISO 7821LLS』、『ISO 7820LL』を提供しています。これらのデバイスは、最大150Mbpsのデータ速度、最大2kVRMS/2828VPKの動作電圧、12.8kVPKのサージ、5.7kVRMSの耐久電圧を実現できます。材料グループIのモールド・コンパウンド(比較トラッキング指数は600V超)を使用した沿面距離8mm、空間距離14.5mmのパッケージで供給されます。これらのデバイスは最小CMTIが100kV/usで、2.25V~5.5Vという広範囲の電源電圧で動作し、150Mbpsでチャネルごとに10mAの低電流を消費します。絶縁LVDSバッファを使用することにより、低コスト、低消費電力、低放射、および長距離にわたる安定した通信リンクを実現しつつ、高電圧絶縁を提供できます。

注記:

[1] データ・シート:『ISO 7821LL』、『ISO 7821LLS』、『ISO 7820LL』

[2]ホワイト・ペーパー:『Isolation in AC Motor Drives:Understanding the IEC 61800-5-1 Safety Standard』

参考資料:

+アプリケーション・ノート:『Performance of LVDS with different cables』

<著者紹介>

アナン・カマス (Anant Kamath)

TI システムおよびアプリケーション・マネージャ

現在は、高性能アナログ製品の新規開発および、既存の産業用/車載用製品のアプリケーション・サポートを統括。フェーズロック・ループ(PLL)およびクロック・システム、高速シリアライザ/デシリアライザ(SerDes)、高電圧デジタル絶縁デバイスの設計など、広範な経験を有する。インド工科大学マドラス校卒業(電気工学科学技術 学士号取得)

*ご質問は E2E 日本語コミュニティにお願い致します。