低ドロップアウト(LDO)リニア電圧レギュレータの本質的特性は、その名前や略語の元になっていることからも明らかなように、“ドロップアウト”です。

最も基本的なレベルでのドロップアウトとは、適切なレギュレーションに必要とされるVINとVOUTの間の最小電圧差のことです。しかし、これに変動要素を組み合わせると、微妙に意味の異なるものになります。ドロップアウトは、効率的な動作を実現し、制限のあるヘッドルームで電圧レールを生成するためには不可欠なものであり、ここではその仕組みを説明していきます。

ドロップアウトとは

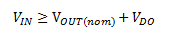

ドロップアウト電圧VDOは、適切なレギュレーションを行うために、入力電圧VINが、必要な出力電圧VOUT(nom)に対して上回っていなければならない最小電圧差を表しています。次の式1を参照してください。

VINがこの値を下回るまで低下した場合、リニア・レギュレータはドロップアウト動作に切り替わり、目的の出力電圧のレギュレーションが行われなくなります。このような場合、出力電圧VOUT(dropout)は、VINからドロップアウト電圧を減算した値に追従します(式2)。

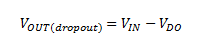

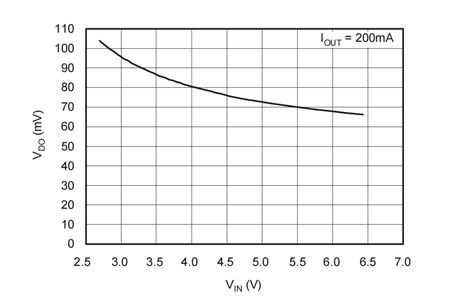

例として、TPS 799のようなLDOで3.3Vのレギュレーションを行っていると考えてみましょう。200mAを供給する場合、TPS 799の最大ドロップアウト電圧は175mVと規定されています。入力電圧が3.475V以上である限り、レギュレーションへの影響はありません。しかしながら、図1に示すように、入力電圧が3.375Vに低下すると、LDOがドロップアウト動作に切り替わり、レギュレーションは停止します。

図1:ドロップアウト動作中のTPS 799

本来なら3.3Vにレギュレートするはずですが、TPS 799にはレギュレーションを維持するために必要なヘッドルームがなくなるため。結果として、出力電圧は入力電圧に追従し始めます。

ドロップアウトを決める要因とは

ドロップアウトは、第一にLDOのアーキテクチャによって決まります。その理由を確認するために、PMOSおよびNMOS LDOに目を向け、それらの動作を比較してみましょう。

PMOS LDO

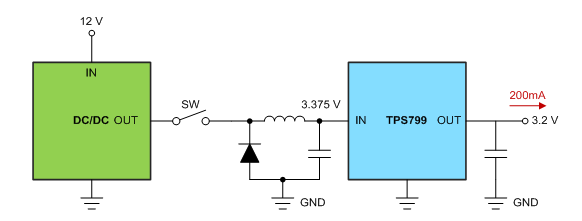

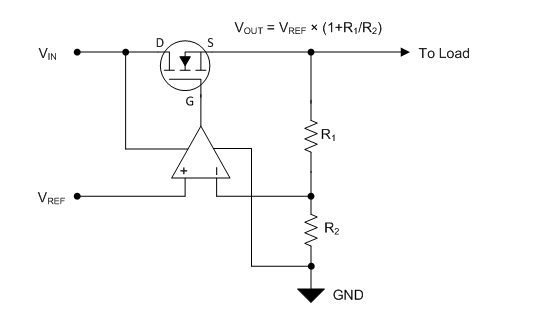

図2は、PMOS LDOのアーキテクチャを示しています。必要な出力電圧にレギュレートするため、帰還ループによってドレイン-ソース間抵抗(RDS)を制御しています。VINがVOUT(nom)に近づくにつれ、RDSを低下させてレギュレーションを維持するために、エラー・アンプがゲート-ソース間電圧(VGS)を負側に引き下げます。

図2:PMOS LDO

ただし、ある時点においてエラー・アンプの出力がグランド電位で飽和し、VGSをそれ以上負側に引き下げることができなくなります。この時点でRDSは最小値に達しています。このRDSの値と出力電流(IOUT)を乗算すると、ドロップアウト電圧が得られます。

VGSの値が負側に引き下げられるほど、RDSが低下するということを覚えておいてください。入力電圧を大きくすることで、VGSをさらに負側に引き下げることができます。したがって、PMOSのアーキテクチャでは、入力電圧が上昇するほど、ドロップアウトが低下します。図3は、この動作を示したものです。

図3:TPS 799のドロップアウト電圧 対 入力電圧

図3に示すように、TPS 799では、入力電圧(および出力電圧)の上昇に伴い、ドロップアウト電圧が低下します。これは、入力電圧が大きいほど、VGSがより負側に引き下げられるからです。

NMOS LDO

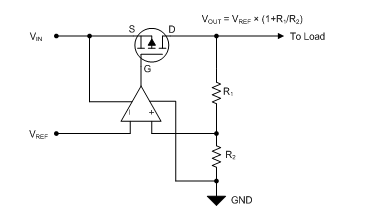

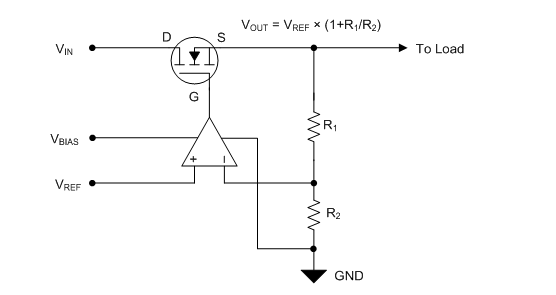

NMOSのアーキテクチャの場合も、図4に示すように、帰還ループによってRDSを制御します。ただし、VINがVOUT(nom)に近づくにつれ、RDSを低下させてレギュレーションを維持するために、エラー・アンプがVGSを引き上げます。

図4:NMOS LDO

ある時点において、エラー・アンプの出力が電源電圧(VIN)で飽和するため、それ以上VGSを引き上げることができなくなります。このような状況でのRDSは最小値となります。この値と出力電流(IOUT)を乗算すると、ドロップアウト電圧が得られます。

すなわち、エラー・アンプの出力はVINで飽和するため、VINがVOUT(nom)に近づくにつれ、VGSも低下するという問題が生じます。このため、超低ドロップアウトにはなりません。

LDOのバイアス

多くのNMOS LDOには、図5に示すように、バイアス電圧(VBIAS)と呼ばれる補助レールが採用されています。

図5:バイアス・レールを備えたNMOS LDO

このレールは、エラー・アンプ用の正電源レールとして機能し、出力をVINより大きいVBIASまでスイングできます。この種の構成では、LDOで高VGSを維持することができ、結果として低出力電圧で超低ドロップアウトを実現できます。

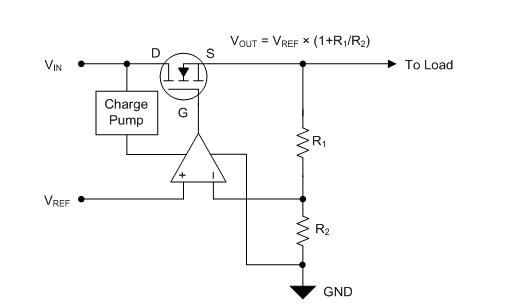

補助レールは利用できない場合もありますが、それでも低出力電圧で低ドロップアウトを実現できる点は好都合です。このような条件下では、図6に示すように、VBIASを内部チャージ・ポンプに置き換えることができます。

図6:内部チャージ・ポンプを備えたNMOS LDO

チャージ・ポンプによってVINが昇圧されるので、外部のVBIASレールがなくても、より大きなVGS値をエラー・アンプで生成できます。

その他の変動要素

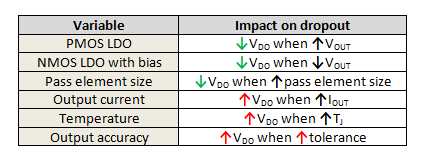

ドロップアウトに影響する変動要素は、アーキテクチャの他にも表1にまとめたようにいくつかあります。

表1:ドロップアウトに影響する変動要素

ドロップアウトが静的な値ではないことは明らかです。これらの変動要素は、単にLDOの選択を複雑にするものではなく、特定の条件に最も適したLDOを選択するうえで役立つ要素となるはずです。LDOドロップアウトの詳細については、アプリケーション・ノート『Understanding LDO Dropout.』をご覧ください。

その他のリソース

- その他のLDOに関するブログ記事をご覧ください。

上記の記事は下記 URL より翻訳転載されました。

https://e2e.ti.com/blogs_/b/powerhouse/archive/2017/03/16/ldo-basics-dropout

*ご質問は E2E 日本語コミュニティにお願い致します。