Hi all,

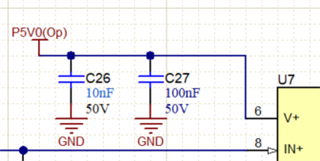

I am currently working on a project using the INA901-SP with two decoupling capacitors wired as shown below:

My question is whether I can have one of these decoupling caps on the bottom layer to optimize space as follows:

Would this be okay with the 901 or would it be better to have both decoupling caps on the same layer?

Thank you in advance for considering my question and I hope to hear from you soon!

-Filipe