Other Parts Discussed in Thread: XTR300,

Hi,

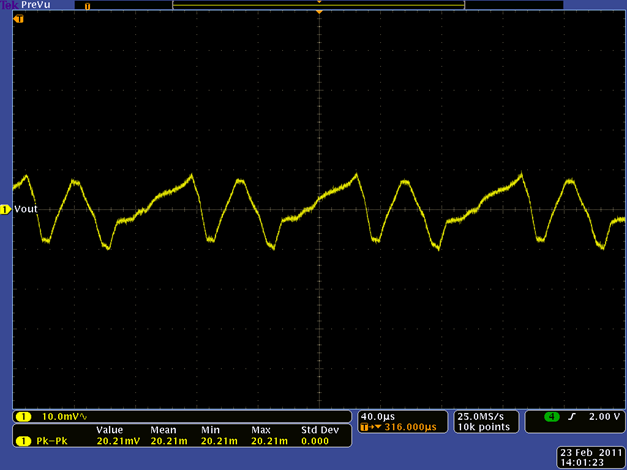

Can you please help me to relate the Figure 5(0.1Hz to 10Hz NOISE, RTI) to Figure 39 (Output Noise without Filter into 500Ω) in the datasheet (SBOS375C –NOVEMBER 2006–REVISED JUNE 2011) if Rset = 2k in terms of the peak amplitude

Best Regards,

Kavindu