Other Parts Discussed in Thread: OPA828, TINA-TI

Our design uses OPA544T.

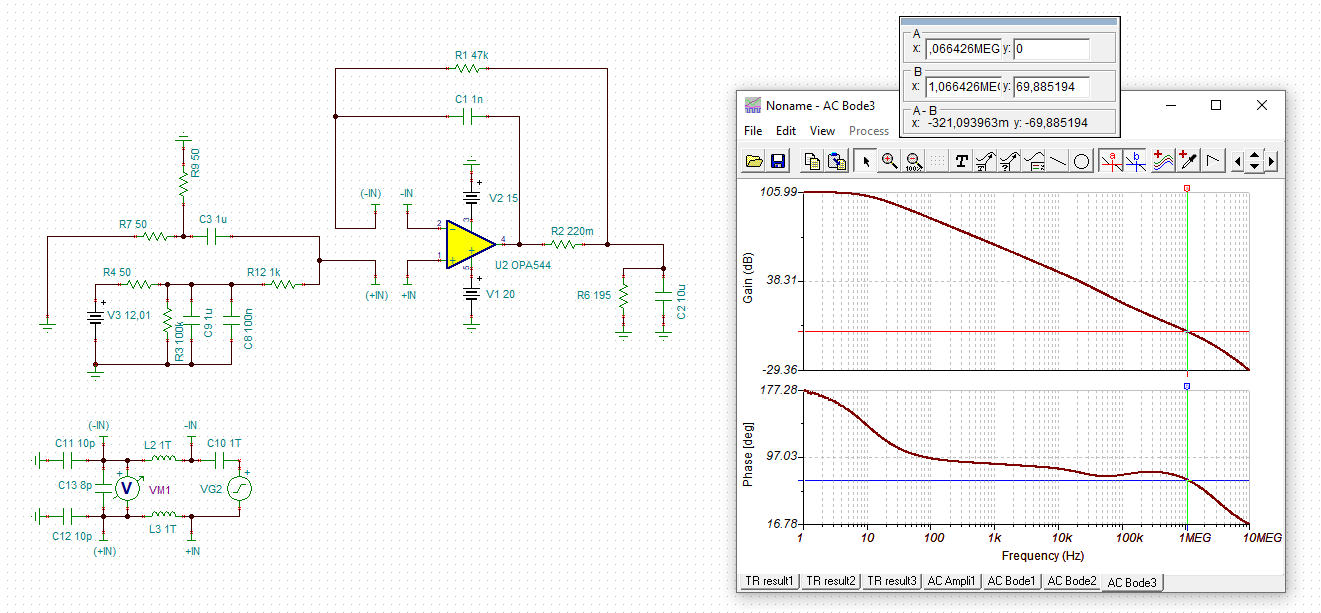

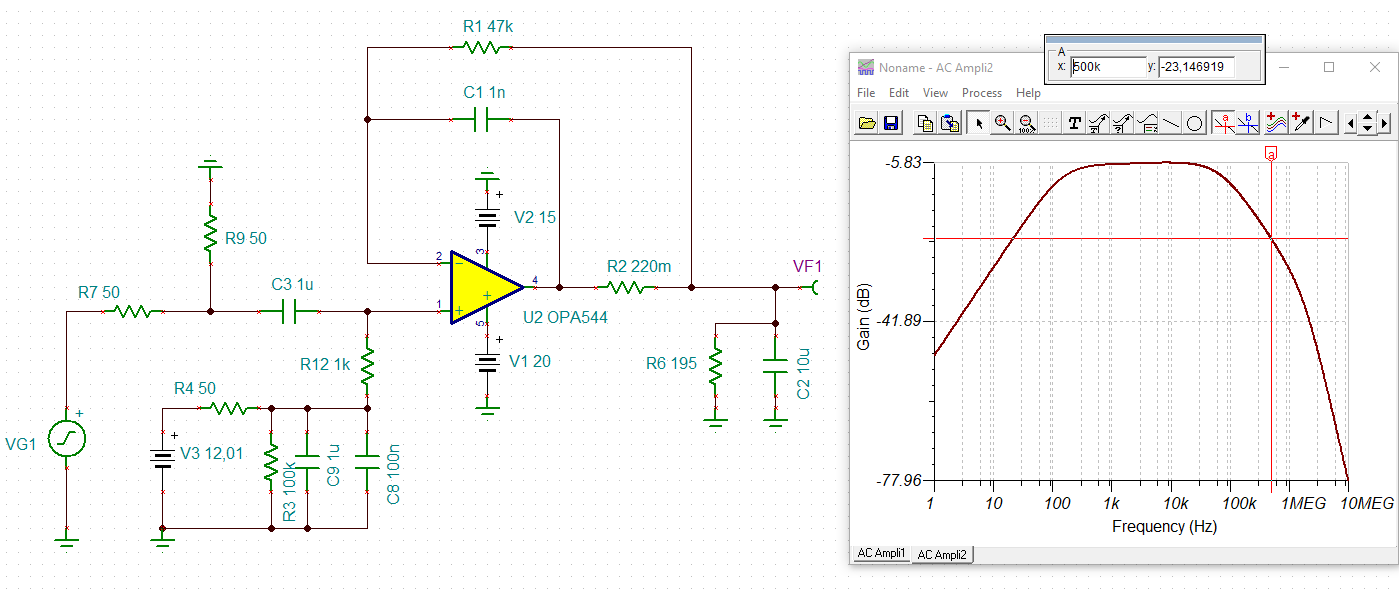

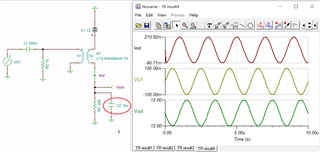

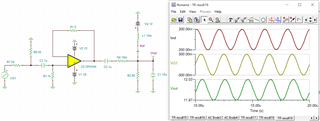

We have simulated the design using the model available. PFA .TSC file, FYR.

OPA544_12V_Switching_500KHz.TSC

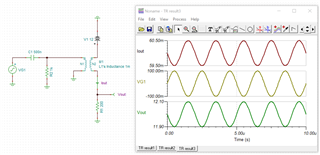

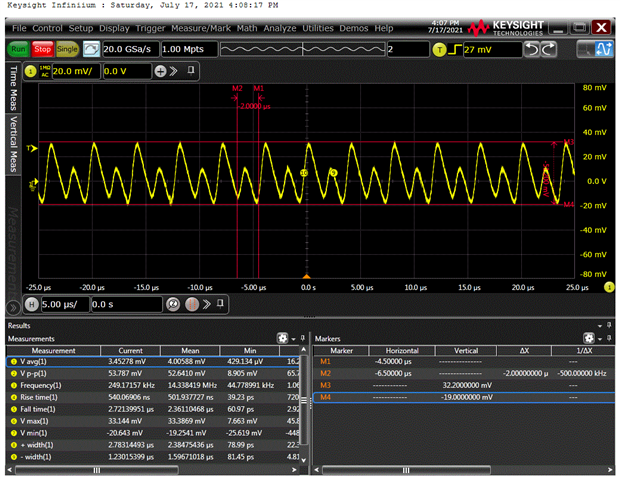

Waveforms from the prototypes Testing:

Vin:

Vout with Oscilloscope set to DC mode:

Vout with Oscilloscope set in AC mode:

Observation:

We could see that the output waveform is distorted and not sine wave + DC offset. We are able to get the sinewave at the output upto 380KHz.

Pl let us know what is causing the output distortion and suggestions for improving the circuit.