Other Parts Discussed in Thread: OPA376

Hi all,

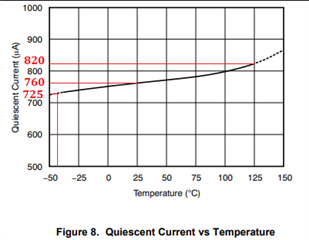

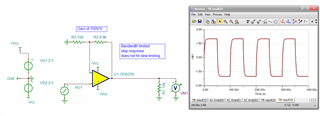

I have got a question about the slew rate variation of OPA376-Q1. Can you tell me how OPS376-Q1 slew rate changes when temperature changes to -40degC and 125degC? Also, I would like the data of slew rate when output gain is +10 and +100.

If you have any data related to this, I'd be appreciated to get those data.

Regards,

RYO