Hi team,

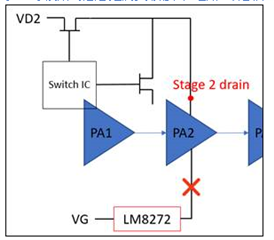

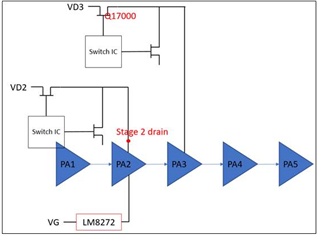

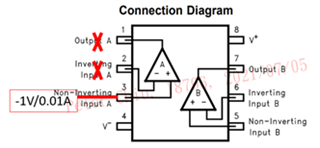

We follow your suggestion and still see the same issue. (pin5 connect to pin1)

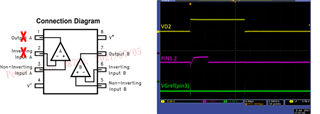

In addition, we also do some measurement to verify the OP state. The result shows that even though we remove OP load and use external power supply. The issue still occurred. Can you let me know whether is related to OP internal design?

- First, we float the OP pin1 and pin2, but ramp up curve still occurred.

-Second, we float pin1/2/3 and use external power supply, the issue still occurred.

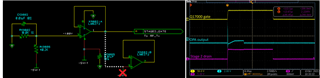

In addition, we found that we will see the 178MHz oscillation before OP ramp up. Does it affect the stability of OP?

Regards,

Roy