Other Parts Discussed in Thread: OPA365, OPA320, OPA325, TMUX1308, OPA348, OPA392, OPA377, OPA3S328, OPA2325, OPA4325, TMUX1309, OPA328, TMUX1108, TMUX1109, ADS131E08

Hello

I would like to know the application of PGA117.

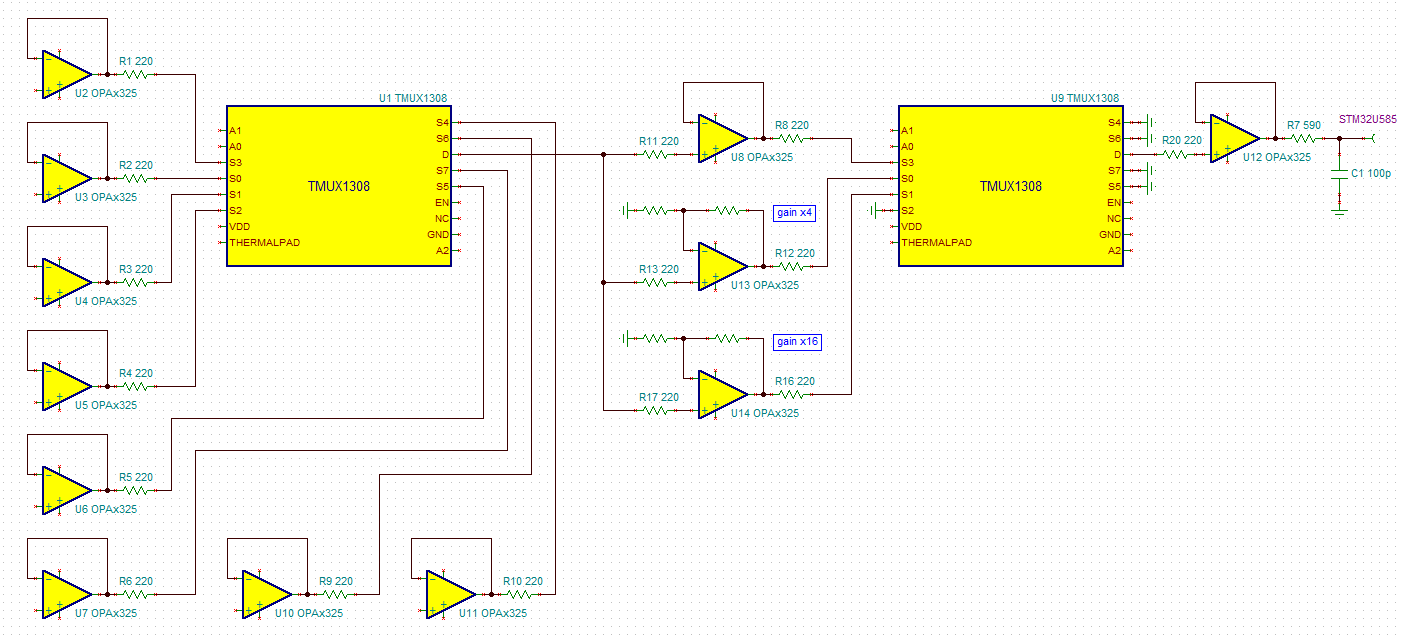

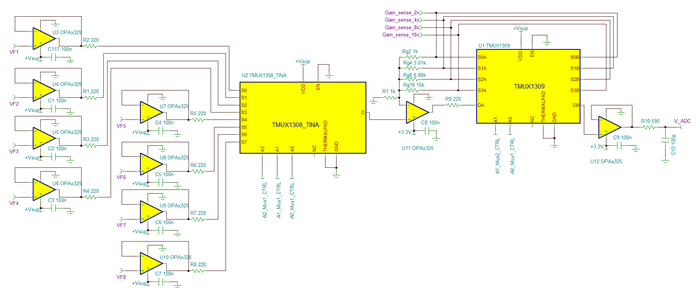

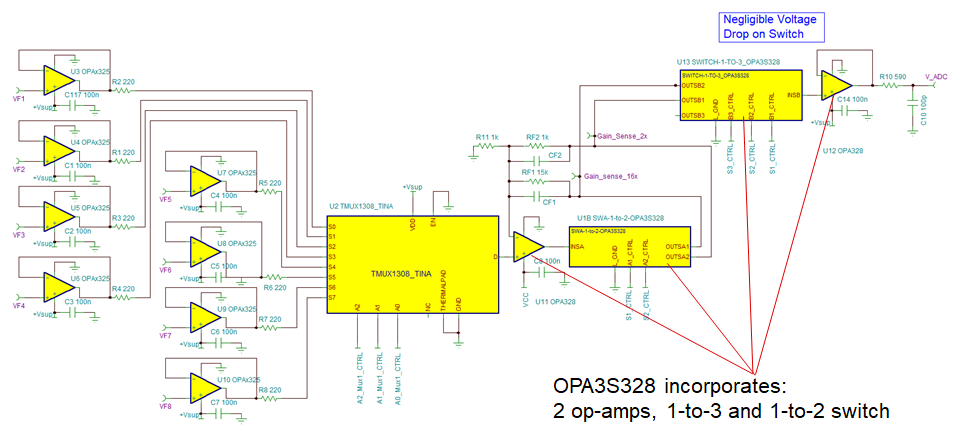

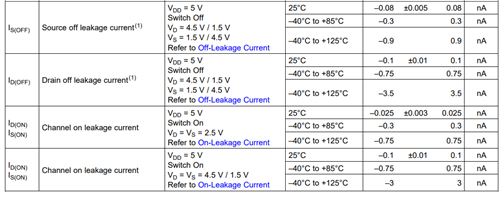

I have a six channel input signal, which is 50Hz. And I would like to use an ADC to sample all of them.

Can I use PGA117 for channel and gain selection?

The gain selection will not switch a lot, I have a determined value after power on.

But the channel selection is quite frequent, I want to measure all the six channels. The current signal is 50Hz.

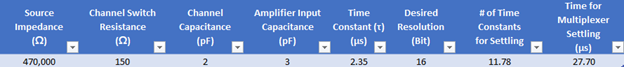

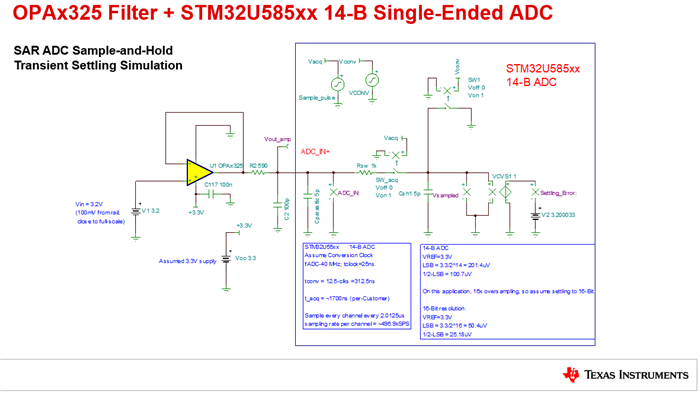

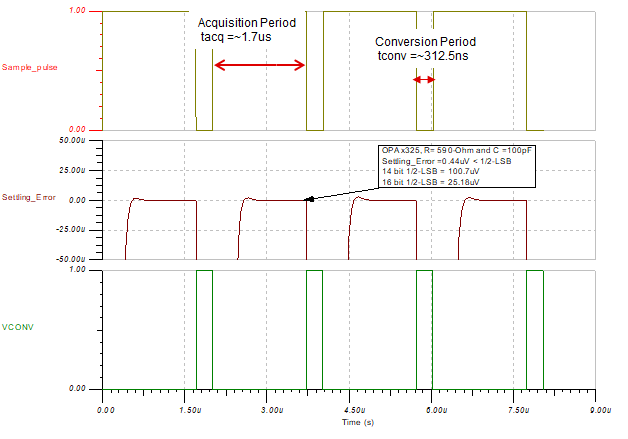

And for each channel, I will stay 64us for sampling, then to another channel. The sample-hold time is 1.7us, means I have 1.7us to charge the CSH capacitor.

Is PGA117 suitable for this kind of application, is the mux of PGA intend to use for high frequency?

Even all the six channel are all 50Hz, the signal level difference between each channel could be high.

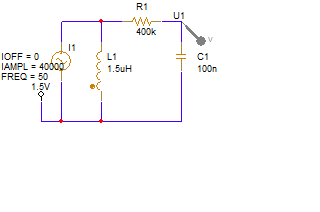

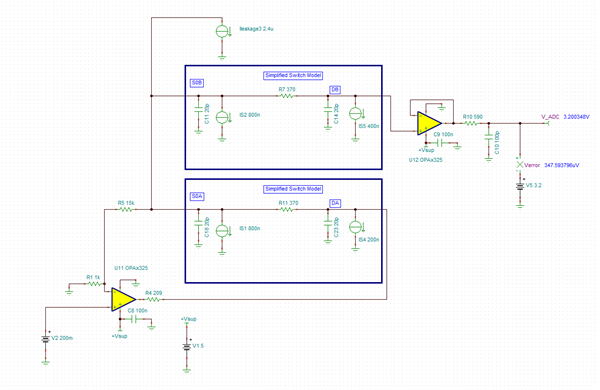

Could you help provide a simulation?