Other Parts Discussed in Thread: OPA2376,

Dear Specialists,

My customer is evaluated OPA2376 in the customer's circuit, offset voltage is larger than the calculated value.

I would be grateful if you could advise and make a friendship.

--

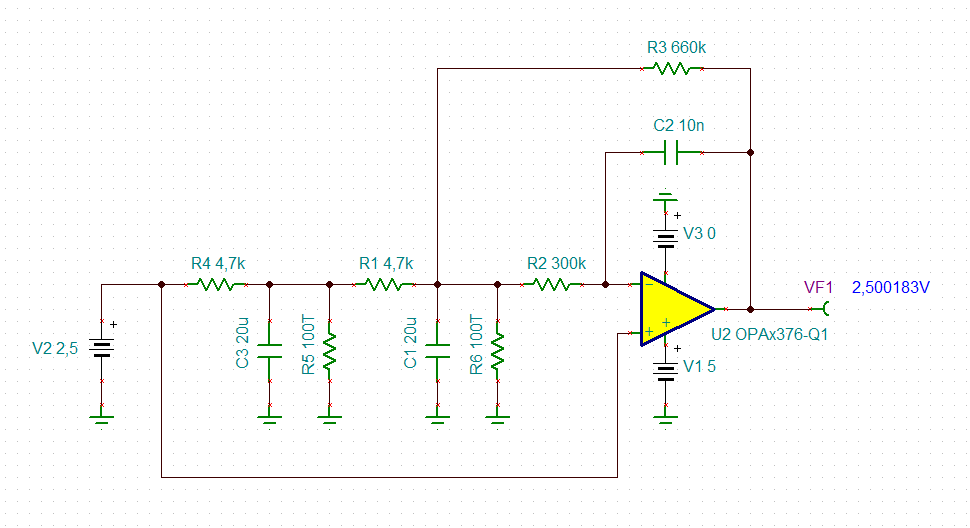

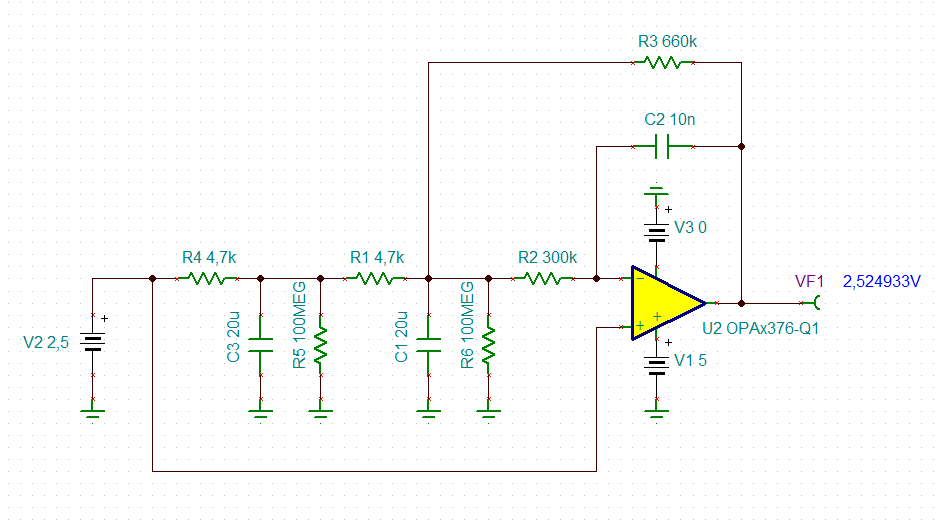

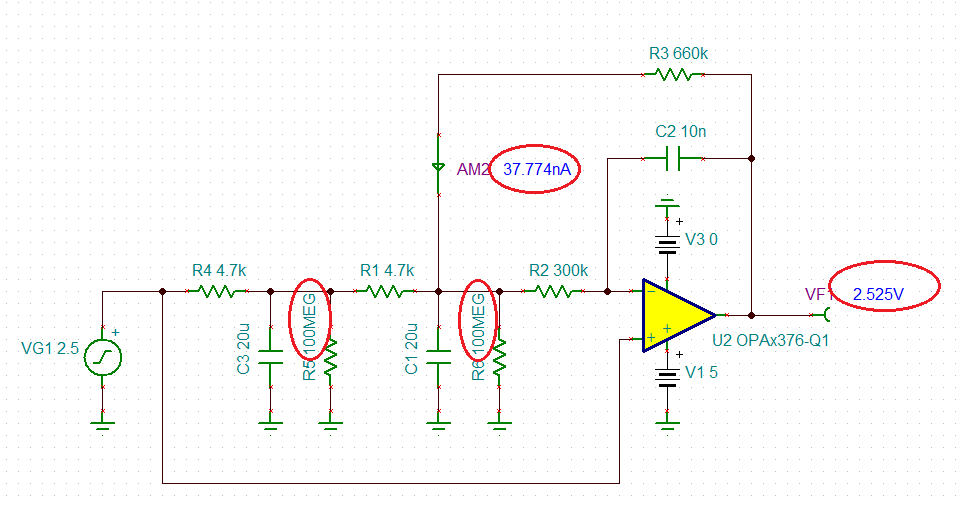

In an inverting amplifier circuit with an amplification factor of about 70 using OPA2376QDGKRQ1,

When the same voltage was applied to the input and non-inverting input terminals as shown in the file below, an offset voltage was generated higher than expected .

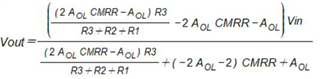

When I calculated the offset current, offset voltage, resistance tolerance, temperature characteristics, PSRR, and CMRR of the inverting / non-inverting input terminals,

the result was that CMRR dominates the offset voltage of Vout.

When the calculated CMRR was the worst, the offset voltage was about 30 mV, while the actual measurement was 60 mV.

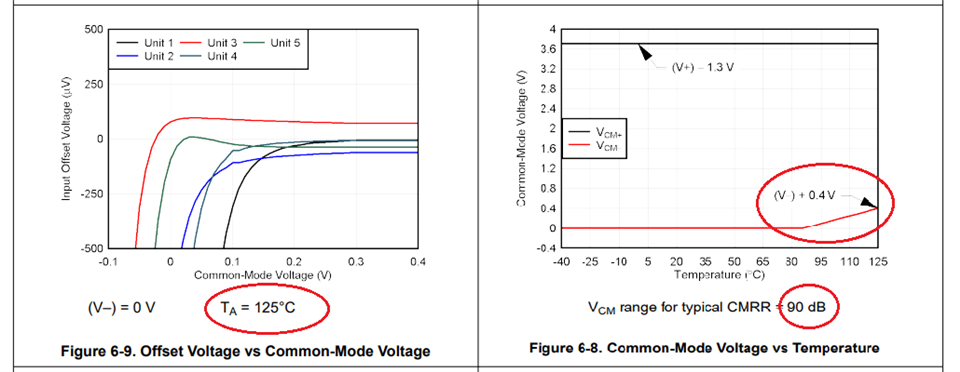

1) Is it possible to drop below CMRR = 90 dB at a common mode voltage of 2.5 V and T = 25 ° C?

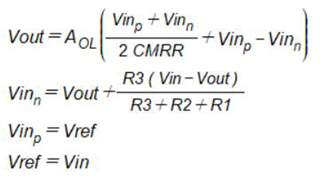

2) Do you have the following idea about the relationship between CMRR and output voltage?

* I ignored R4 and capacitors because I was thinking of applying DC.

Could you please tell me what Figure 6-9 means?

Does it mean that an offset voltage is generated when both the inverting input terminal and the non-inverting input terminal are low and the common mode voltage is close to 0?

---

For more details of the measurement results, we will send you after making a friendship.

I appreciate your great help in advance.

Best regards,

Shinichi