Other Parts Discussed in Thread: TINA-TI, OPA551, OPA593

Hi all.

For a medical sensor testing facility I need to inject a precise "pulsed" current into the sensor (merely modeled as a resistive load) for a given amount of time.

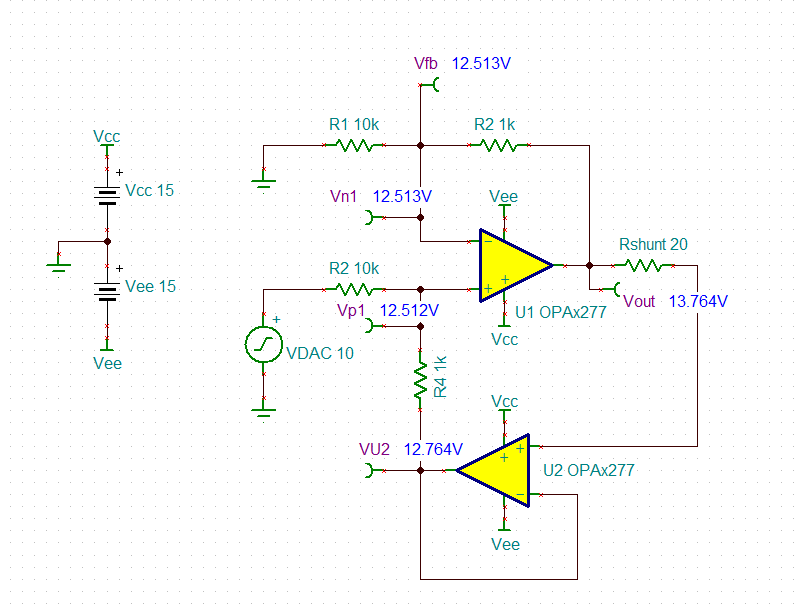

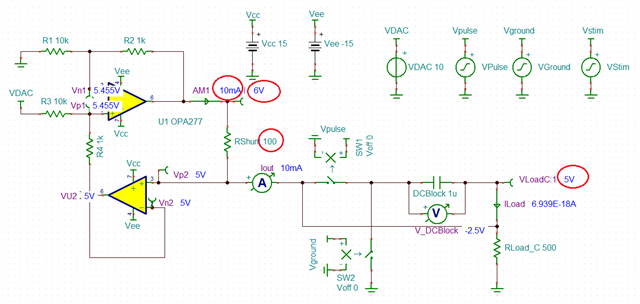

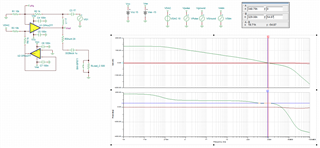

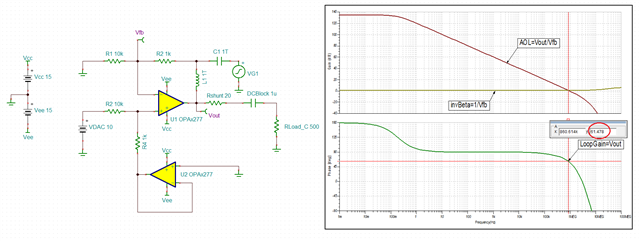

That's why I was thinking of a Howland Current pump with the OPA277.

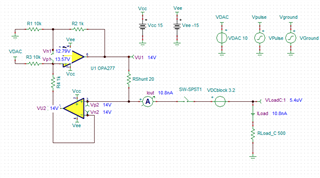

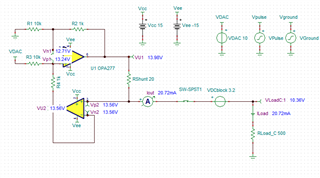

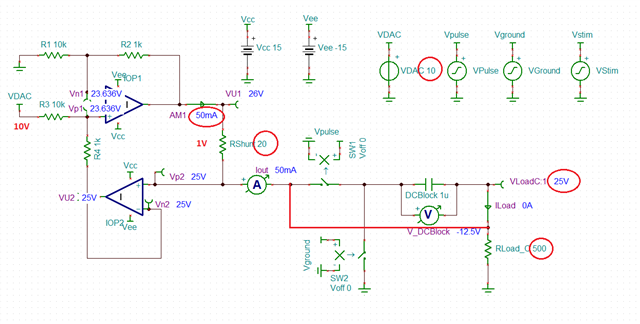

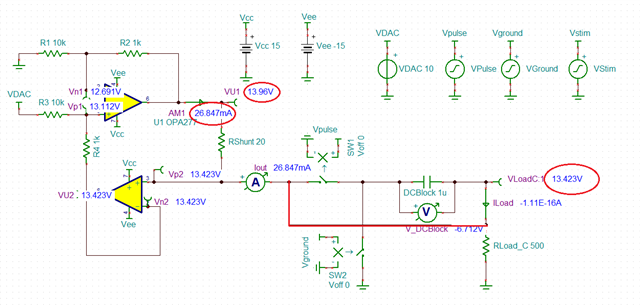

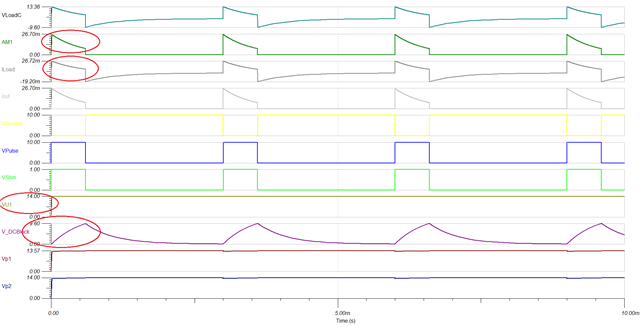

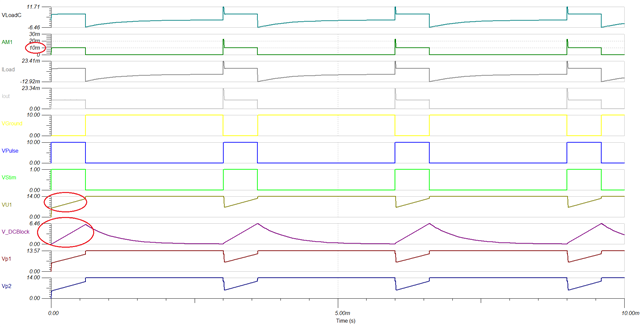

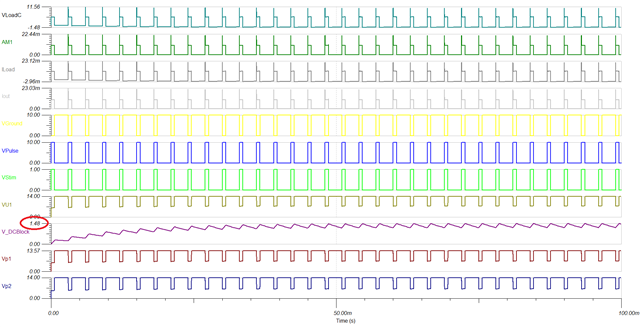

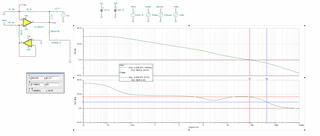

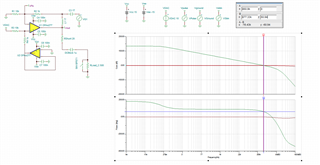

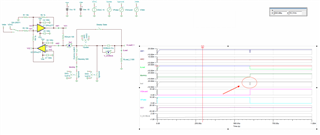

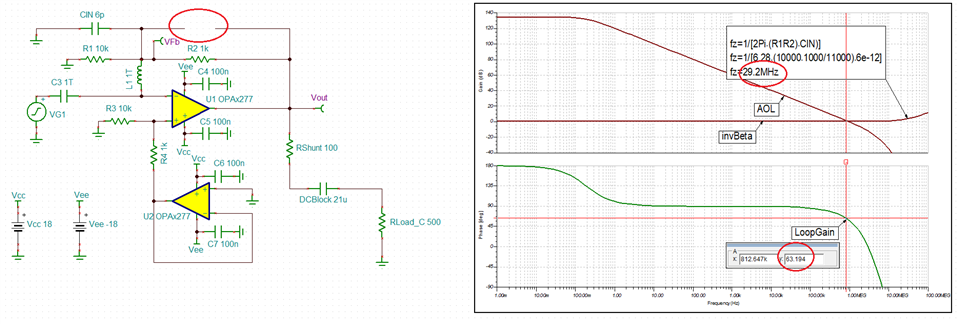

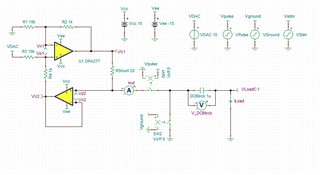

I can theoretically control the current precisely via the voltage applied at its input. Here the TINA-TI simluation:

A DC blocking capacitor at the output of the opamp before the pure resistive is used so forming a C-R circuit (a high pass filter).

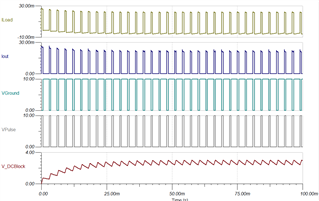

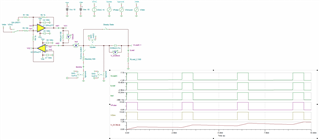

The stimulation is performed in two phases:

- Pulse phase (lasting 600us): where the load is connected to the opamp via the DC Block capacitor injecting the current typically 10mA-20mA.

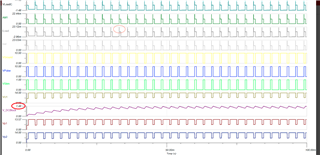

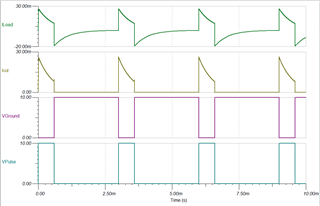

- Ground phase (lasting 2,4ms): the load disconnects from the opamp and shorts to ground. therefore the charge accumulated into the DC capacitor flows back into the load in the opposite direction until its complete discharge, avoiding any net charge accumulated into the load ( in reality the sensor) during every cycle. That is graphed on the photo attached where I have used two pulsed square waves (Vpulse and Vground) to activate the relative switches.

You can see in the figure the first graph Iload - the current that flows back and forth into the load.

Now the questions:

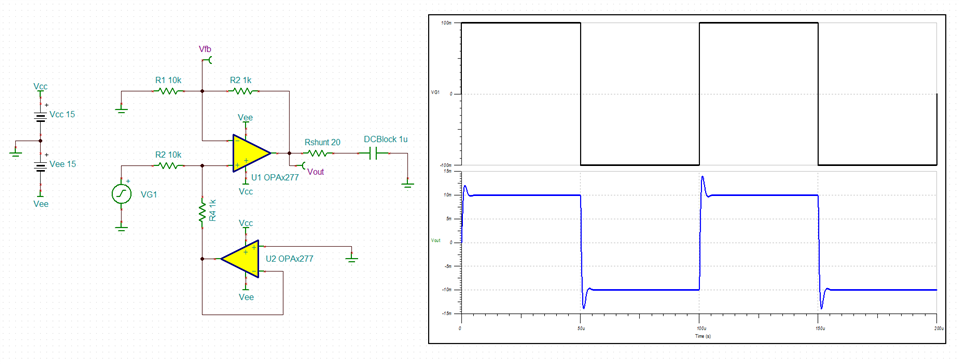

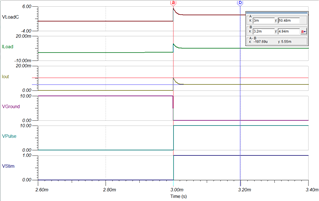

1. Am I secure during the ground phase to let the output of the OPAMP floating and then switching it back to the load? I'm afraid not: there will be for sure on a real PCB parasitic inductances, but I don't know how to perform such a protection. what is the best way to protect the output stage of the opamp? should I switch the opamp to a dummy resistor during the ground phase?

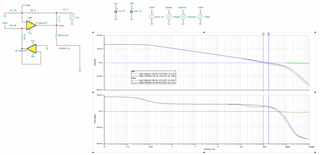

I can see spikes on the output of the OPAMP: the things get worser if I reduce the current injected to 5mA, i have huge current spikes of 10mA on the output during the reconnection of the load.

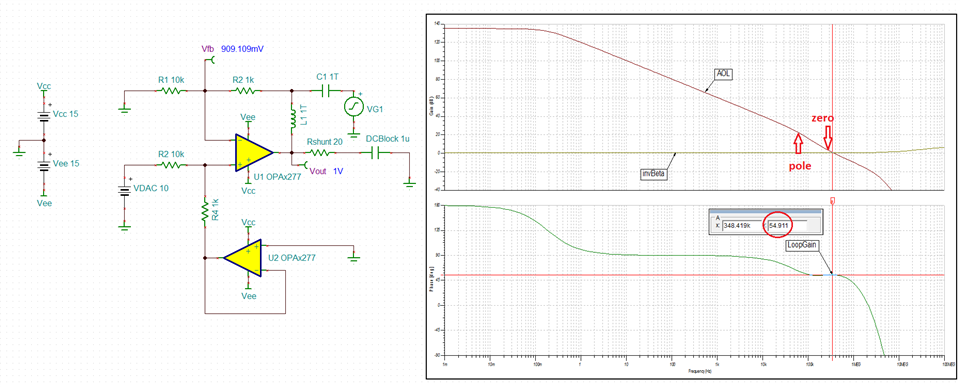

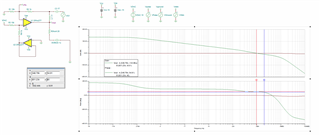

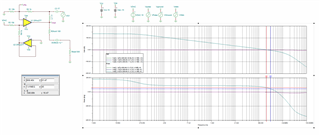

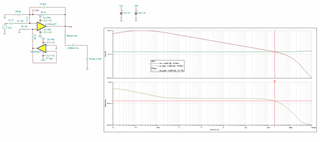

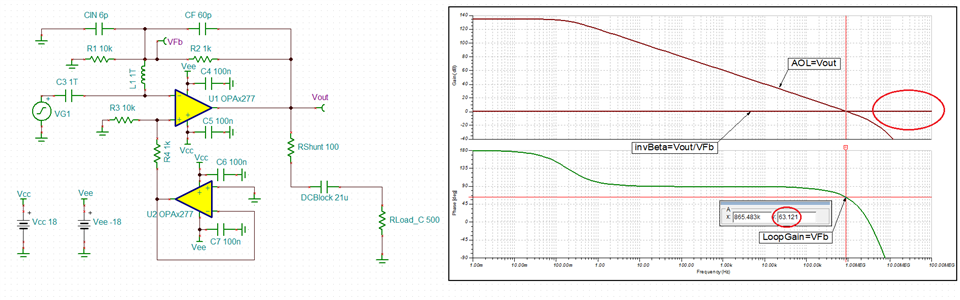

2. How to calculate the stability of the circuit with this typology of loads?

I mean, having studied the Ti precision Lab theory stability chapter there is always mention of capacitive loads connected in parallel that introduces poles, not in serie one. So how to perform such an analysis?

My AC analysis is a little bit naive. Since the load resistance may vary from 400 to 1,2k I would like to be sure about the correct phase margin. But don't know where to start. Where have I to open the OPAMP loop?

Have already read the suggestion from Tim Green here: https://e2e.ti.com/support/amplifiers-group/amplifiers/f/amplifiers-forum/739959/tina-spice-ina133-tips-to-carry-out-stability-analysis-for-improved-howland-current-source but don't know where to start.

Thank You for any help in advice,

Stefano