Other Parts Discussed in Thread: DAC128S085, TLV9302, , TLV4172, OPA4191

Hai Sir,

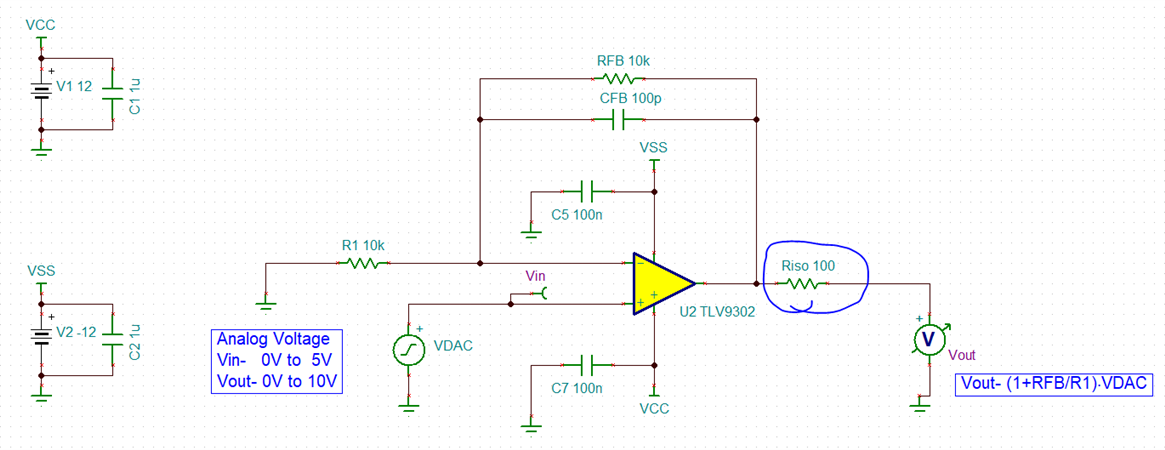

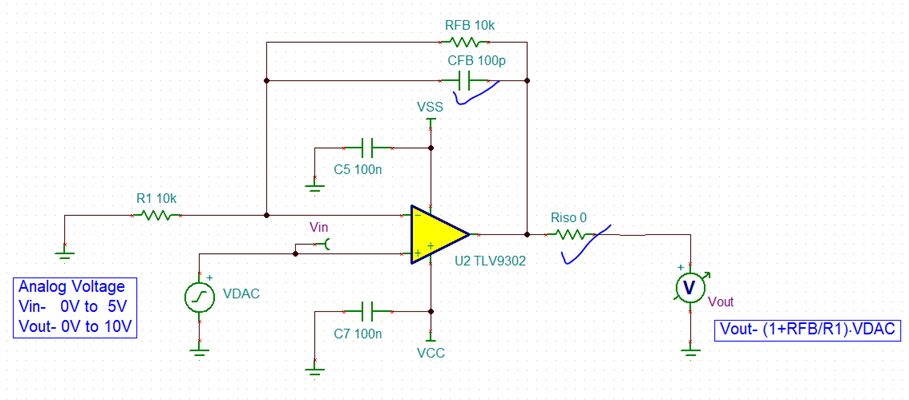

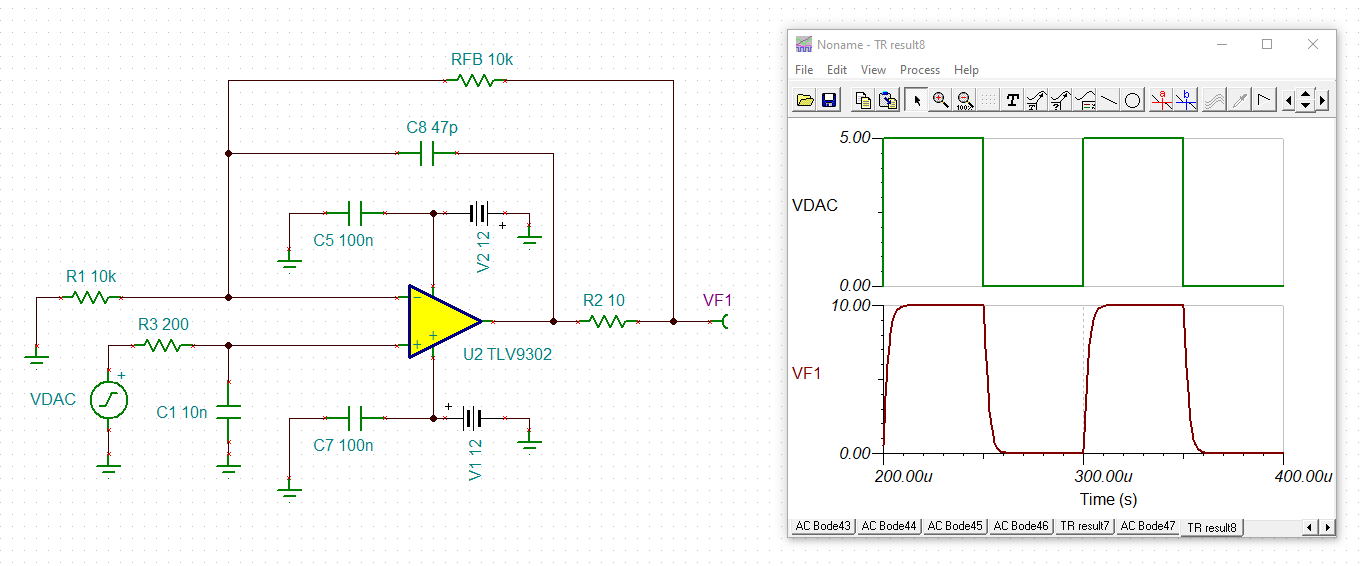

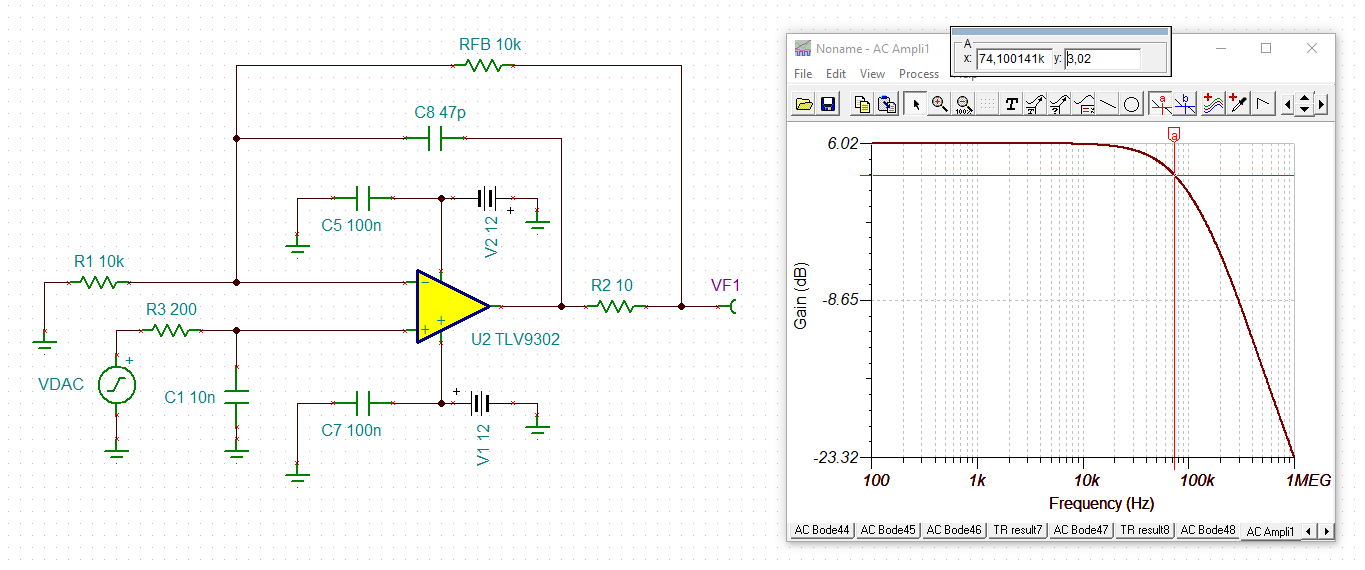

My End application is - Controlling & Analog outputs driving.

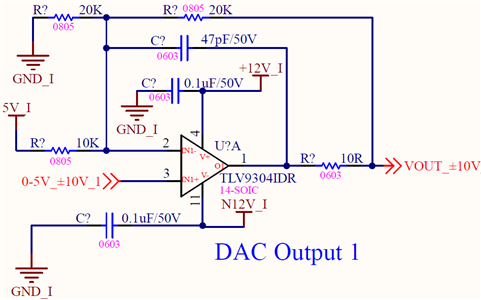

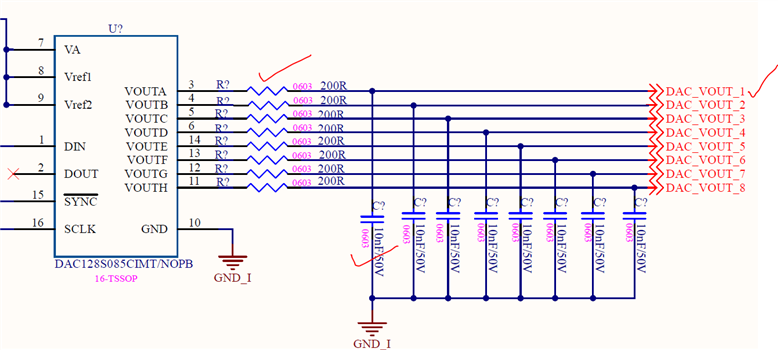

We are planning to generate the 0-10V & ±10V output using Opamp-TLV9304. Here we have to give the input voltage(0-5V) to Opamp is from DAC (DAC128S085).

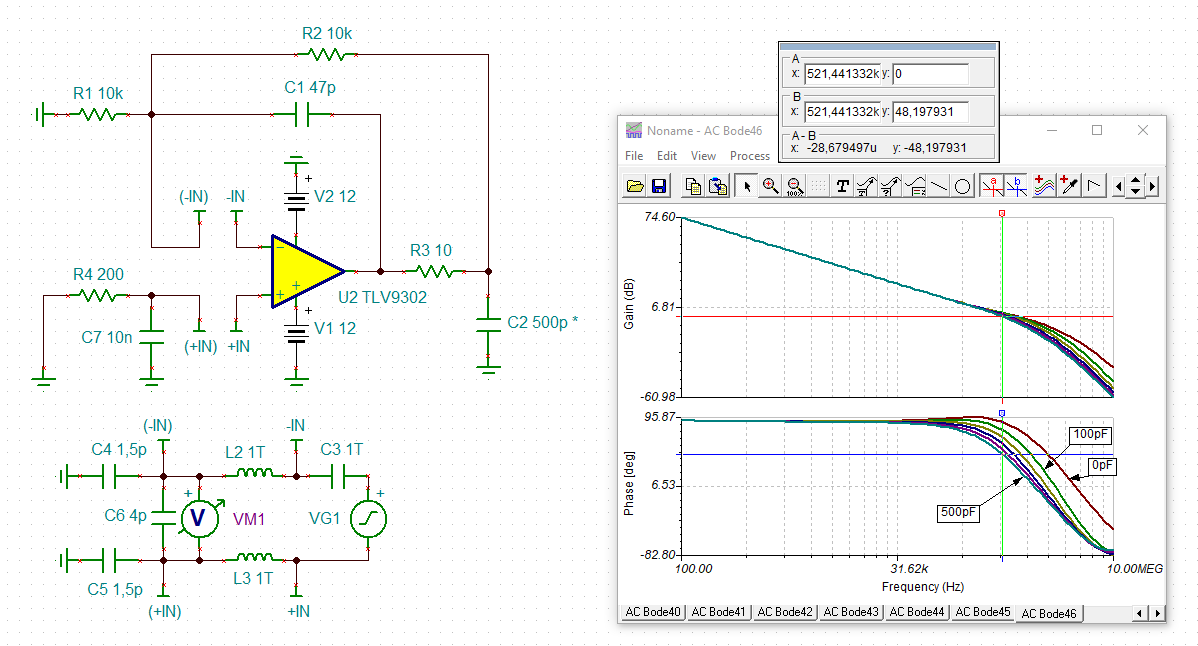

Can you please verify the attached tina simulation file for design verification to generate 0-10V & ±10V from 0-5V and let me know if any modifications to be done.

0-10V & ±10V_OpmapTLV9304.09.08.22.TSC