Other Parts Discussed in Thread: SN74CBTLV3251

Hi,

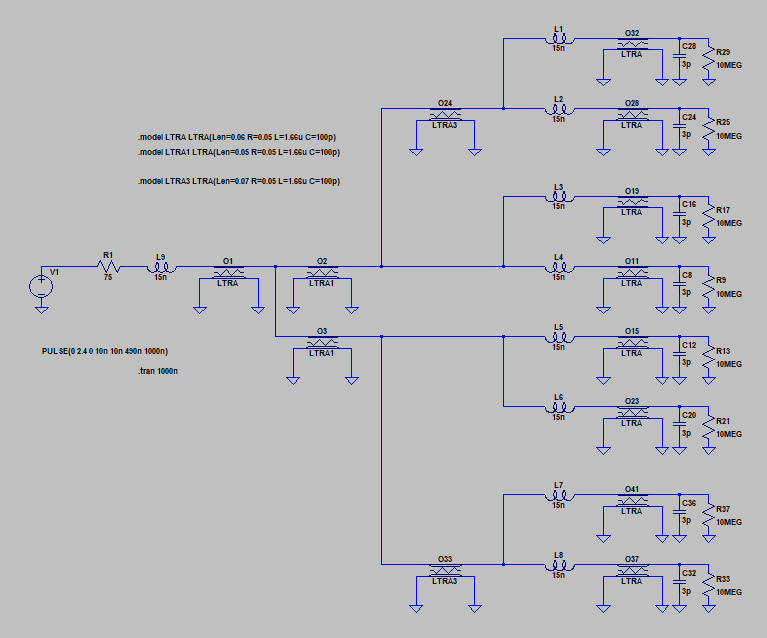

I would like to daisy chain 64 of thes parts on the same SPI bus direct tie the SCLK and SDI pin together with separate independent CS and SDO. Is it possible? Can you tell me the current required for the SCLK and SDI?

Thanks.

VD