Other Parts Discussed in Thread: OPA659, OPA2810, OPA2822, OPA858, , TINA-TI

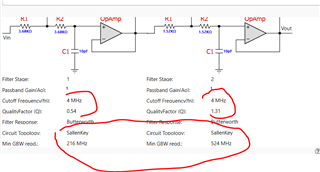

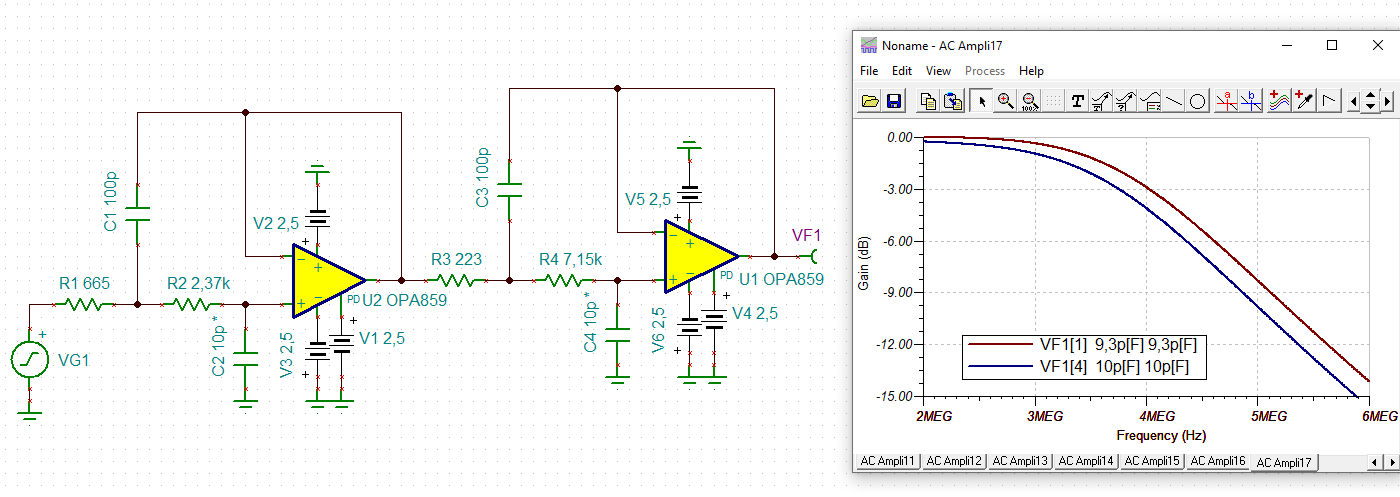

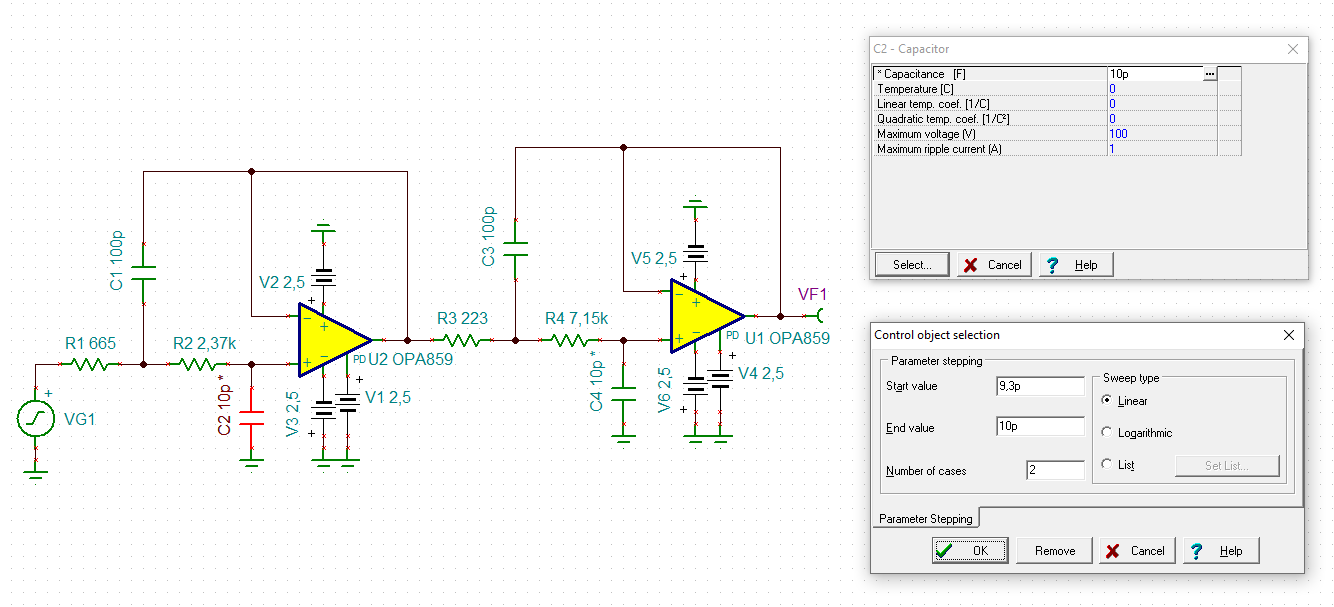

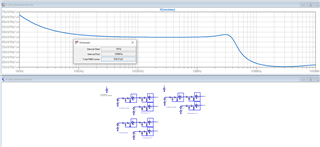

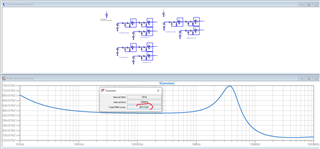

I used the TI Filter Design Tool to get a 4-pole Butterworth design using two Sallen & Key stages. Corner frequency was design at 4 MHz, yet the simulation shows -3dB at 3.4 MHz. Years ago Sallen & Key did not simulate well due to the positive feedback - I'm wondering if that is still the case. Also, I couldn't get TI PSpice to converge at all so I simulated in LTSpice with a similar amplifier. TI Spice file attached.