Other Parts Discussed in Thread: AMC1311-Q1, AMC1311, LMV321

Hi TI expert,

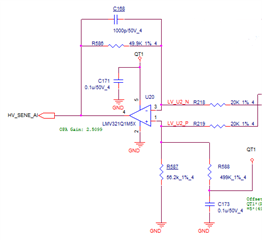

May I know how to judge the Vout tolerance if we short the "right side" of the R218 & R219 together in the below application?

We add a 0.5V offset by R588/C173/R587.

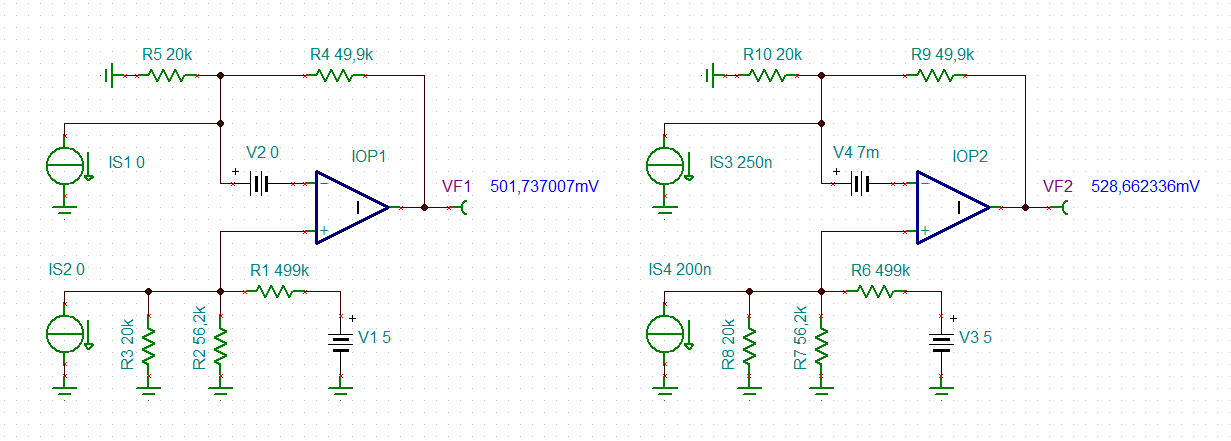

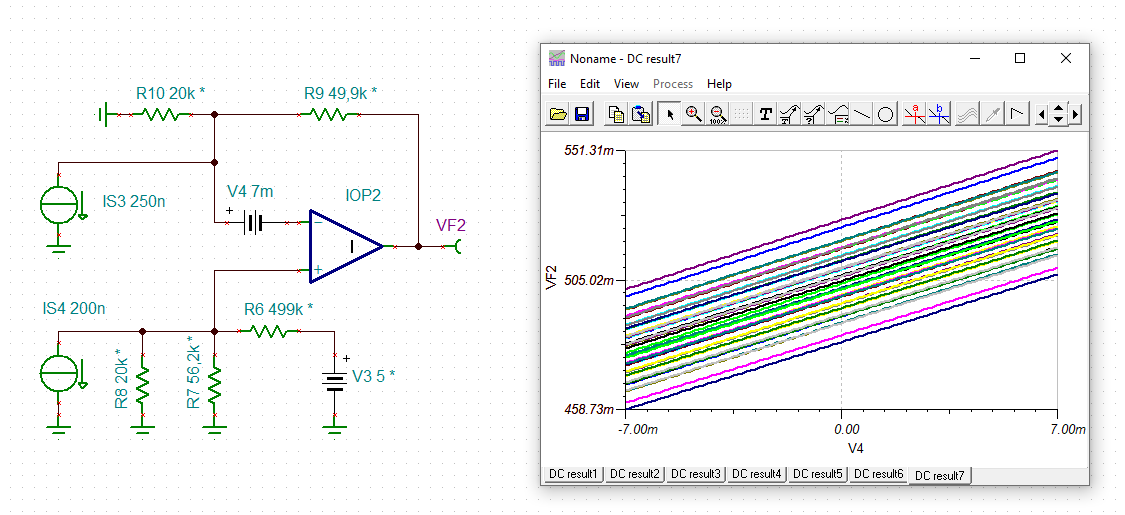

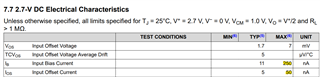

As I know the Ibias and Vos will affect the Vout but not quite sure how to judge the output tolerance based on that.

Could you guide us on how to calculate the VOUT tolerance for this case? we need to do the calibration for cascaded ADC from "HV_SENE_AI".

QT1 = 5V with 1% tolerance.

Looking forward to your reply.

Thank you.