Hi teams,

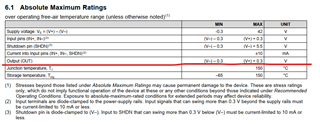

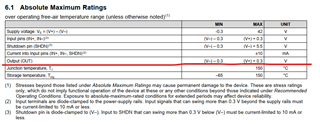

Refer to TLV1805 datasheet below ,

does it mean that the absolute max voltage of output pin relies on supply voltage.

For example, If ±12V is supplied for AMP, the voltage range that output pin coud withstand is -12.3V ~ 12.3V.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi teams,

Refer to TLV1805 datasheet below ,

does it mean that the absolute max voltage of output pin relies on supply voltage.

For example, If ±12V is supplied for AMP, the voltage range that output pin coud withstand is -12.3V ~ 12.3V.

Yes; there is a diode from the pin to V+. See [FAQ] Can the input voltage (Vi) to my logic device be higher than the supply voltage (Vcc)?

Again, thanks again Clemens!

Hello Xiansong,

Normally the output should not exceed the supplies. Normally you do not force current back into the output.

However, inductive loads or long traces can cause inductive kick-back or ringing that may push the output beyond the supplies. There are ESD didoes on the output to the supplies that should clamp the output, and the output limit spec is for these diodes.

Hi Paul,

Thanks for your reply.

Based your reply and the datasheet, I think 0.3V is the litmit voltage spec for the ESD diode.

Normally a VF of diode is defined based on IF, besides for voltage limit spec as 0.3V, is there any information on the current limit spec for the ESD diode or output pin.

Hello Xiansong,

The 0.3V limit keeps the diode from fully conducting so that the input bias current is still within spec.

As for current, we recommend keeping the ESD diode current below 10mA (similar to the input) or as low as possible.

If there are chances of exceeding the supply, then external clamps are recommended.