Other Parts Discussed in Thread: INA237

Hy,

we develop a 19" rack with 8 cards, each holding a INA237-Q1. We put the pins A0 and A1 to the card edge connector, on the backplane we connect A0 / A1 to Gnd, 3.3V, SDA or SCL differently for each slot. On each card, there is also an eeprom (address range 0x5x) and a port expander (adress range 0x2x).

We now have the first board and try to take it into operation. The assembled INA reacts on address 0x40 when A0=Gnd, A1=Gnd and to 0x41 when A0=3.3V and A1=Gnd.

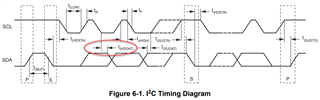

But when we connect A0 to SDA, the device reacts on 0x43 rather than 0x42. We use raspberry pi i2cdetect to find out which simply scans each I2C address. I2C signals seem good, speaking of edges and timing, freq=100kHz. The INA does not only react to a i2cdetect, but also can be read out using address 0x43, so it's not an error due to scanning I2C addresses.

What could be the root cause for this? When exactly does the INA adjusts its adress? Must there be an idle time before accessing the device after a previous I2C communication?

Any help appreciated

Harald

P.S. Datasheet reads "secondary I2C address". What does that mean? Is that just the regular I2C slave address?