Hi,

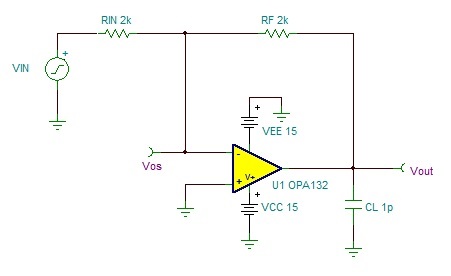

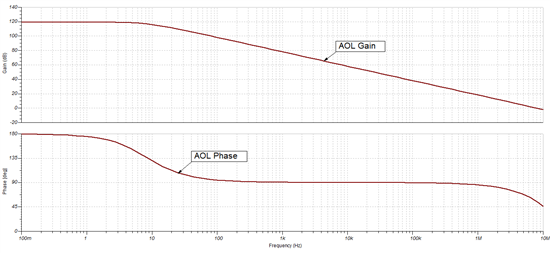

The pspice model of the opa132 (that I downloaded as Jan 27, 2104) has a strange open loop gain, the phase is rising. I have not encountered this problem with other pspice models of Texas Instruments amplifiers.

Could you please check the model ?

Thanks