Other Parts Discussed in Thread: LM2902

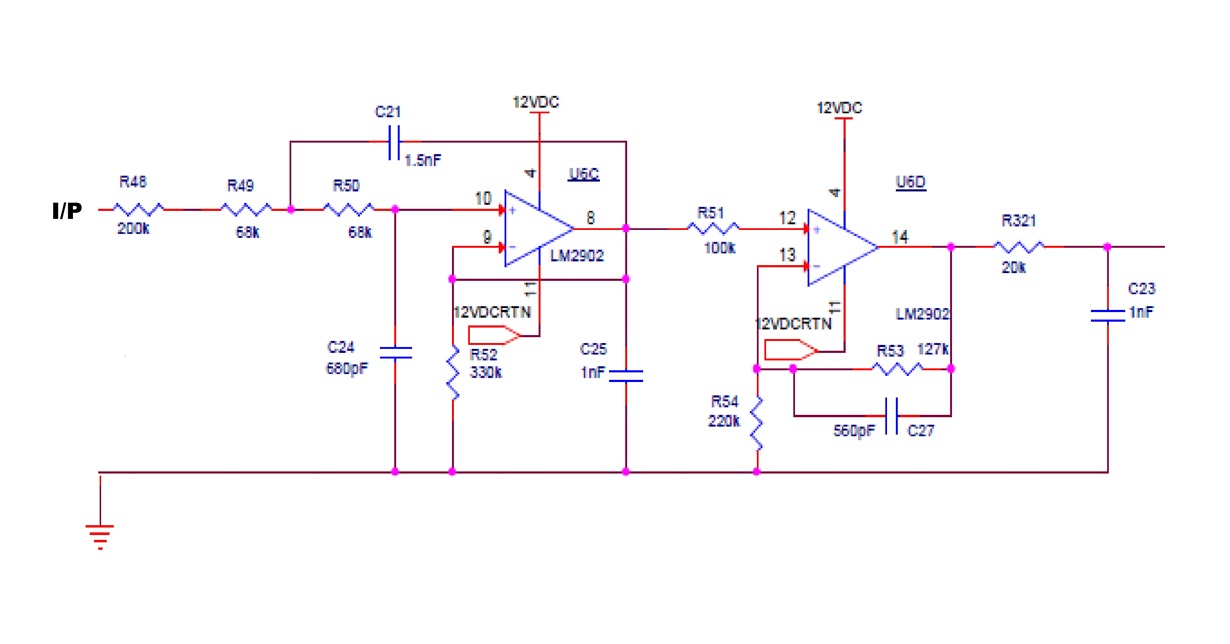

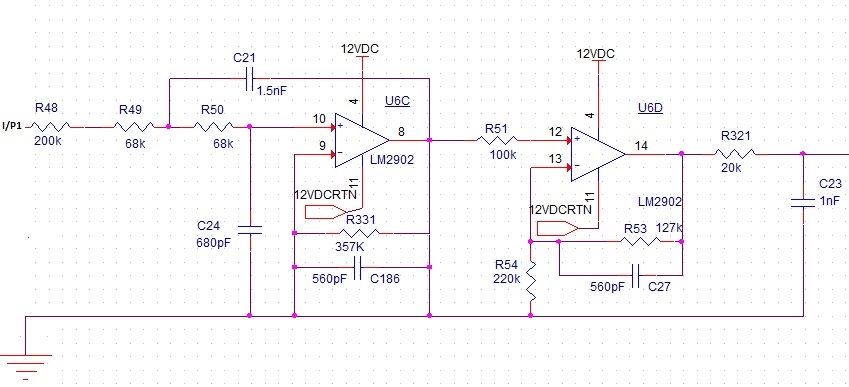

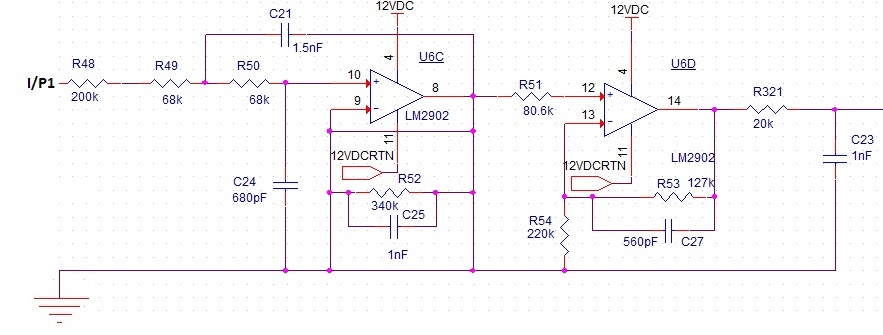

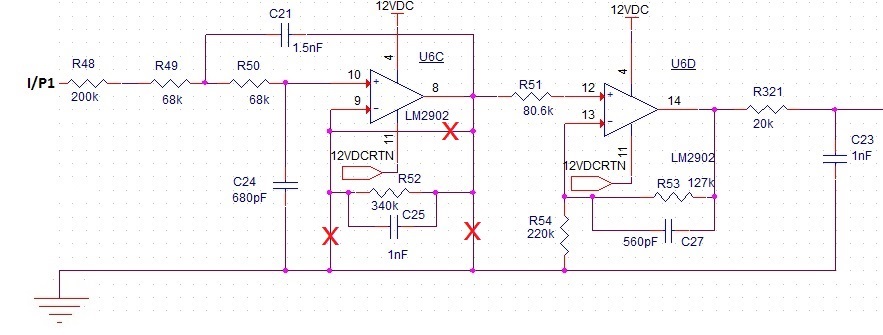

I am using LM2902KAVQDRQ1 for analog voltage amplification as shown in the circuit. The full circuit has a gain of 1.62 and the input range is from 0 - 1.88 V. The problem is that there is a variation of 5-20 mV at the output side(PIN NO 14). The resistor tolerance is 1% and capacitor tolerance is 5% in the circuit. Can you please suggest any improvements ?

Regards