Other Parts Discussed in Thread: OPA320, OPA197, OPA4197, OPA4191

Ref. Case CS0070966 (on TI support page) re-adressed to E2E

Original details:

Spike or distortion of the DC voltage output of the OpAmp (used as DC voltage level shifter and 2nd order LPF) coupled to ADC input of MCU NXP MKV42F256VLH16 not programmed (standard condition for hardware pre-test before programming)

OPAmp STM TS914I and TS924I don’t shows any problem

Please find below a detailed description of the problem with schematic and scope screenshots

We have our previous products in full production that uses this P/N since 2011

Now we are in components qualifying stage for a new product planned to replace the old ones

Problem Description

We encountered a problem coupling TI OpAmp TLC2274I to MCU NXP MKV42F256VLH16

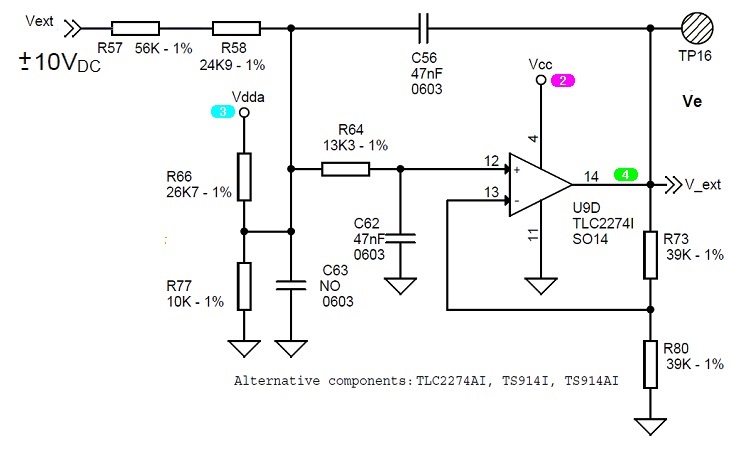

Such OpAmp is used as DC voltage level shifter and 2nd order LPF (Butterworth non inverting topology), as represented in Fig. 1

OpAmp Output (signal V_ext) is connected to ADCB_CH0 input of MCU (pin 7) by a passive RC filter (R=1Kohm, C=100pF)

Critical working condition is test #4 of Tab. 1 below reported actually planned to be the standard test condition for hardware (pre-test before programming)

In the same application and test conditions alternative OPAmp STM TS914I and TS924I don’t shows any problem

Operating conditions of all test

Input voltage range of voltage level shifter: Vext=±10Vdc

Output voltage range (OpAmp output): V_ext=0÷3,3V

Analog power supply: Vcc=5,5V

ADC power supply: Vdda=3,3V

Digital power supply: Vdd=3,3V

All ICs have obviously its own Bypass Capacitors connected as near as possible to their Power Supply pins

Fig. 1: Simplified electric diagram of DC voltage level shifter and 2nd order LPF

|

Test # |

Test configuration |

Vext applied |

Test Result |

NOTE |

|

1 |

MCU not programmed, no other signal applied except Vext |

-10 ÷ +10Vdc |

PASS |

|

|

2 |

MCU not programmed, signals applied as per Tab. 2 + Vext |

-10 ÷ 0Vdc |

PASS |

|

|

3 |

MCU not programmed, signals applied as per Tab. 2 + Vext (same conditions of test #2) |

0 ÷ 4,85Vdc |

PASS? |

Voltage spike on OpAmp output with amplitude depending by Vext voltage value applied fig. 2 - CH4 (VEXT0003.png) (@ Input voltage Vext=4,85V) |

|

4 |

MCU not programmed, signals applied as per Tab. 2 + Vext (same conditions of test #2) |

5 ÷ 10Vdc |

FAIL |

Distortion of the OpAmp output with amplitude depending by Vext voltage value applied fig. 3 - CH4 (VEXT0006.png) (@Input voltage Vext=9V) |

|

5 |

MCU programmed, signals applied as per Tab. 1 + Vext |

-10 ÷ +10Vdc |

PASS |

|

Tab. 1 schematic description of the problem encountered with TI Op amp TLC2274I

Signals applied to MCU ADC_CH0÷CH3 are obtained from other TLC2274I NOT contained in the case of D.U.T.

Vcc, Vdd, Vdda are not afflicted by voltages pulses or distortion (see. Fig. 3 and 4 CH2=Vcc and CH3=Vdda)

Voltage spikes and voltage distortion on OpAmp output are synchronous with AC signals applied to other ADC

(verified by triggering voltage spikes and modifying frequency of ADCA_CH0÷CH3 voltage applied)

Capacitor C63 is NOT assembled (test with 100nF had a negative result: C63 don’t solve the problem)

|

Signal name |

MCU pin |

Average DC component |

Peak-to-Peak AC component |

Reference Image |

|

ADCA_CH0_Vaux |

5 |

+1,65V |

1,34V |

Fig. 2 - file MAVR3001.png |

|

ADCA_CH1_VU |

6 |

+1,65V |

1V |

|

|

ADCA_CH2_VV |

9 |

+1,65V |

1V |

|

|

ADCA_CH3_VW |

10 |

+1,65V |

1V |

Tab. 2: additional signals applied to MCU ADC_CH0÷CH3 test #2 ÷ #5

Fig. 2: additional signals applied to MCU ADC_CH0÷CH3 test #2 ÷ #5 - file MAVR3001.png

fig. 3 - Level Shifter Input voltage Vext=4,85V - file: VEXT0003.png - note voltage spikes on TLC2274 output (CH4)

fig. 3 - Level Shifter Input voltage Vext=9V - file: VEXT0006.png - note output voltage distorsion on TLC2274 output (CH4)

As per information available on NXP MCU data sheet, in default mode pin 7 of MCU is configured as ADCB_CH0 input, its equivalent circuit cannot explain the problem described.

In conclusion the problem seems related to:

- TI TLC2274I OpAmp

- Unconfigured inputs of MCU NXP MKV42F256VLH16

- AC signal applied to other ADC channels (ADCA_CH0÷CH3)

Could you supply an explication?

Do you think there’s some solution rather than modify test procedure?