Other Parts Discussed in Thread: INA819, INA818,

Hi,

1) Is the only difference between the INA818 and INA819 the pin-out? The INA818 being a superior version of the INA118. Used with a MPX10DP Pressure Sensor.

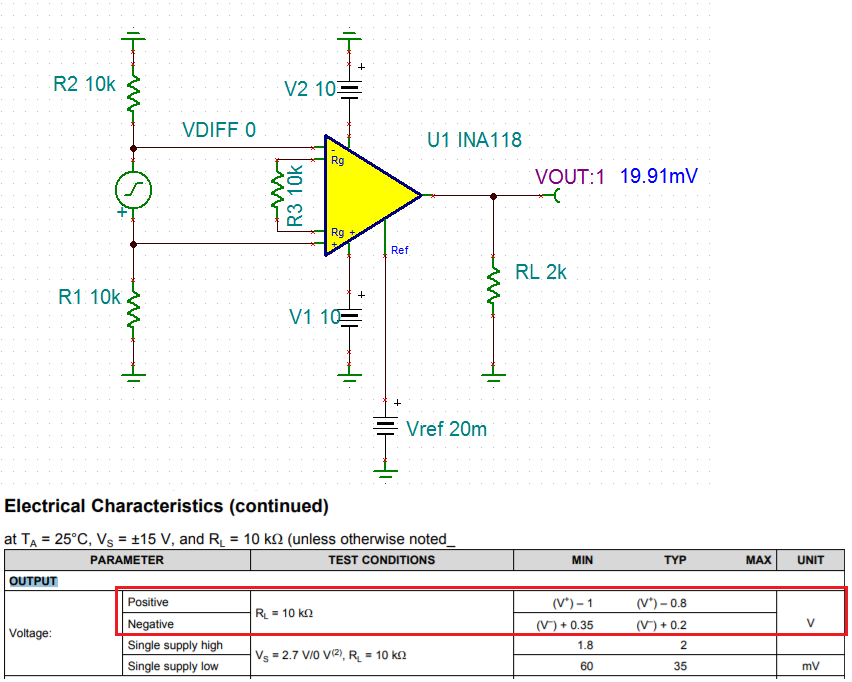

2) The application is taking an MPX10DP differential pressure sensor (span is 0mV to 40mV)(subtracting the Pressure Sensor's DC Offset (20mV) - solved) and Differential-End to Single-End amplifying by 1000 to go into an ADC (span 0V to 5V). INA118 is on 0V to 5V rails. They want the INA118/INA818 to have a uni-polar output from 0V to 5V.

A big DC Offset issue was noticed with the INA118. That may be reduced by going to the INA818 (Unless you suggest something better).

But it go me wondering...

If I need to use a low impedance buffer to take the REF pin a few milli-volts below the V- rail (to reduce the DC Offset), will that definitely cause issues (or will that happen if the voltage is more like a diode drop?)?

The obvious answer is; that if you CAN take the REF pin below V-, then why don't you power the INA118 from the more negative voltage.

True, that's now what we will do on Rev 2.

But as I said, I was wondering....

Is a few mV - too much?

Cheers,

Peter