Hi Team,

Our customer is evaluating INA180A3QDBVRQ1 at Figure44 circuit.

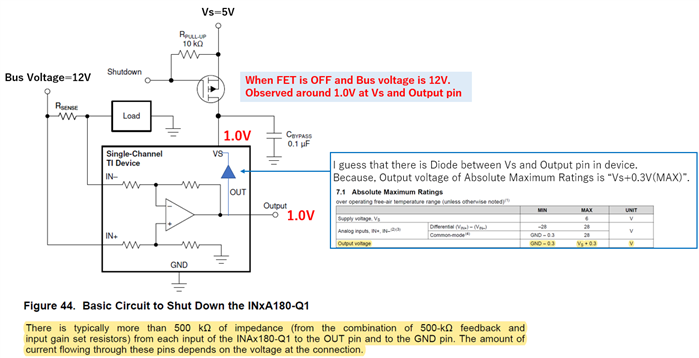

When FET is OFF and Bus voltage is 12V, observed around 1.0V at Vs and Output pin.

I guess that there is Diode between Vs and Output pin in device and it is correct behavior.

Is my understanding correct?

And, could you please let us know the workaround if you have any information(idea)?

Regards,

Hide