Other Parts Discussed in Thread: OPA2320

Hi guys, I'm Jose.

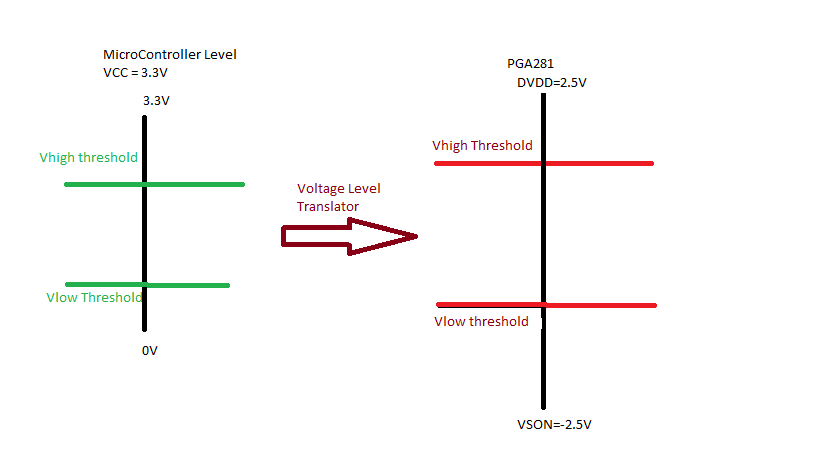

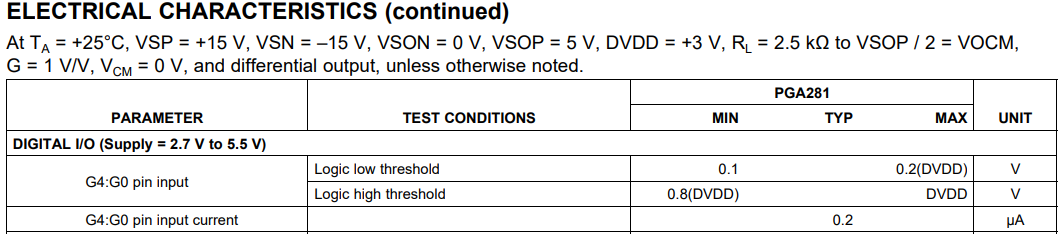

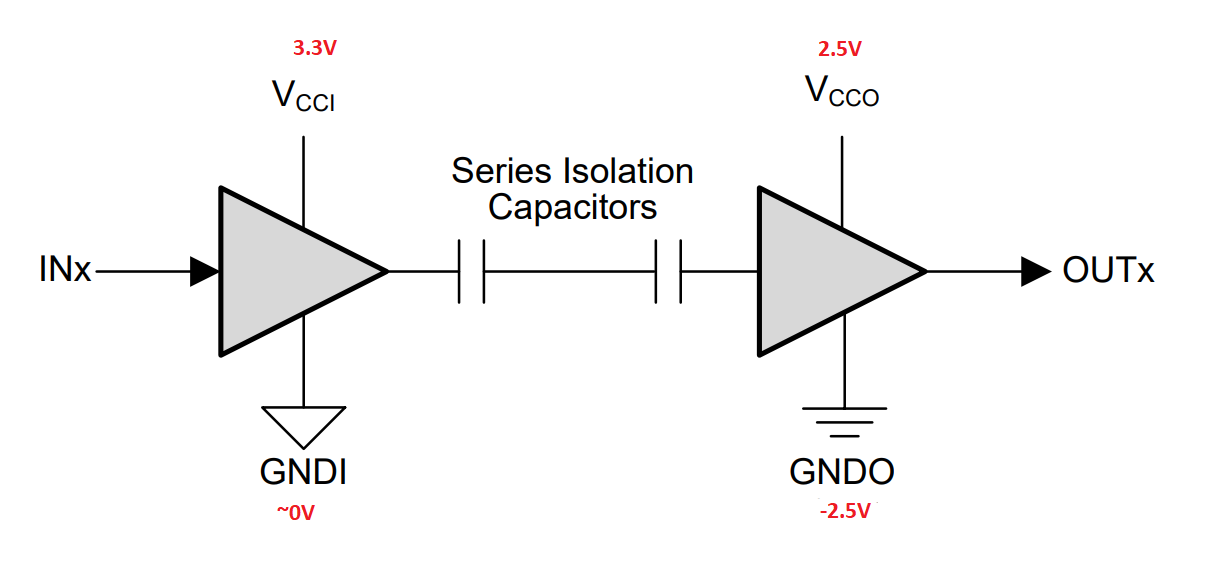

I want to use the PGA281. For VSOP = 2.5 V and VSON = -2.5V. When using a negative supply for VSON, the datasheets says "The negative digital supply is connected to the VSON pin. Take care if using split supplies on the VSOP and VSON pin because the logic low and high thresholds are determined by DVDD and VSON. In normal operation, VSON is connected to the system ground."

I've been seen a simulation which I downloaded from a link in the datasheet. Basically I modified it because all examples I found in the datasheet are specified for VSON=GND.

So, I want to know what would be the digital thresholds when using a VSON=-2.5. In the simulation I have:

VSOP=2.5 and VSON=-2.5

VOCM = 0V

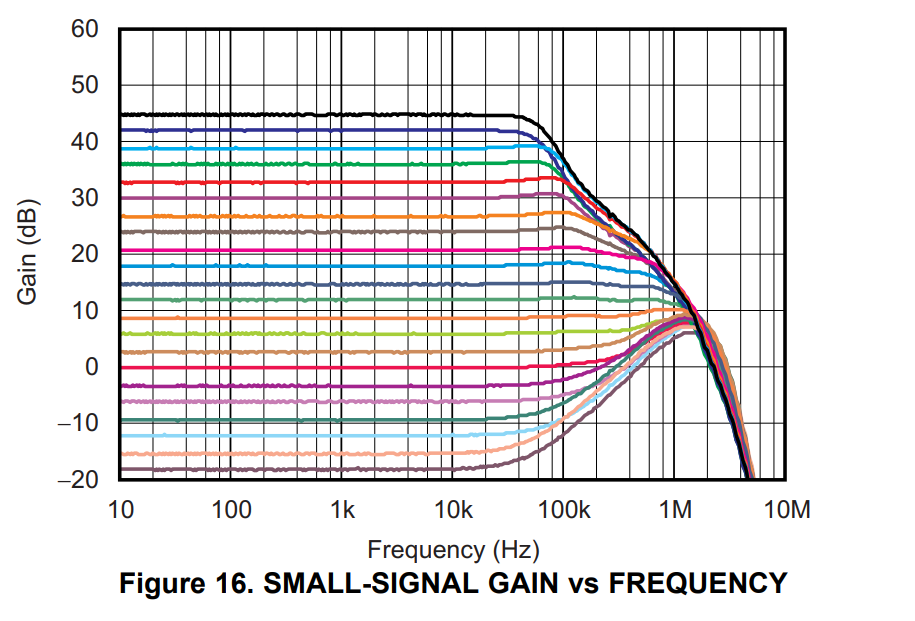

INP = sine signal of 500mV and 100kHz

INN = sine signal of -500mV and 100kHz

GAIN = 1

DVDD= 2.5V ( As DVDD-VSON = 5 is correct because 2.7<5 <5.5 as per the datasheet indication).

Thank you, I hope someone can explain this to me, and get the correct simulation.