Hey team,

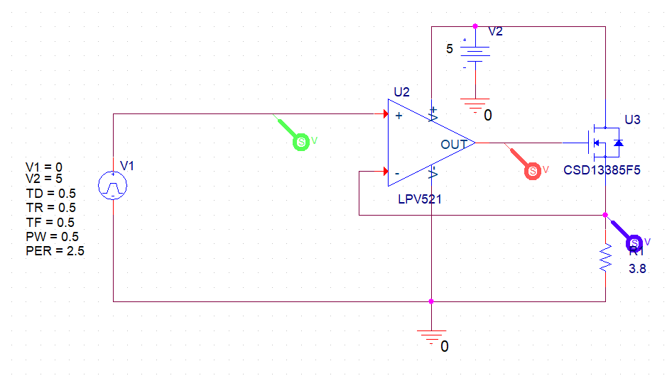

Just wanted to run some simulations by you for a voltage controlled current sink design. I had one odd measurement that I was curious to get your thoughts on. Attached is the schematic and graph in question.

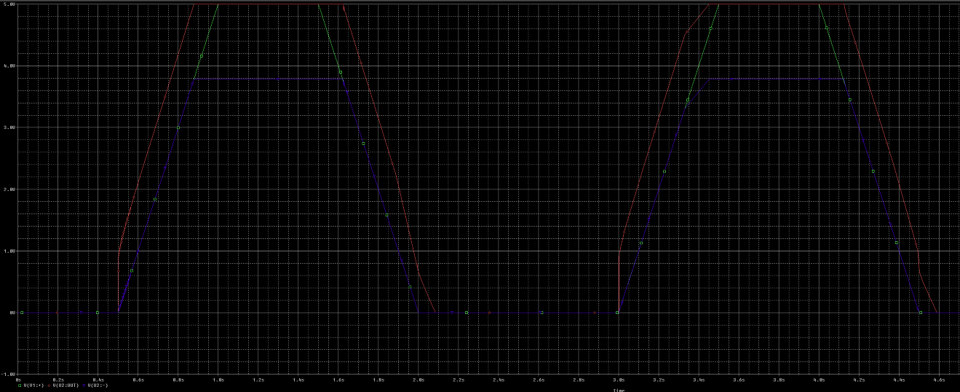

The red line above shows the voltage at the gate (output of the amplifier), the blue line is the output voltage at the source (negative terminal of the amplifier), and the green line is the input voltage.

The area I'm curious about is the output of the amplifier being around 1.2V higher than the input towards the start of the simulation. My assumption would be it has to do with negative feedback, but the graph doesn't look like how I would imagine it to be. I would expect the voltage over the negative terminal to be 0V until Vgs (or Vthreshold) is hit from the nFET (which is 1.2V maximum).

I'm sure I'm just missing something fundamental here so I appreciate the help! I'm aware that my design could likely be improved by adding a voltage divider at the input to pull the 5V down lower so that the tracking extends from 0-5V rather than 0-3.8V.

Cheers,

Cameron