Hello, Team,

The customer is considering to use TL331-Q1 and have 3 questions related to the Application Report (https://www.ti.com/lit/an/snoaa35a/snoaa35a.pdf).

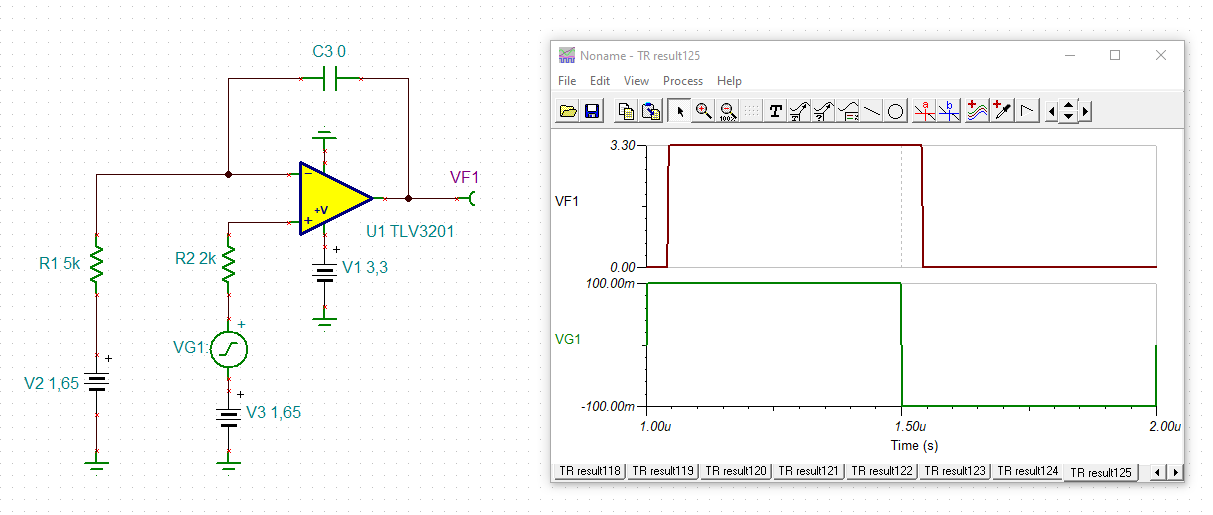

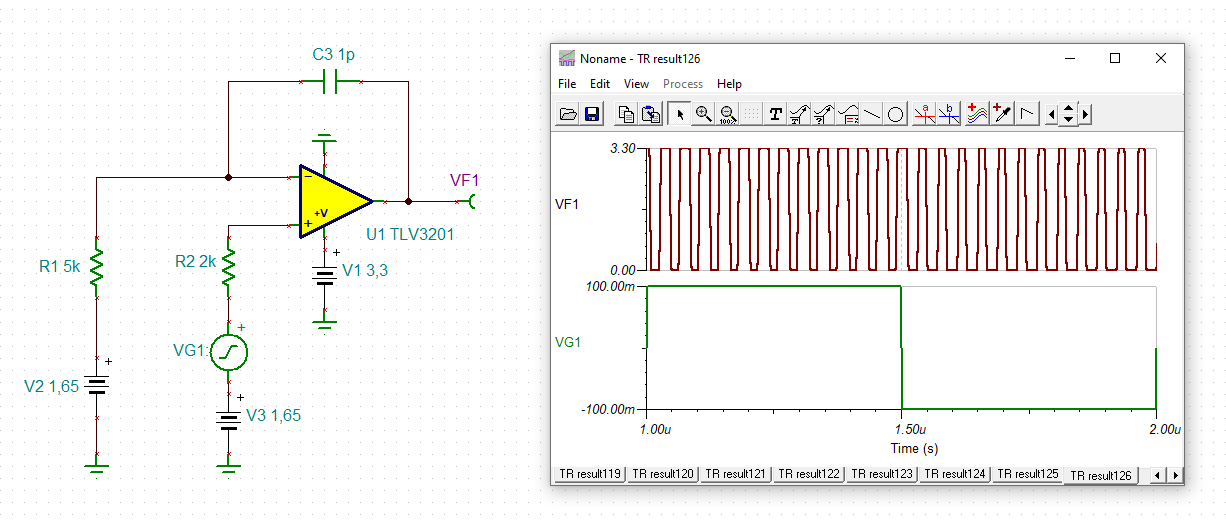

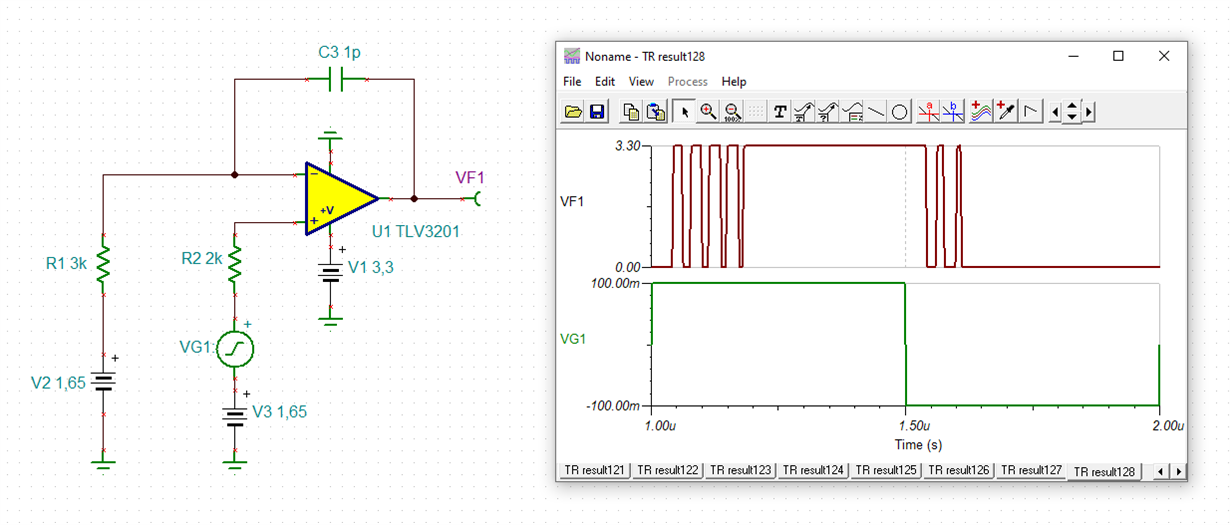

- It is stated in section 2.8 that in order to prevent oscillations and false-triggering, the output and input traces need to be kept separated when the source impedance is greater than 25kOhm.

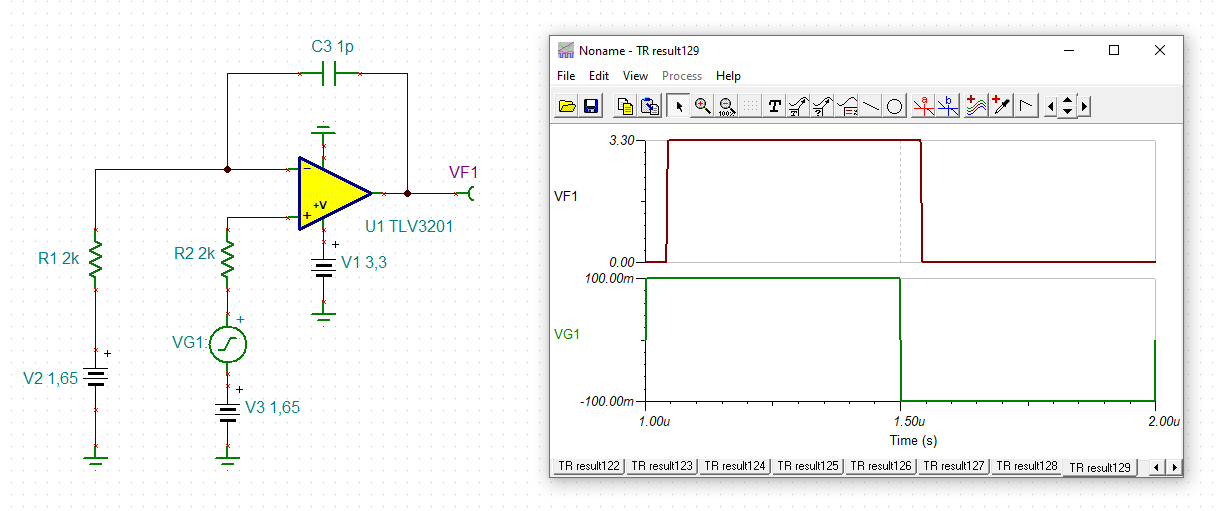

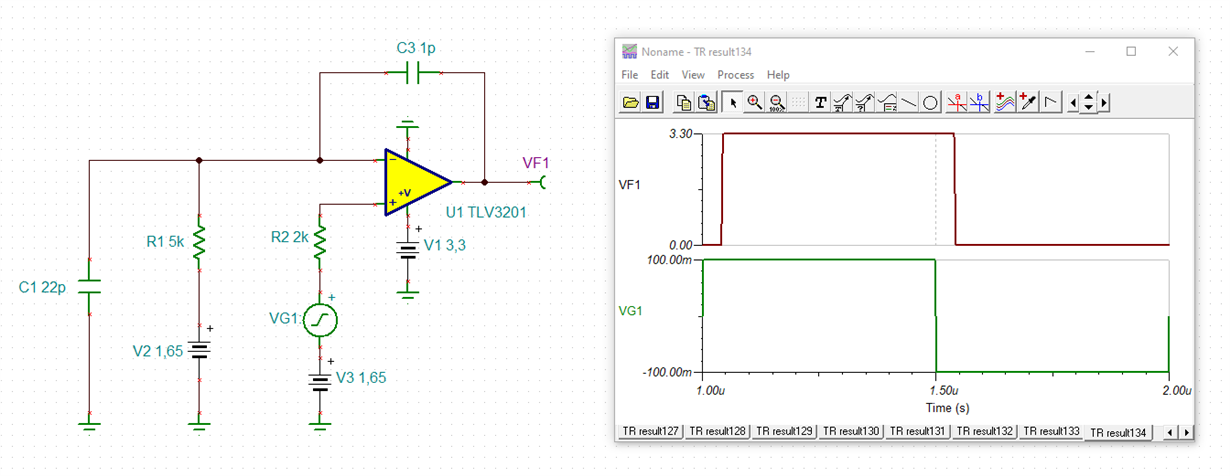

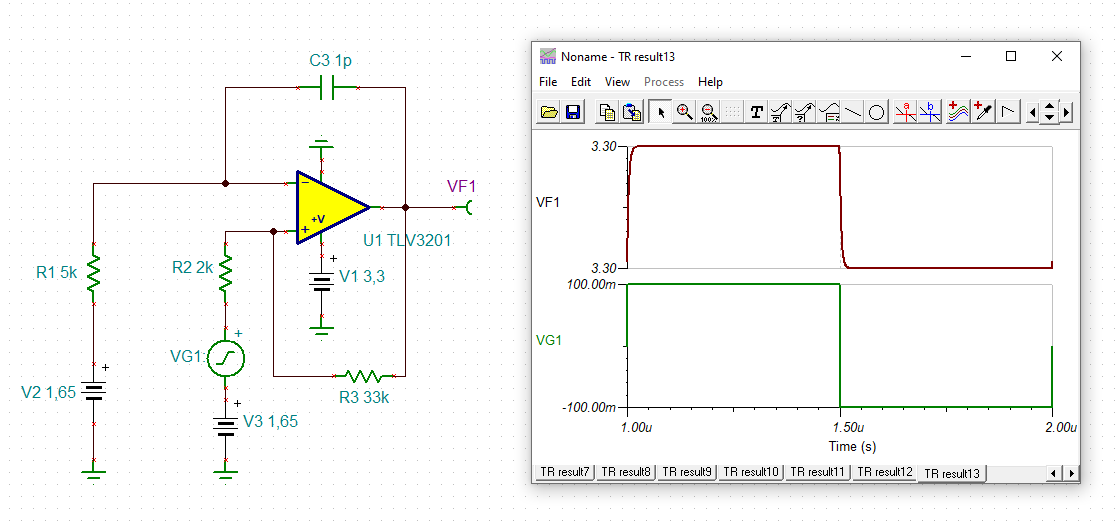

Is there any technical reason behind this "25kOhm" value? If so, could you please explain why it is "25kOhm"? - After sorting out the layout, what kind of method can we use to evaluate a margin in terms of the oscillation?

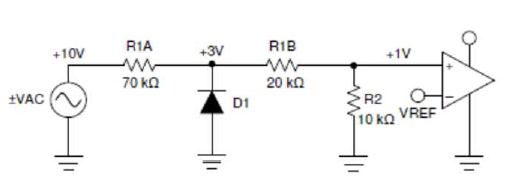

- In the circuit given in the section 2.9.2.1, the source seems to be divided into R1A (70kOhm) and R1B (20kOhm).

Can this be regarded as the source being under "25kOhm"?

Thanks,

Masaru