Part Number: TPA3128D2

Other Parts Discussed in Thread: TPA3132D2, TPA3118D2, TPA3116D2, TPA3130D2, TPA3131D2

I'm having some issues with a new TPA3128D2 implementation when using 1SPW mode. When powering the device on (with open inputs) i can hear a clicking sound on the outputs which refers to stepped bias response on the inputs.

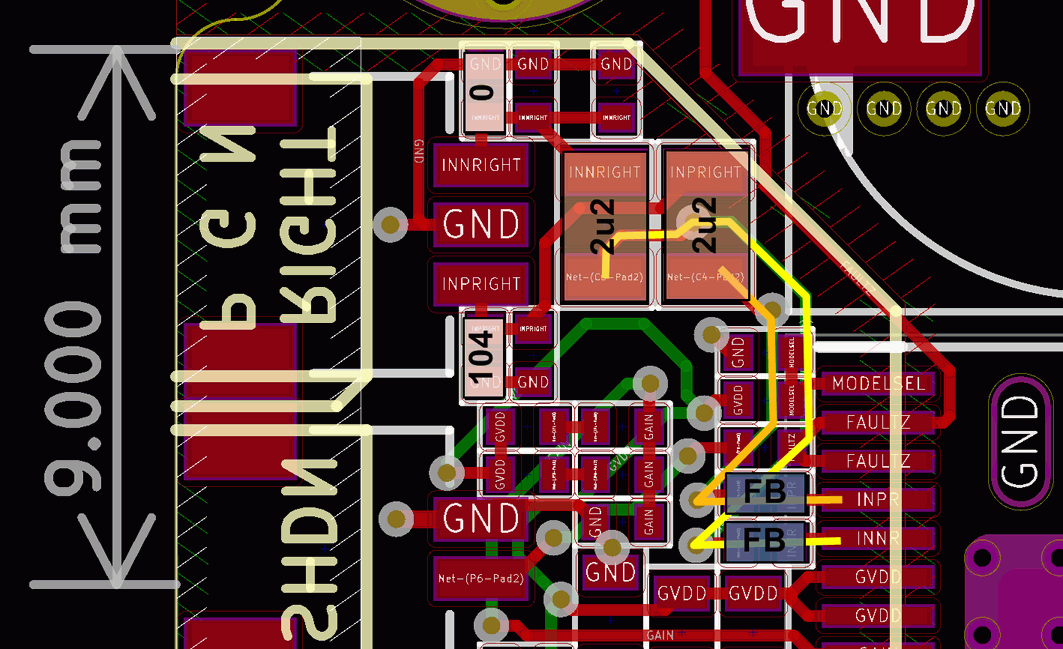

IC is configured as:

600kHz 1SPW

SE input (ground refered)

2u2F input coupling caps

1s power on mute

Weak 100k "pulldown" resistor to GND on the inputs before coupling-caps

System overview:

The clicking noise looks like this on power on:

Touching the inputs while powered on also results in clikcing noise as shown here:

As said, this isn't noticeable when using BD modulation. Any ideas?

Best regards,

Christian

www.360customs.de