Other Parts Discussed in Thread: REF3333, TIDA-00909, , INA282

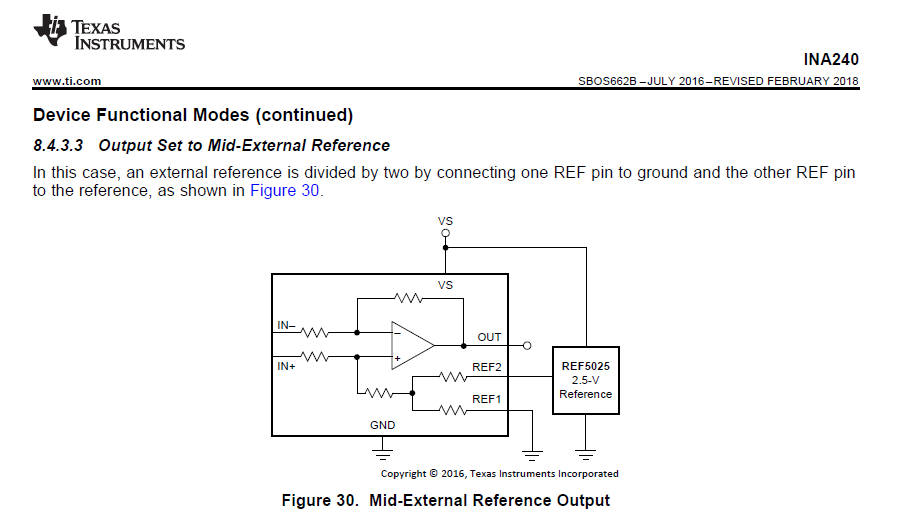

Is it possible to simulate the effect of PWM duty cycle speed increasing output amplitude with full REF being added to the shunts current measurement? Transient analysis of a shunt (uV/A) is ok until the test bench speed of the PWM duty starts to overtake REF1+2 reference and incorrectly adding what seems is entire REF into the output magnitude. How can that attribute be evaluated in Tina or even stopped on test bench without adding a resistive output divider to ground?

Currently there are No 100n caps on each A1 REF1+2 which seems to increase output magnitude after omitting them from transient analysis, also on our test bench. It would seem 10uf placed on the +1.225v precision reference would be ample filtering alone. R2,R18 were (0R) and C12,C16 (100n) for the A2 test bench, produced the same excessive output amplitude as the PWM duty cycle increased beyond the actual shunt 500uv/A current measurement. Other words there should be less amplitude relative shunts 500uV/A * 20 gain producing only 10mV/A on INA output added to the REF floor of 1.224v.