Other Parts Discussed in Thread: TM4C1294NCPDT, UCC27714, EK-TM4C1294XL, INA282

Hello again,

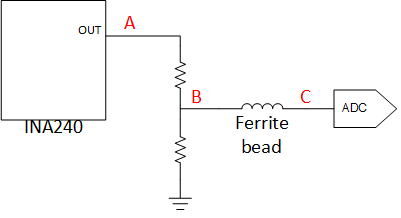

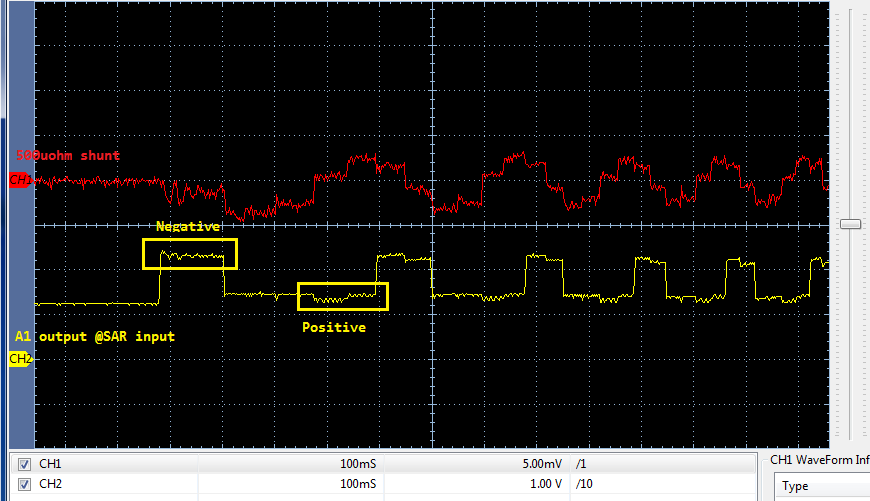

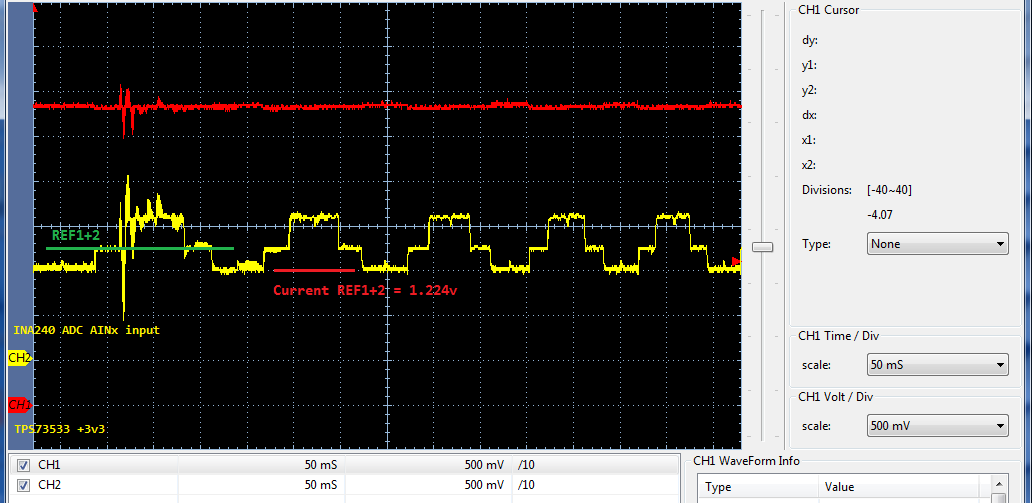

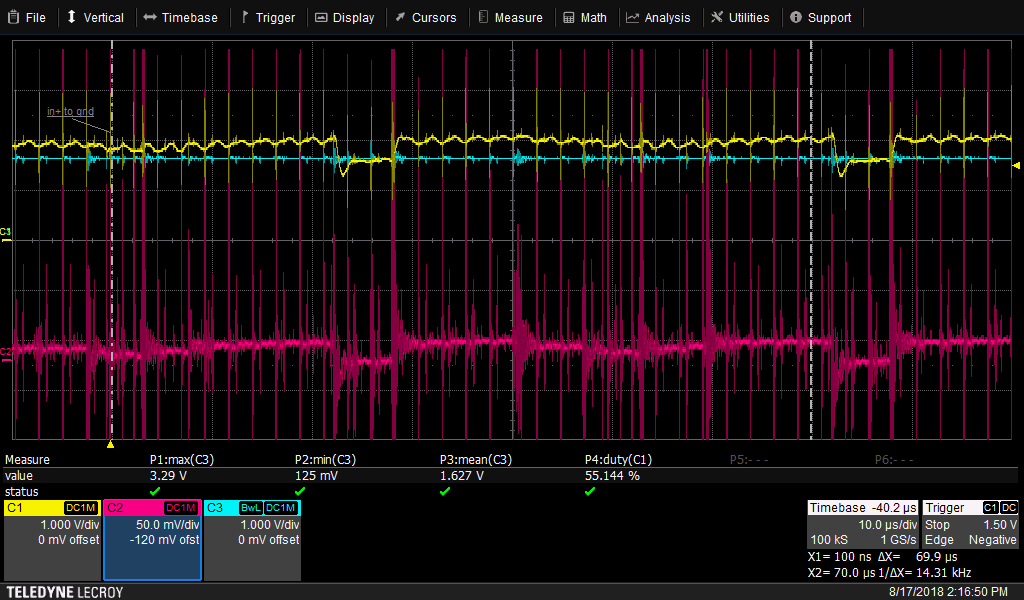

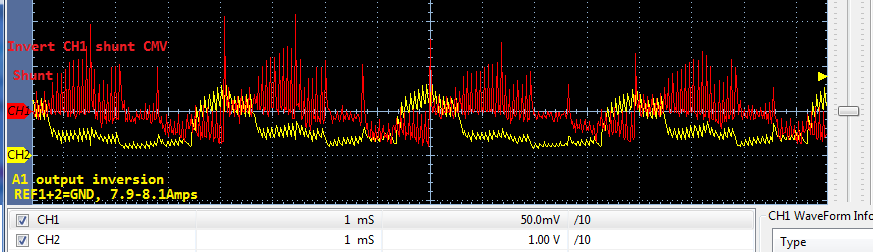

Many captures posted A1/A2 signals we of late see output inversion occurring unrelated to REF1+2 pins configuration.

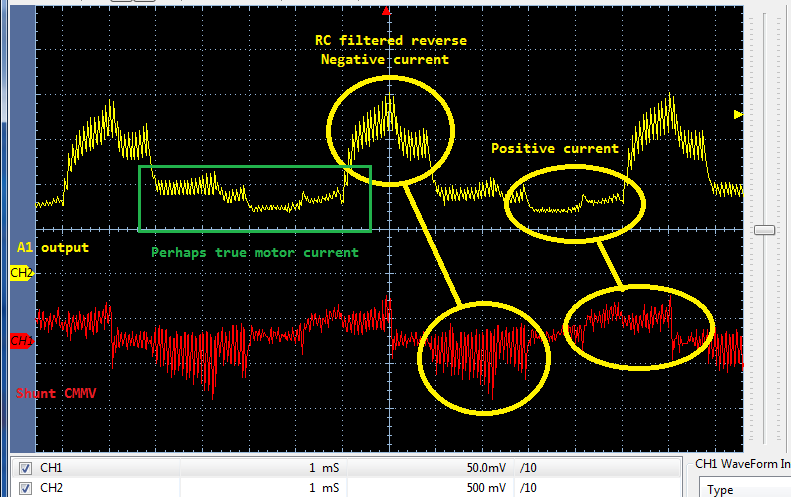

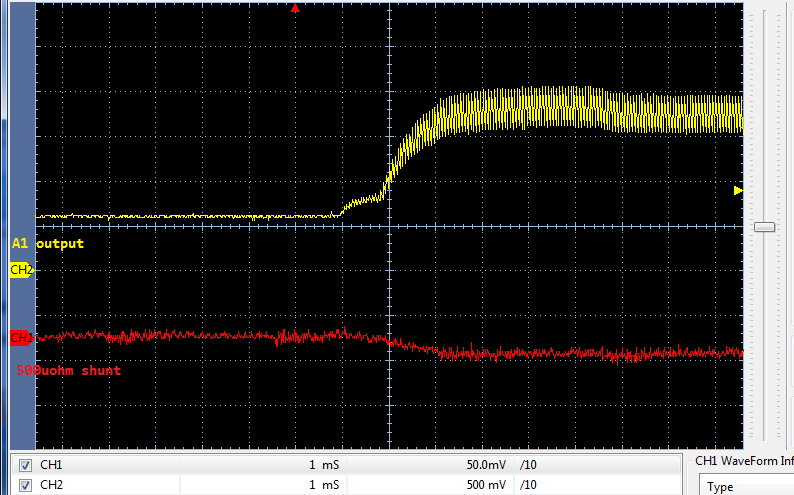

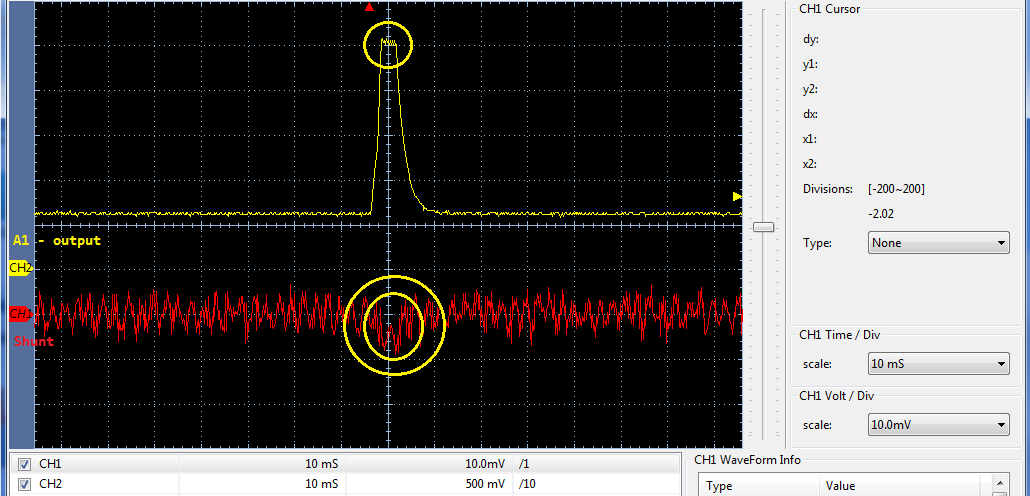

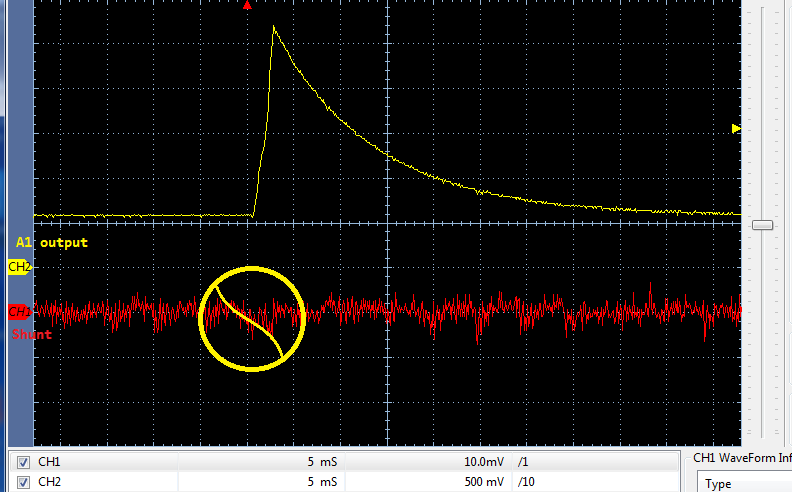

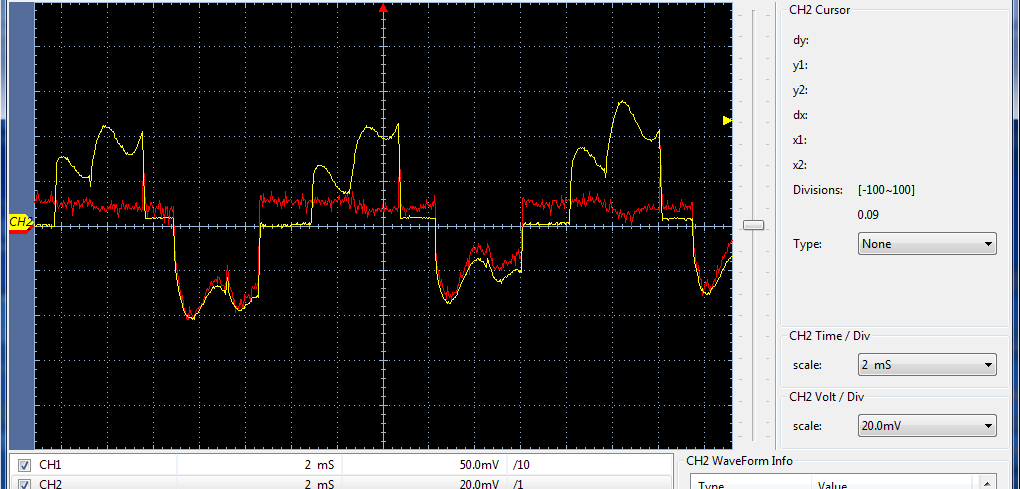

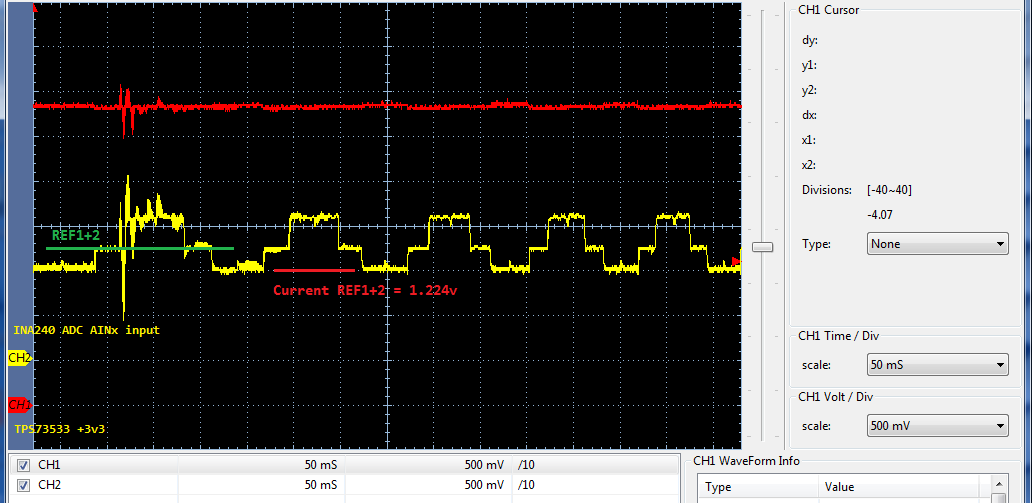

Basically the inverted output produces inverted peaks meant for mid negative REF. The output solution (A1/A2) seemingly produces inverse shunt or negative current on top and positive current on the bottom just above +1.224 REF1+2 rail. Otherwise the REF should divide the output signal mid supply of REF +1.224v when VS=3v34.

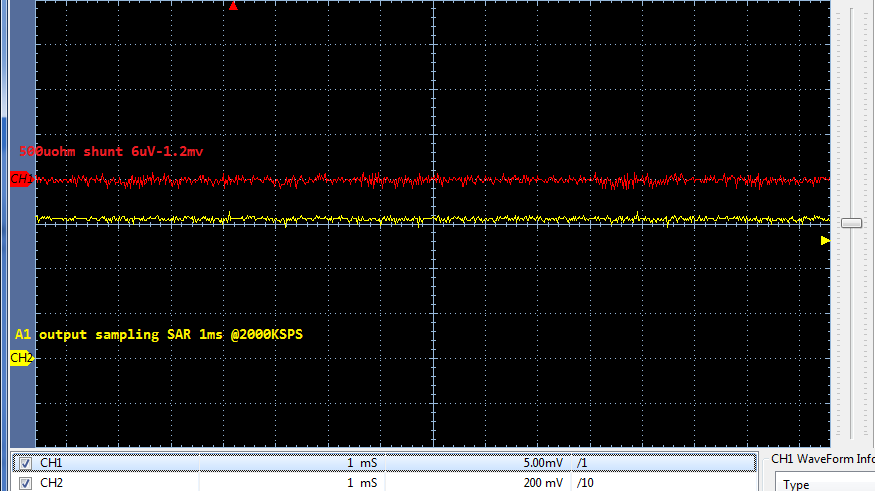

The A1 +IN pin faces +VCM source (from low side perspective) and -IN pin connects to GND. Datasheet suggests REF1+2 or 1/2 REF precision reference does not invert shunt CMV or +IN entering the non-inverting amplifier input. The 240 datasheet REF disclosure text mirrors 282 datasheet REF disclosure text, yet 240 inputs act opposite of 282 relative to REF configuration. So it would seem as the A1 output is then RC filtered the output inversion of shunt input signal widens above REF as below capture shows. Reported similar A1 behavior this forum was never acted upon by TI engineering to later include datasheet updates and proper CUT showing any laboratory testing of REF for all voltages in the VS range 2v7-5v5.

CH2 represent PWM cycle by cycle measures (note) ride above REF relative to shunt input polarity meant for mid supply, not to be added to REF. Perhaps the datasheet incorrectly characterized REF pin behavior as it relates to VS=3v3 and or REF1+2=1.224v? Otherwise REF pin violates datasheet specifications in the absence of REF pin testing below CMV+12, VS+5.