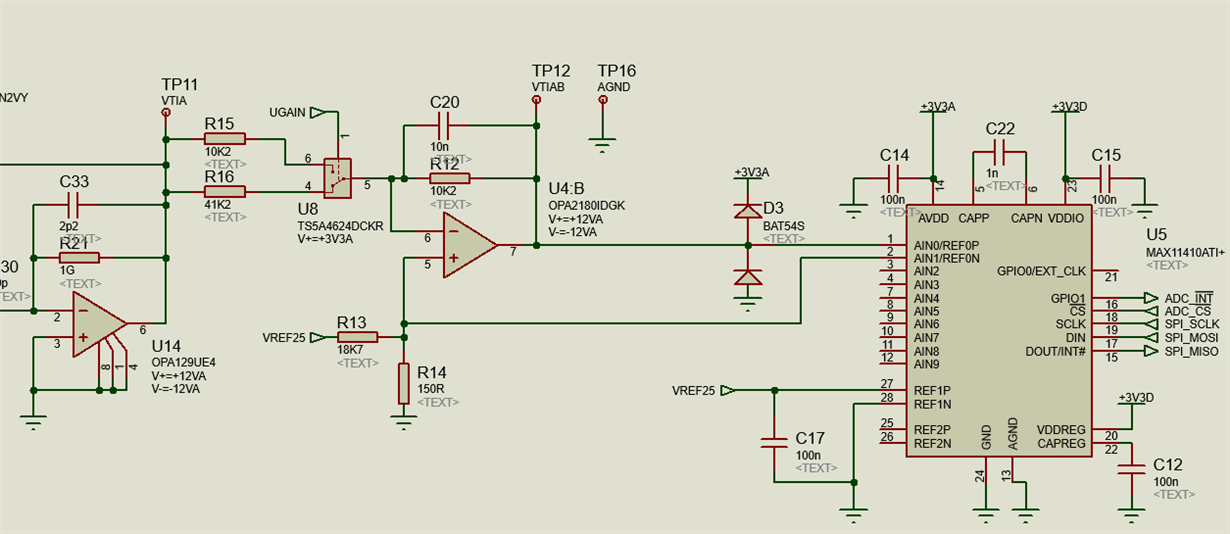

I'm using half of an OPA2180 to invert and add a small offset to the output of a transimpedance amplifier. See circuit below. Signal from transimpedance amplifier is applied directly in place of VS2 (hereafter called, the input), and spans around 0 to -10V. Vout drives the next stage of the circuit, an ADC input.

At the non-inverting input, the resistor divider sets 19.9mV. So, I would expect the output to be (19.9mV +-75uV) * noise_gain, where the 75uV is the max. offset error for the OPA2180, and the noise gain is 1 + (10k2/41k2). I.e. output should be 24.8mV +/- 90uV or so depending on the offset voltage of the op-amp sample.

However, in the real circuit, under the same input conditions, I measure an output voltage of around 22.36mV, about 2.5mV less than expected.

I then shorted the 150 ohm divider resistor, such that now, both the input (VS2) and the non-inverting input were 0V. I expected the output to be the op-amp offset voltage, i.e. +/-75uV. Instead, I measured -3mV on the output. That seems to me as though the op-amp is exhibiting an offset voltage tens of times bigger than the expected 75uV. I did also try another sample of the op-amp, and got the same behaviour.

What am I missing?