Other Parts Discussed in Thread: INA282, TIDA-00909

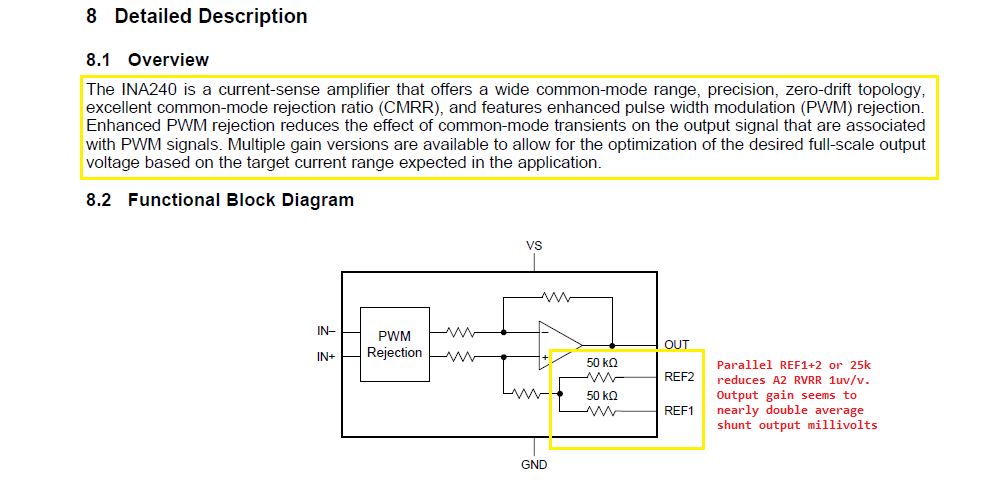

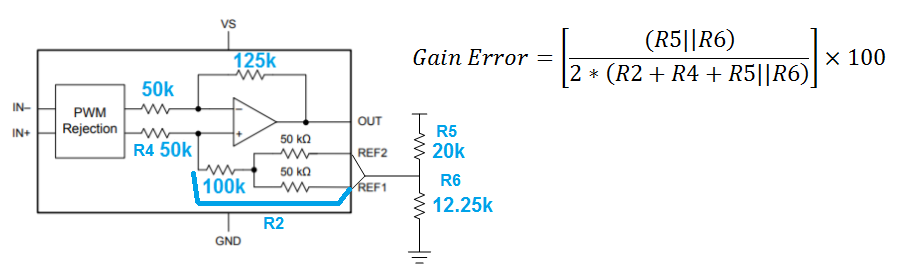

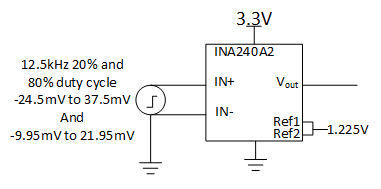

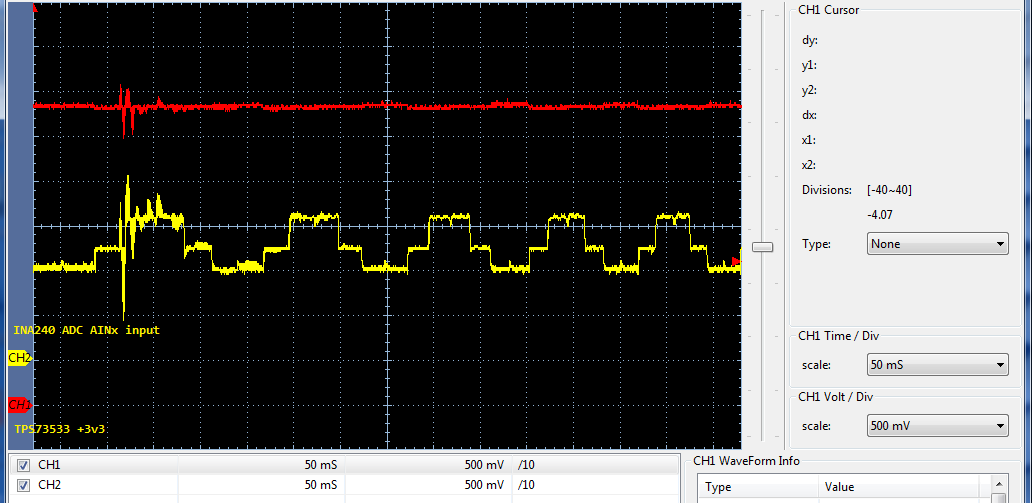

It would seem the datasheet analysis section leaves out very important factual info, REF1+2 divides A2 RVRR (2uv/v) effecting amp gain and noise immunity. Effectively lowers disclosed REF noise rejection and increases 50v/v gain to near 100v/v.

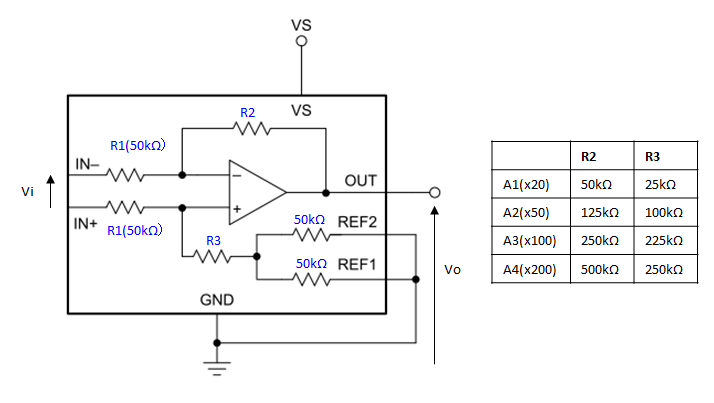

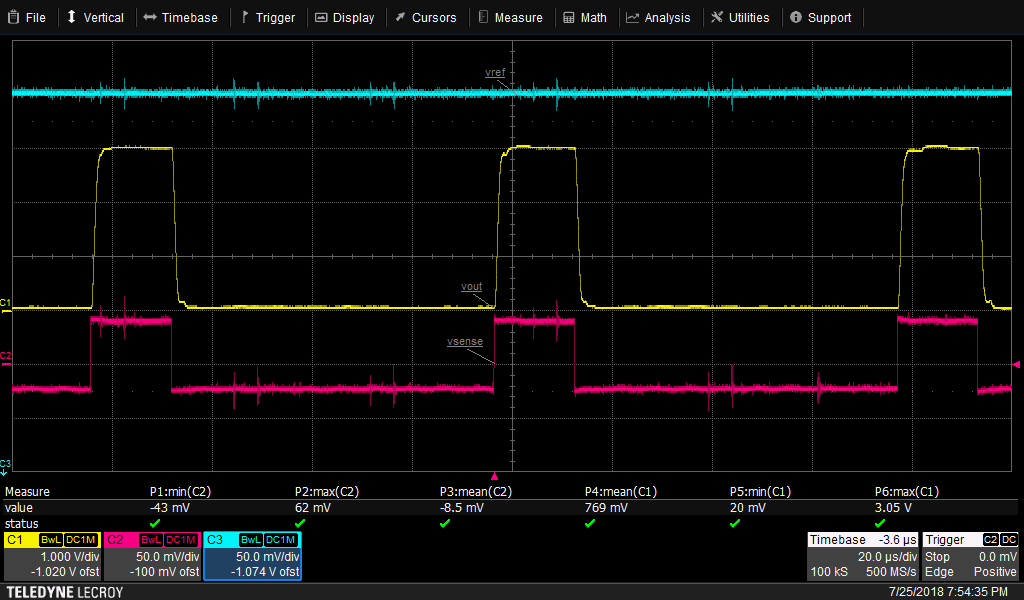

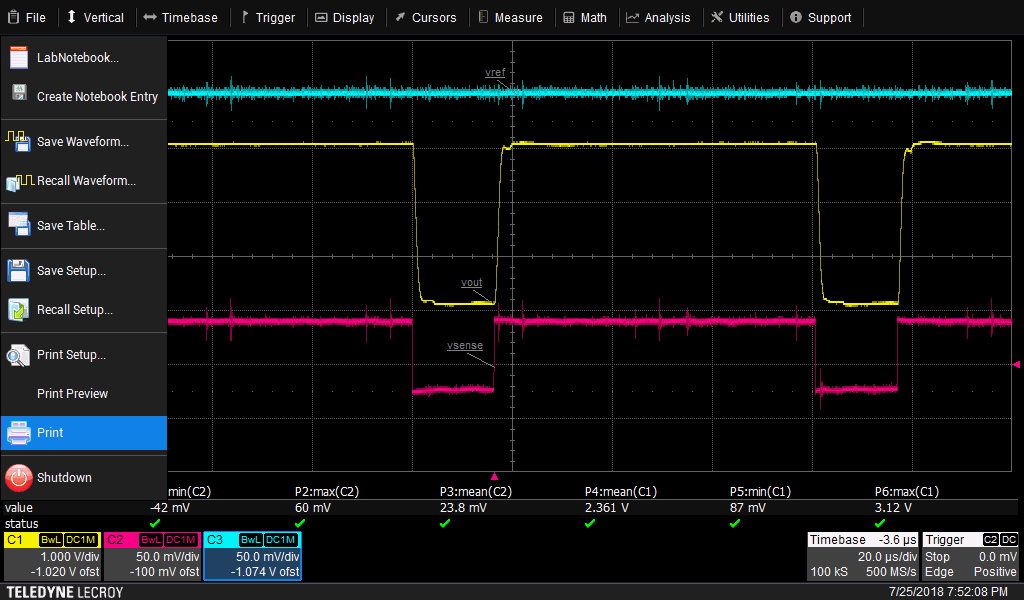

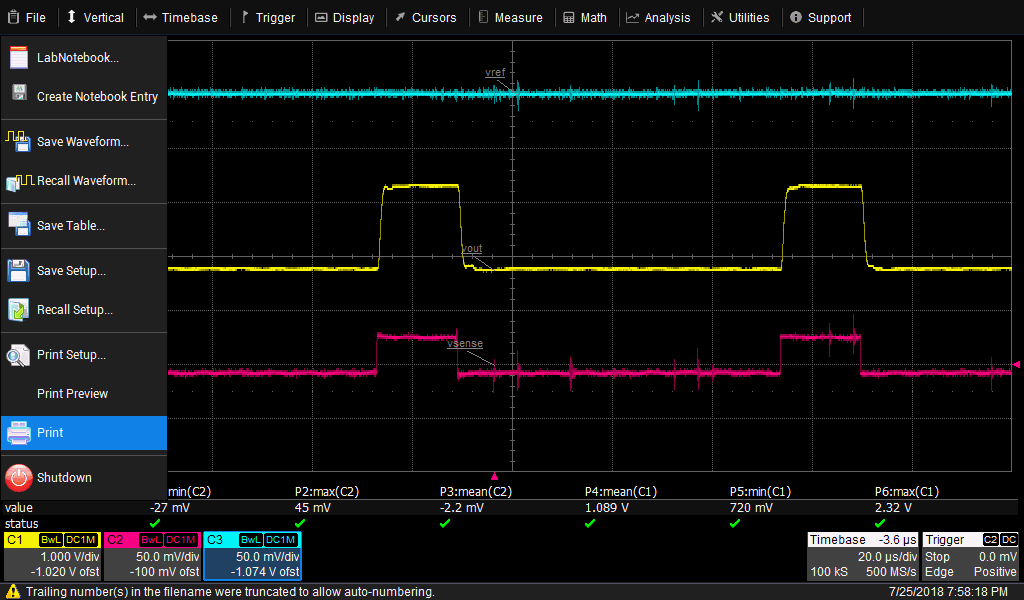

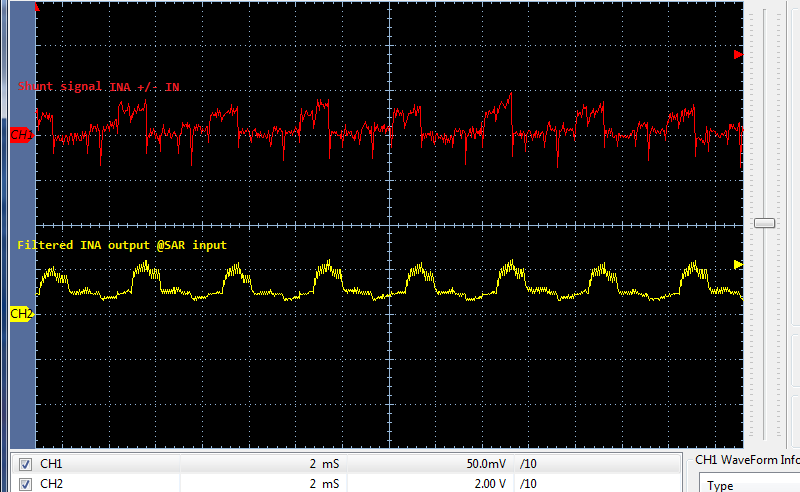

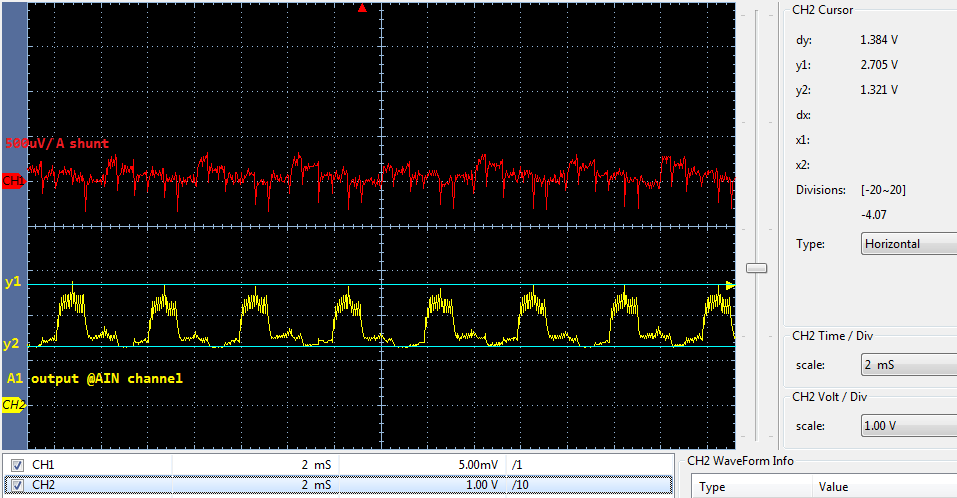

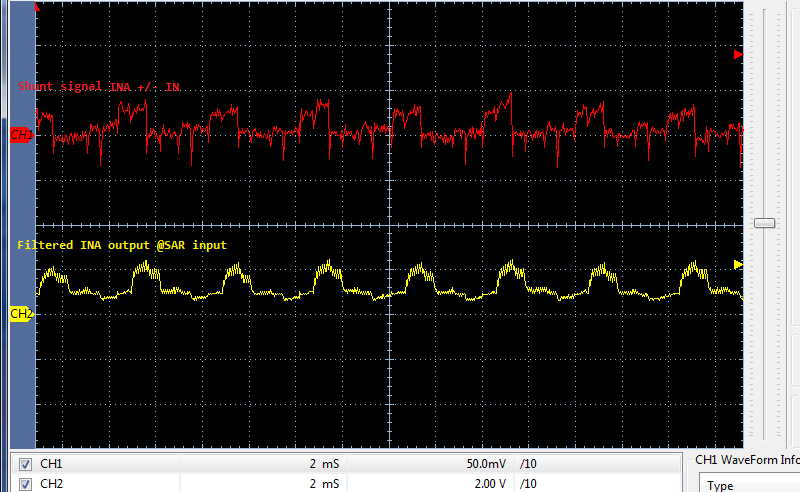

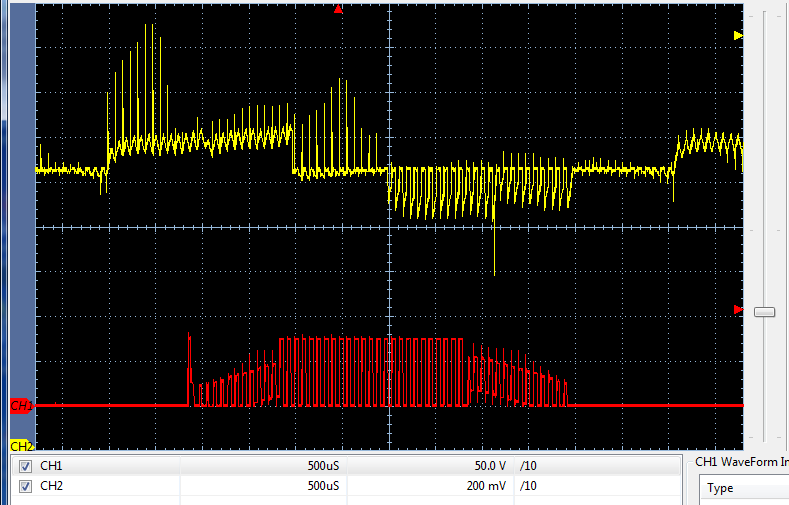

A 500uv/A shunt should produce 25mv/A in all disclosed REF configurations and actually produces 75 - 100mv/A when REF's are tied together. Tina INA240A2 DC or transient analysis macro is not producing correct output results for REF1+2 tied to external reference. Otherwise certain configurations of REF pins mislead customers in the design stage by plotting false data. Tina INA240 model is not disclosed as being DC model only and should produce correct transient analysis plot results for different configurations of REF pins and chosen shunt resistance values.

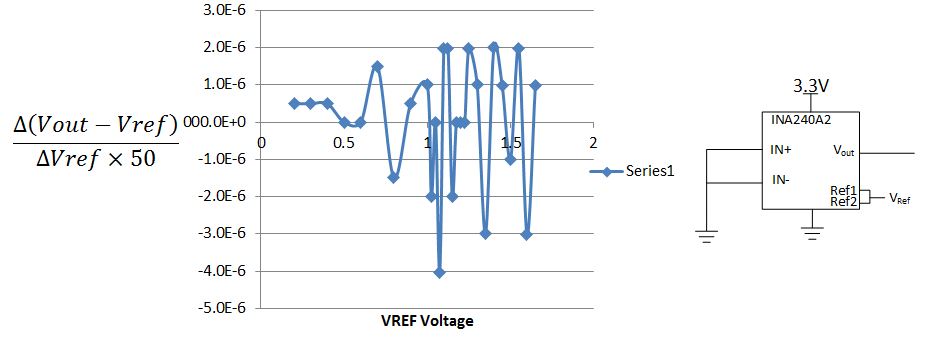

When REF1+2 pins are tied to an external reference the A2 50v/v gain nearly doubles, e.g. 50% error occurs as REF1+2 are below mid supply (+1.65v). Ideally we need to reduce REF1+2 below our +1.225v external precision reference to reduce output gain error %, not increase error as stated in datasheet, e.g. REF1/2 pins are above ground.

That part of the datasheet as from our evaluation (REF1+2 external reference) violates Tina models and the electrical specifications section of disclosed amplifier gains. Perhaps lab can revisit the electrical specifications/analysis and total error sections to list WA for errata being disclosed?