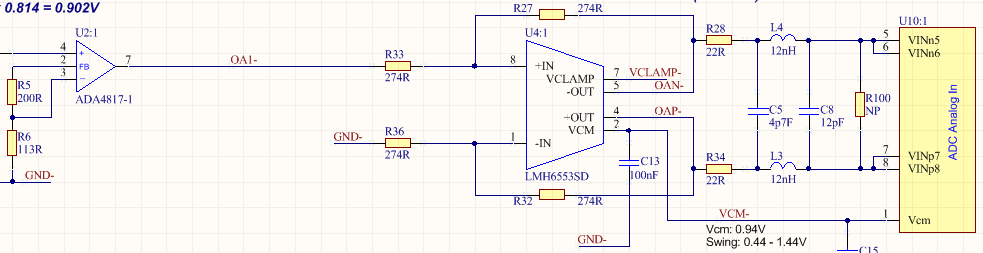

Follow up questions relating to this post:

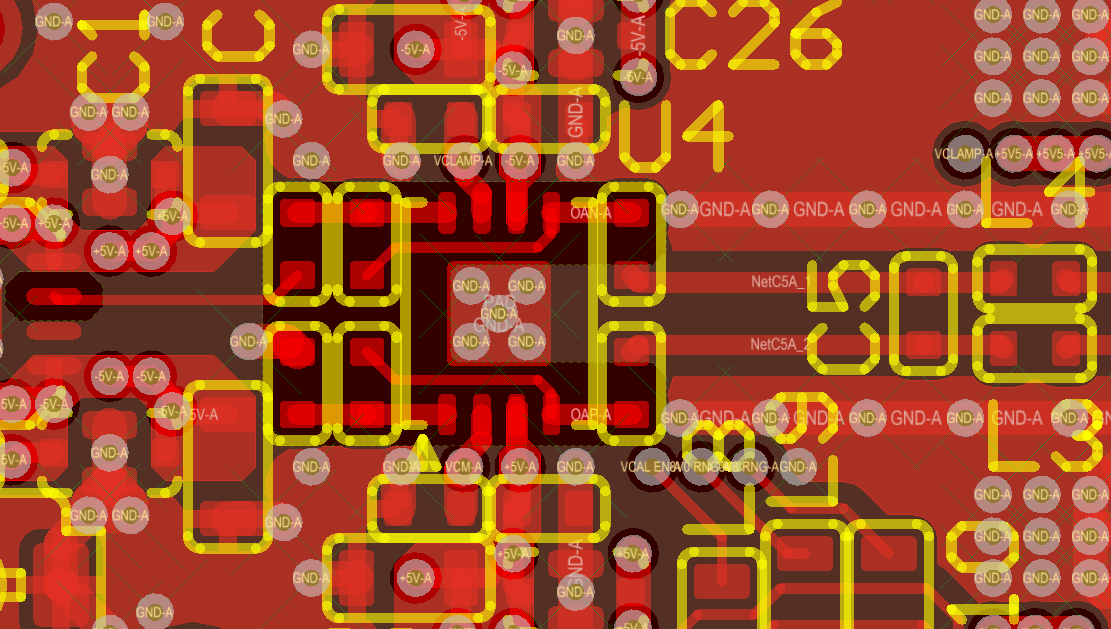

1. What is the layer structure for this board? I would like to know how far the ground plane on layer 3 is below the feedback tracks on layer 2.

2. In the LMH6553SDEVAL SNOA528A document, Layout Considerations, Item 7. Remove the ground and power planes from under and around the part, especially the input and output

pins. But on the layout there is ground plane on layer 3 under the input and output pins, so which recommendation should be followed?

3. Why has the ground plane been removed around the VCM and VCLAMP pins? Are these not normally DC levels?

I'm asking these questions because we are seeing some loss of bandwidth on our LMH6553 layout, so any help would be appreciated.

Thanks, Ken