Other Parts Discussed in Thread: TIDA-00499, , ADC3441, TINA-TI, INA149, TIDA-00049

Hi,

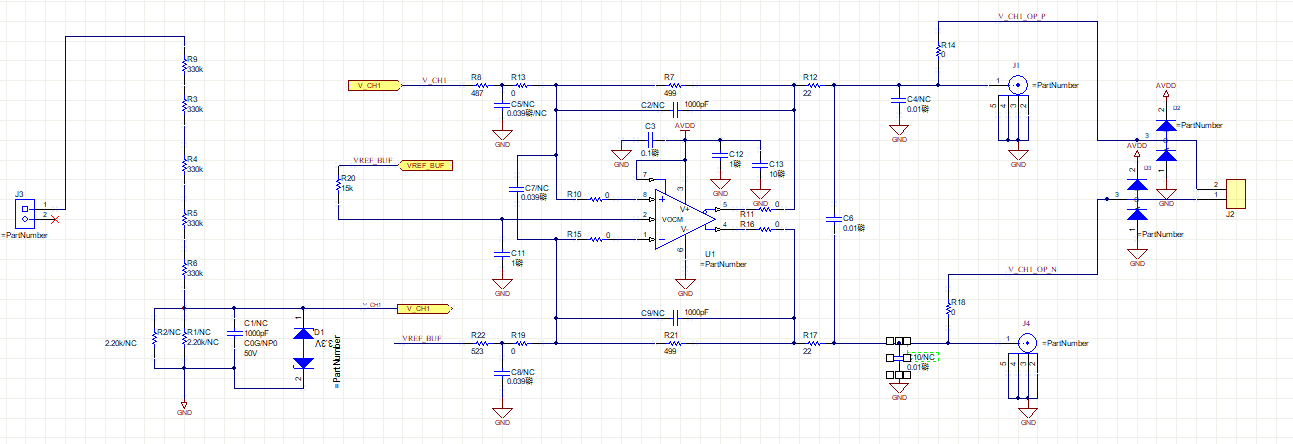

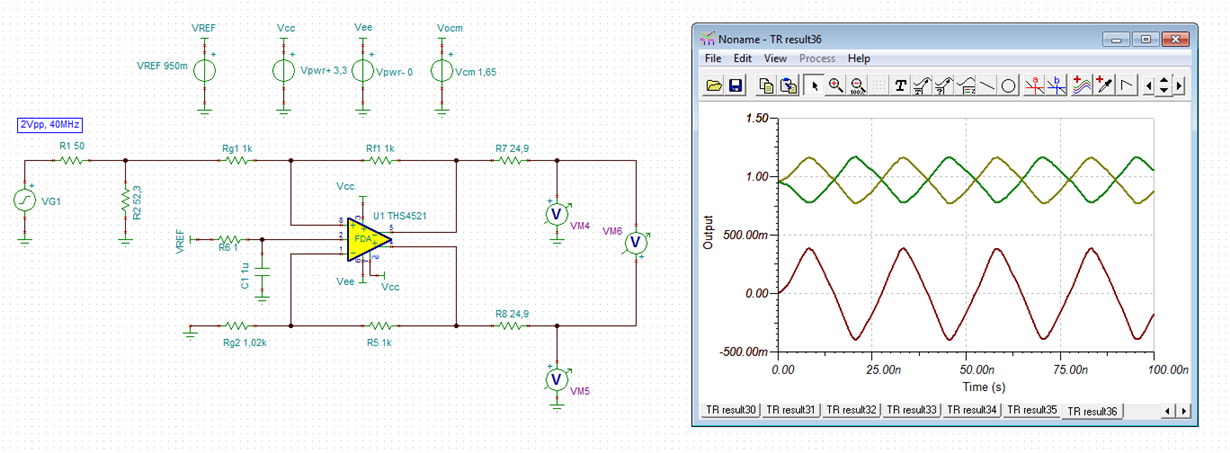

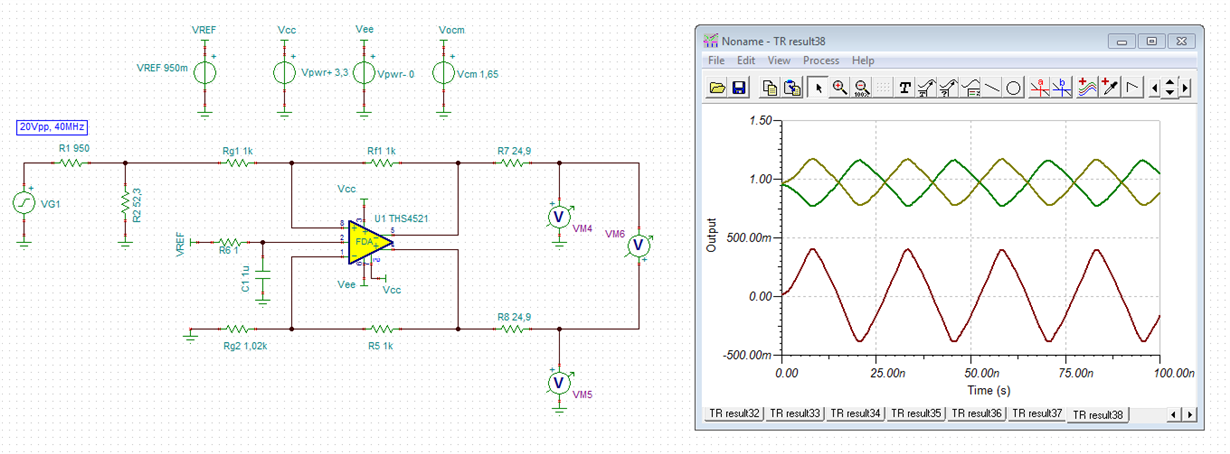

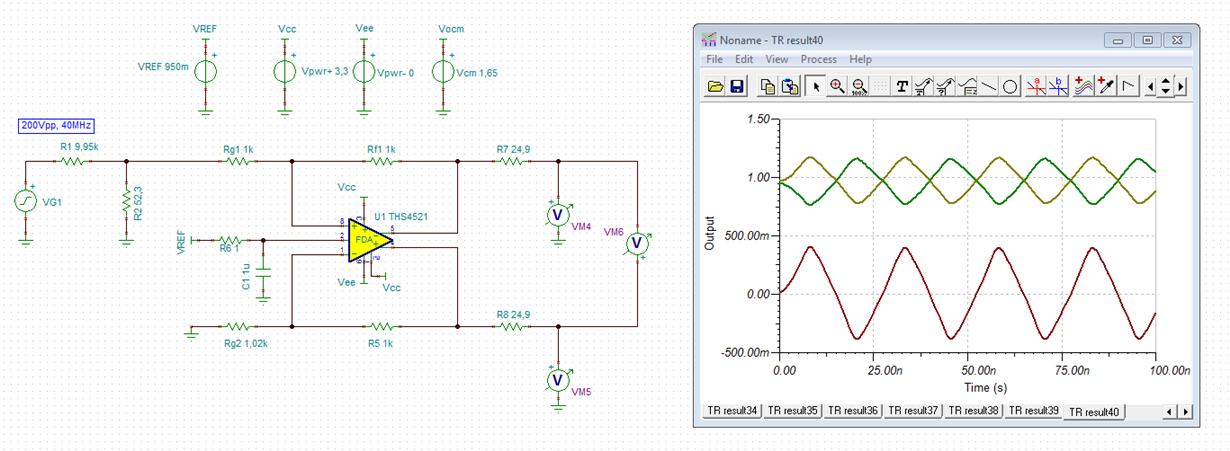

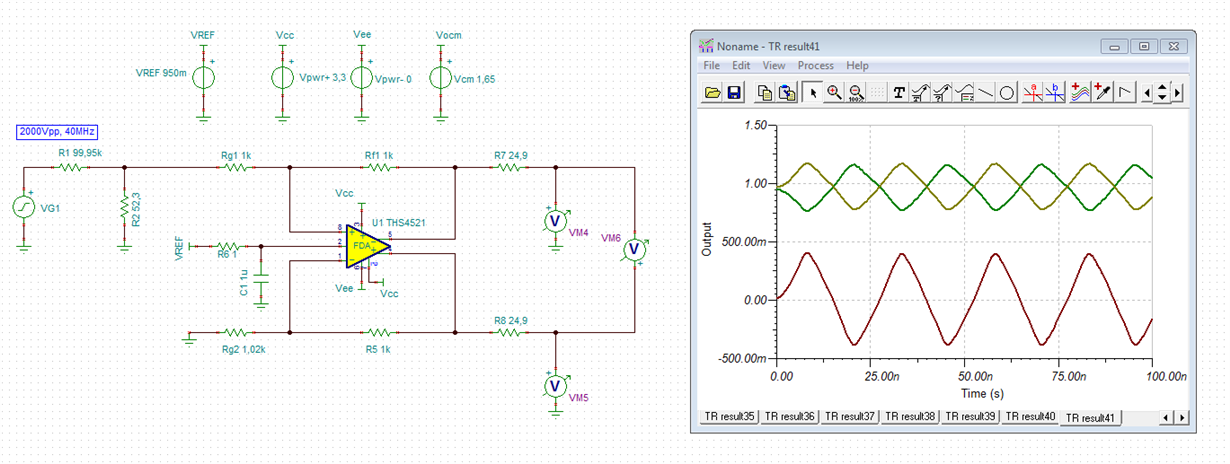

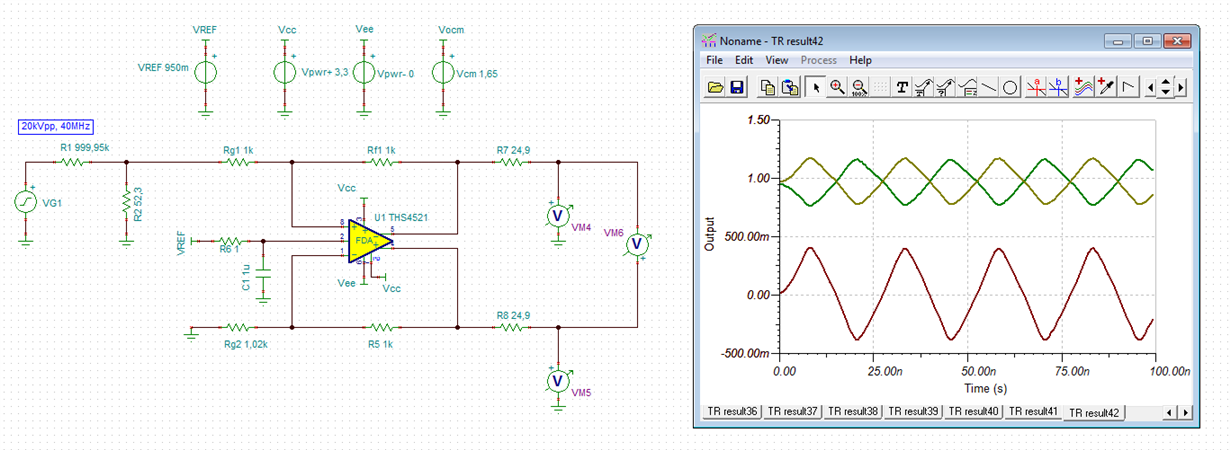

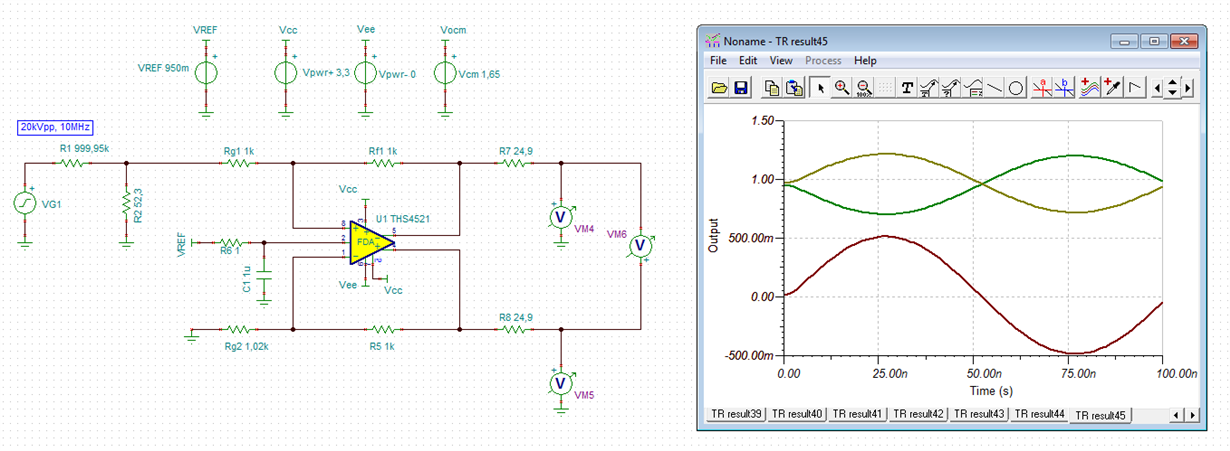

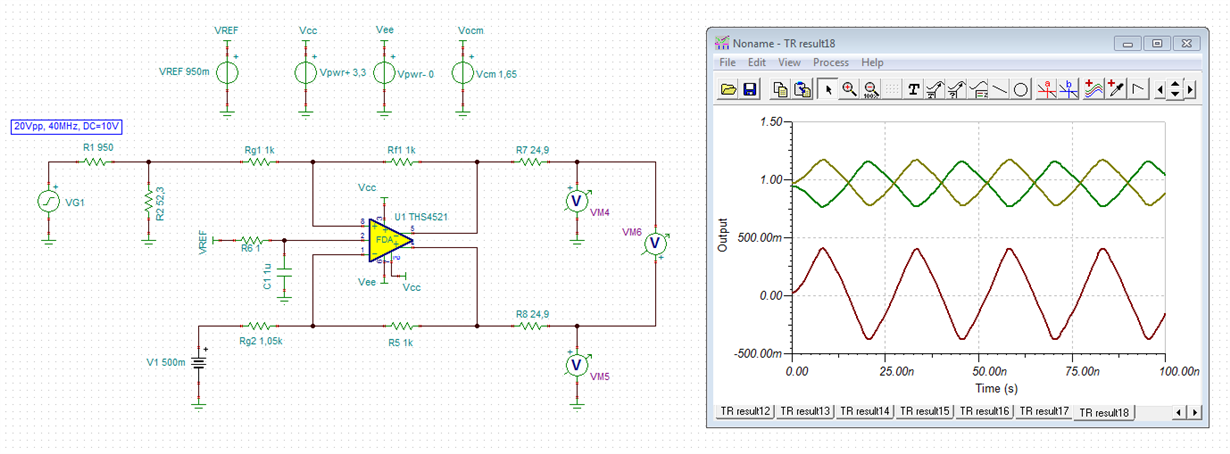

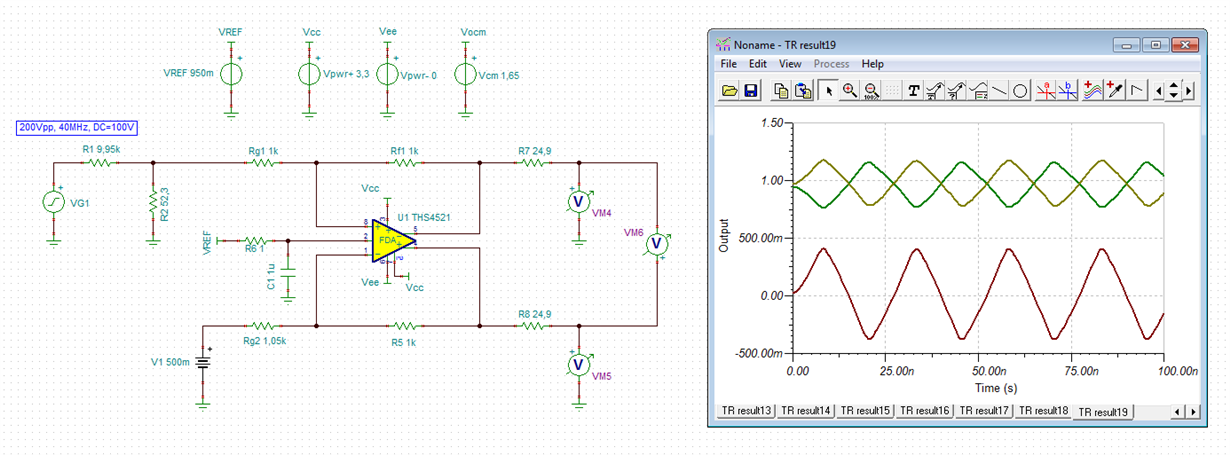

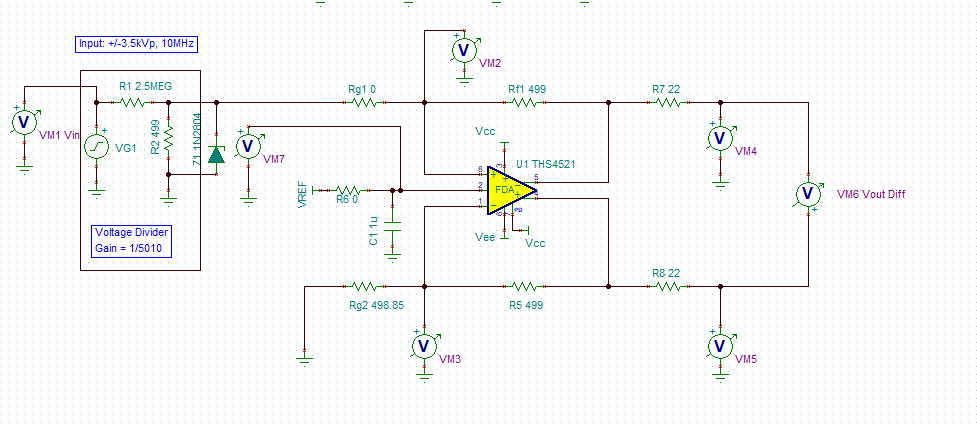

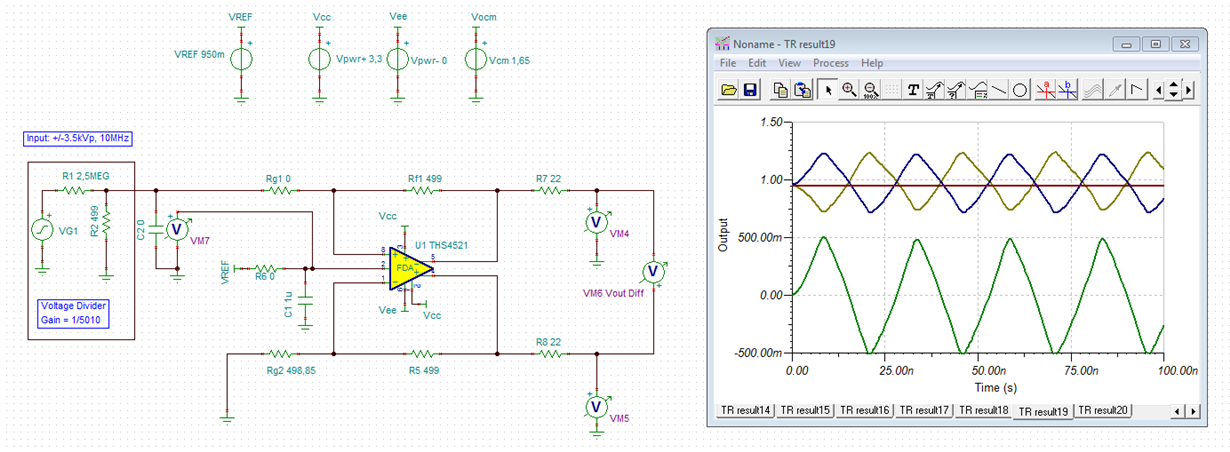

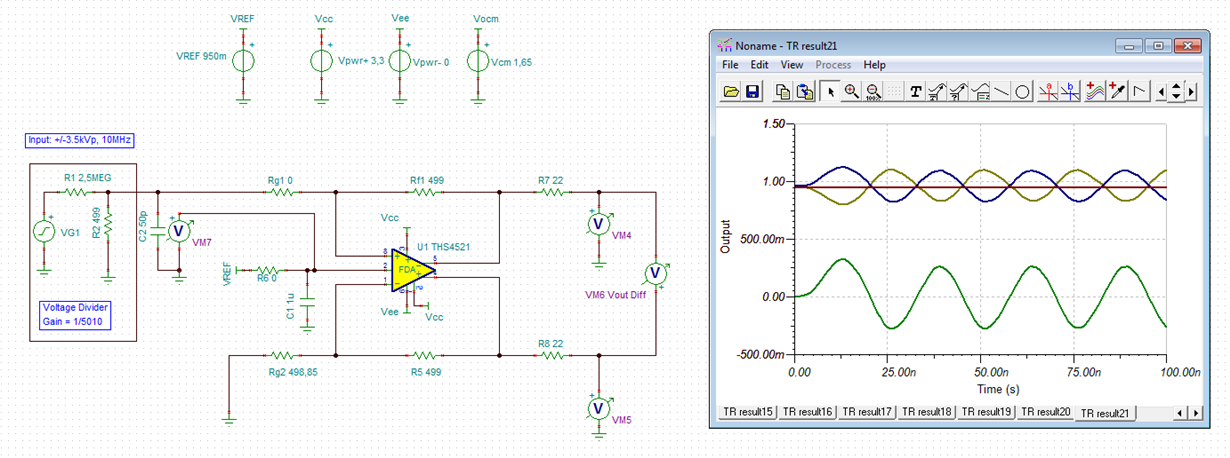

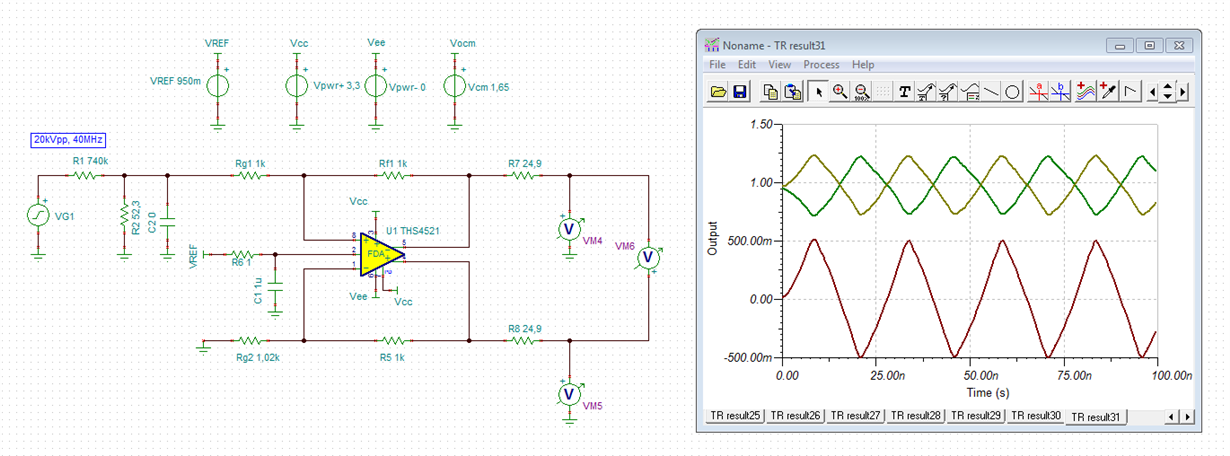

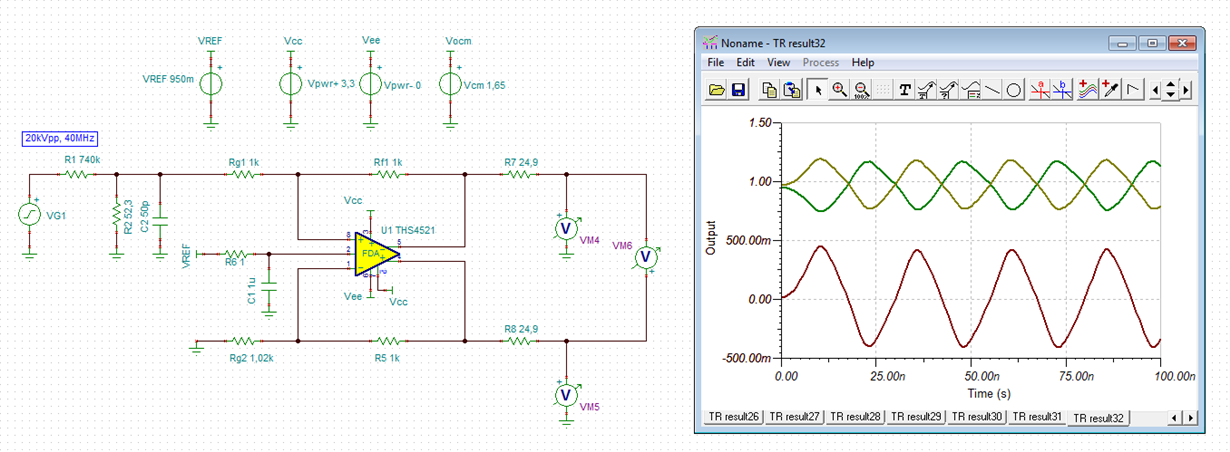

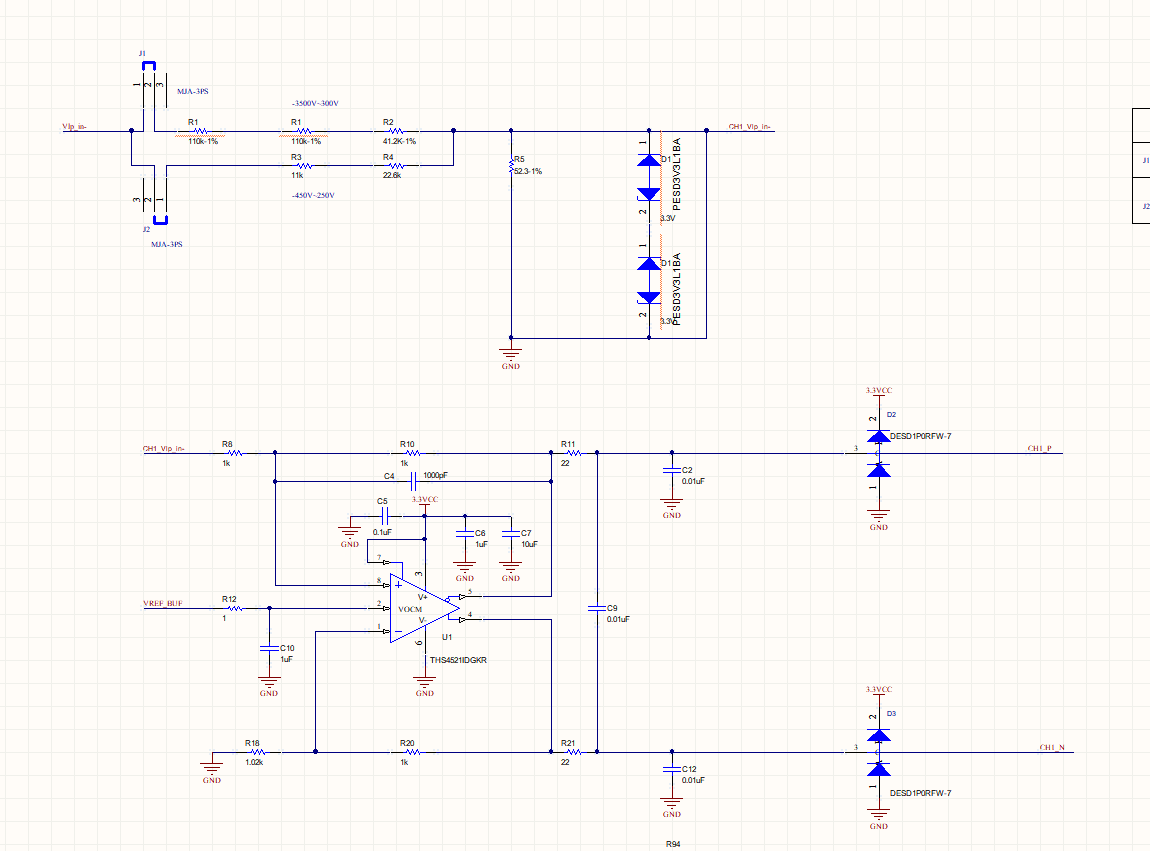

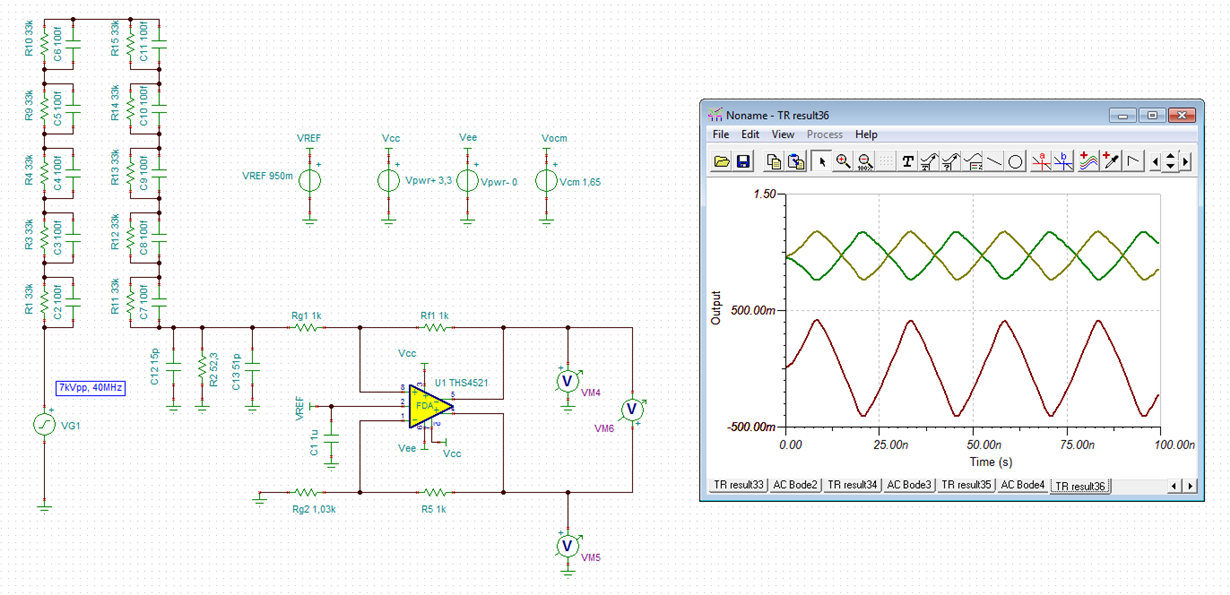

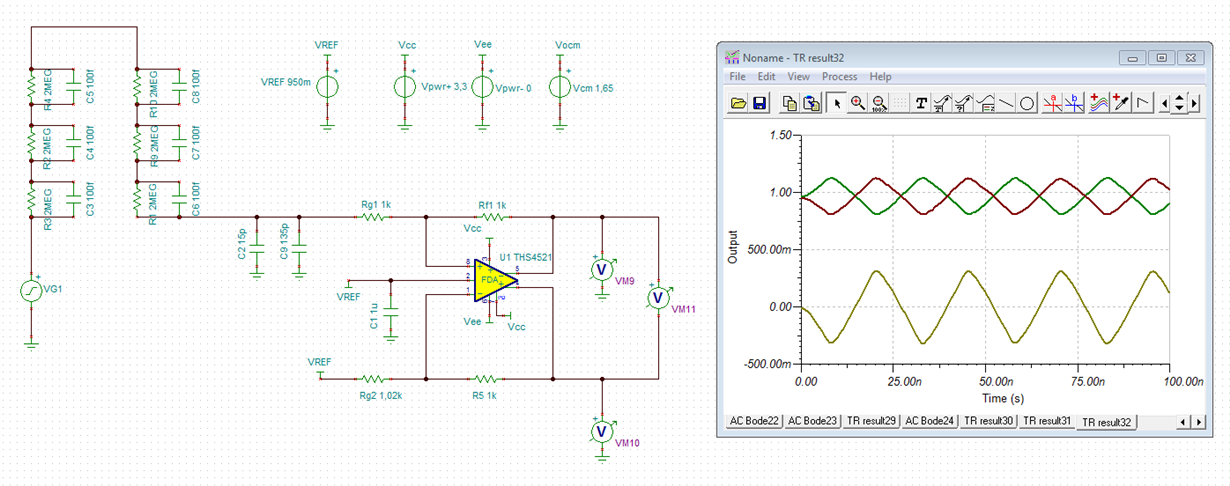

Please help to analysis the attached circuit which is the same with TIDA-00499, but when simulate with TINA, we could find that the output waveform is not smooth, and there is some jitter. In addition, what is the usage of the input Zener diode ?

Thank you very much.

ths4521_TIna_NO cap NO gnd Vlp_in+ 70V (1).TSC

Best regards

Kailyn