Other Parts Discussed in Thread: TINA-TI, OPA365

Tool/software: TINA-TI or Spice Models

Dear all,

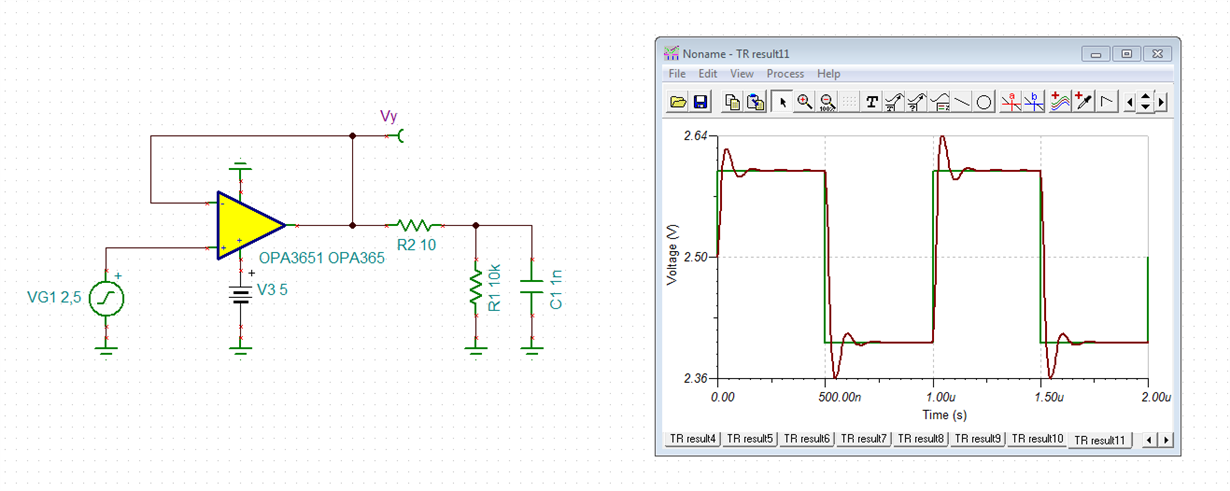

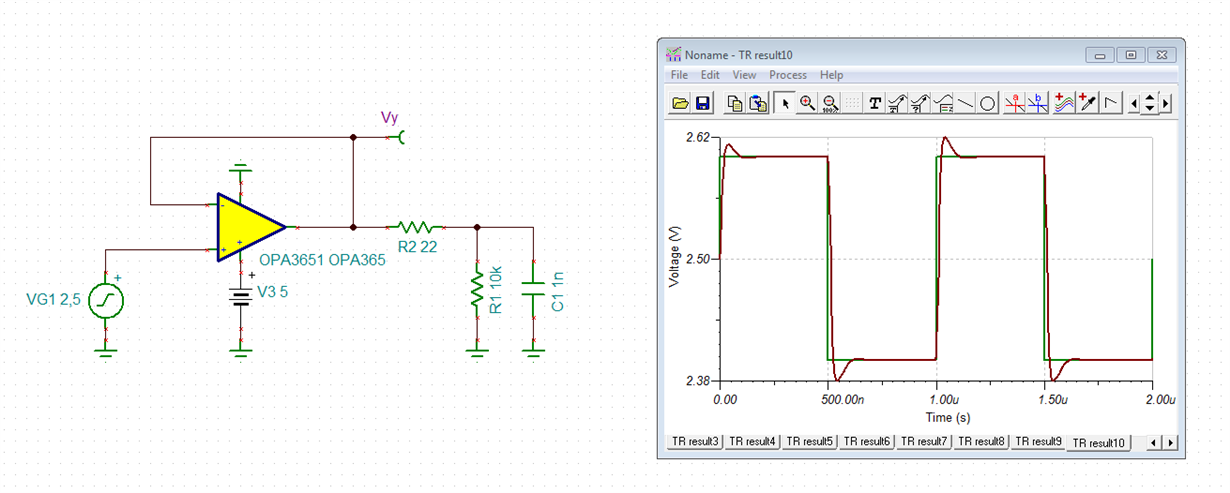

I simulated OPA365's phase margin with driving capacitive load (1nF) by TINA-TI.

But the phase margin was not so good. I know that we should have over 45 degree margin.

Please check following file that TINA result and TINA project file.

OPA365Q1 phase margin_result.pdf

OPA365Q1 phase margin project.TSC

Could you teach me how to think about phase margin and how to control phase margin with driving capacitive load?

I referred to '9.1.1 Capacitive Loads' at data sheet, so I added series resistor at output line.

Now, I plan to input signal from hundreds [kHz] to several [MHz].

Best regards,