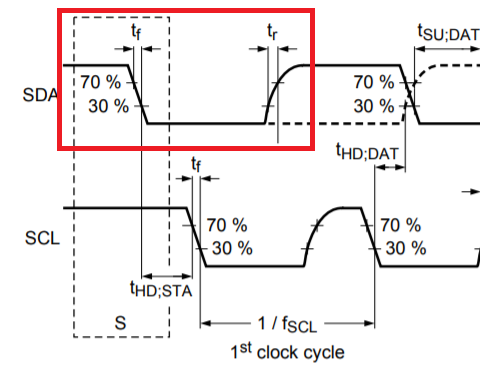

When SCL operating frequency is 400kHz, the Data rise time measured is 540ns, larger than the maximum value of 300ns (given on the datasheet). is there any effect on the I2C bus transmission? and the 540ns is measured from 10% to 90%, is it right?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.