Hello,

Let me confirm about contradiction of input offset current.

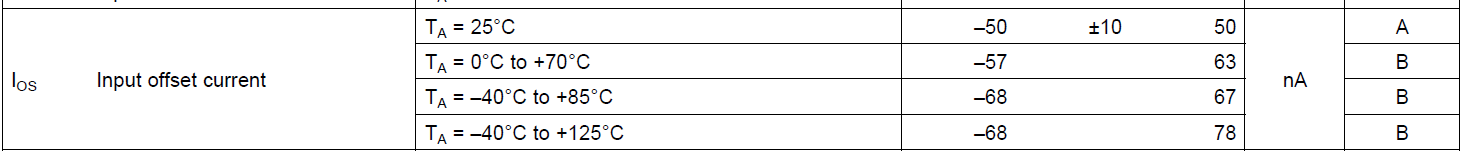

* According to datasheet, there are several spec to understand input offset current at each temperature.

1. I could confirm input offset current drift from "input offset current" spec.

According to datasheet, I could understood as shown below.

Delta input offset current from 25 degree :

28 nA (78nA - 50nA (Source side))

Delta input offset current from 25 degree :

18 nA (68nA - 50nA (Sink side))

2. I could confirm input offset current drift from "input offset current drift" spec.

According to datasheet, I could understood as shown below.

Delta input offset current from 25 degree :

28 nA (280pA * 100 degree (Source side))

Delta input offset current from 25 degree :

28 nA (280pA * 100 degree (Sink side))

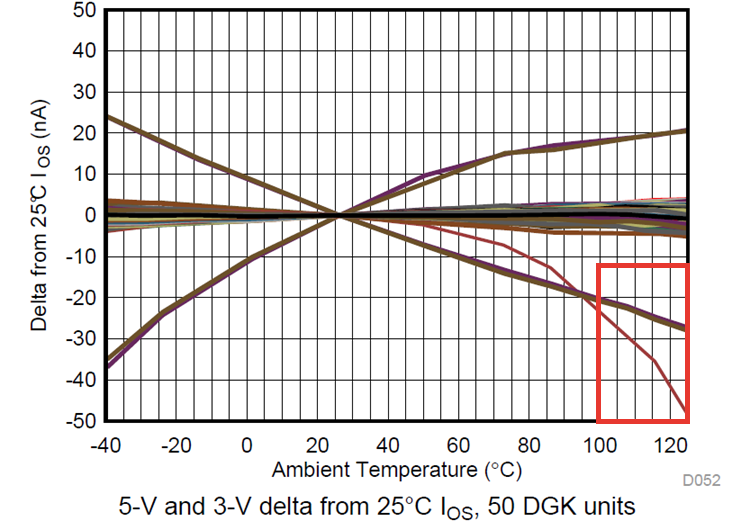

3. Finally, I could confirm input offset current drift from "Figure 52".

According to datasheet, source side of delta input offset current is similar to datasheet other(above "1" and "2".) specs.

However, sink side of input offset current is too much compared with other(above "1" and "2".) specs.

The question is below.

Q. Could you please tell us which input offset current drift value is correct ?

Best Regards,