Hello,

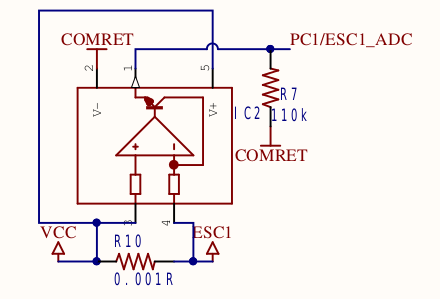

We have a few boards that use two INA169 chips per board. We seem to get different offset errors for each of the chips on the board, but they remain the same across the boards. For exampe, board 1 has chip1 and chip 2. Chip 1 on all the boards seems to have a similar voltage offset at low currents and chip 2 on all the boards seems to have a similar voltage offset at low currents, but the voltage offset of chip 1 and chip 2 is very different. Here is a schematic of what I am using:

From reading other forum posts I was expecting to have a maximum offset of 22mV (0.2mv x 1000uA/V x 110K), but in reality, I am seeing an offset of ~280mV on one of the ICs and ~124mV(and that is consistent across all the boards). We expect max peak current to be about 30A. Do you think we should just add an offset to our software that handles what we are seeing? What do you recommend?

Thanks,

Felipe