Other Parts Discussed in Thread: TIDA-00909, INA282

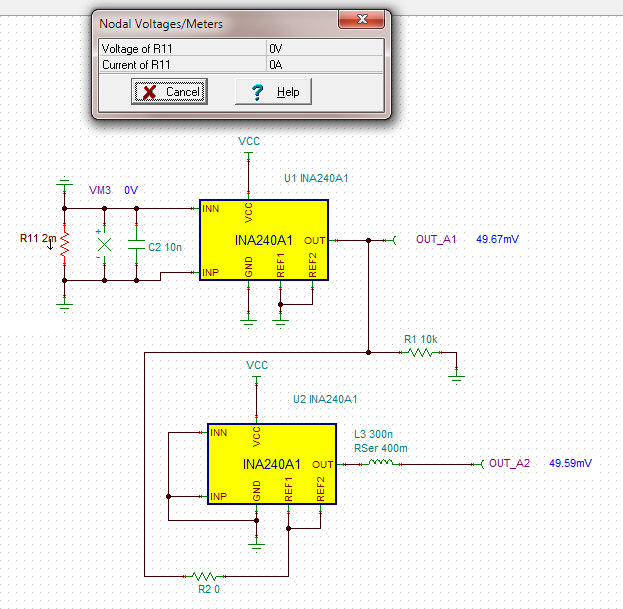

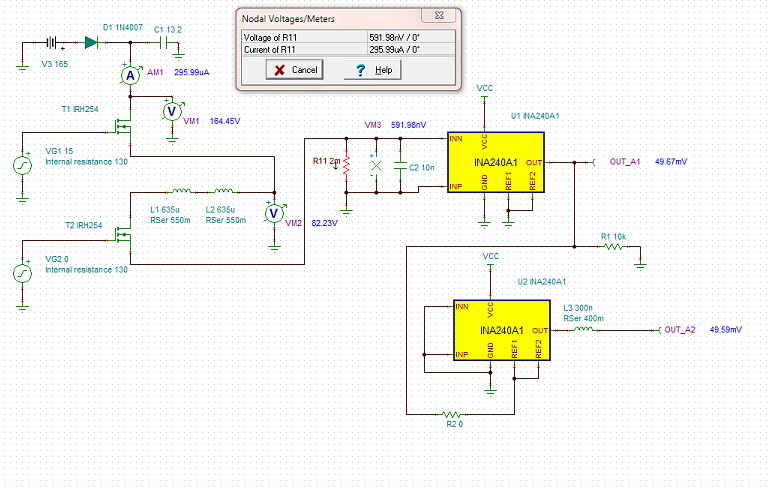

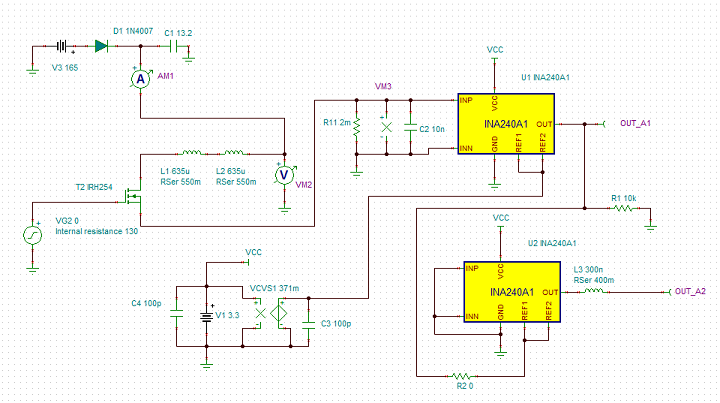

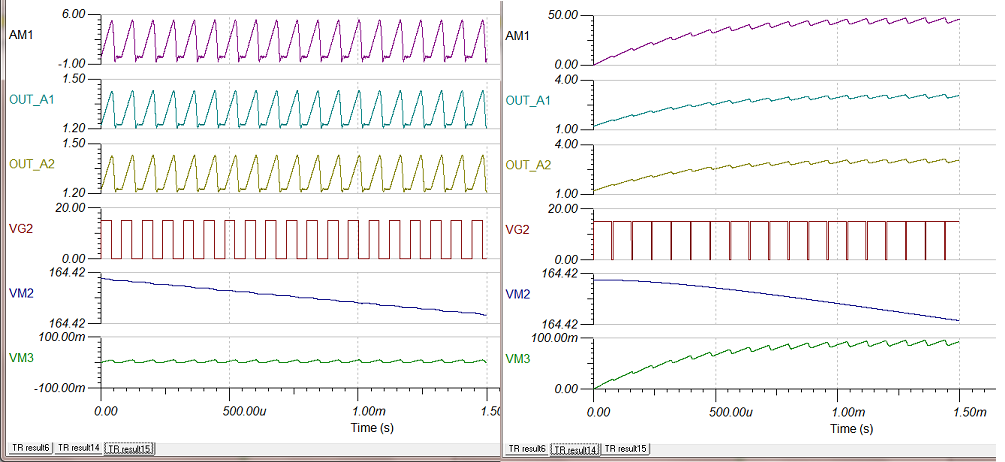

The Spice model DC analysis has 49mV output leakage via INN/INP= 0V. The 240 PCB configuration of the Spice model below has the same output leakage violation for very small microvolt +/-INN bias voltage. A single 240 PCB configuration has even more leakage (120mV) than buffered configuration shown here. Very pleased to see 120mV PSRR reduce to 49mV via addition of follower buffer amp but even 49mV seems excessive. The PCB is very flexible for testing various low side configurations of 240 REF inputs in anticipation of possible issues.

How to reduce the output leakage from the 240 output in both the model and PCB configuration?

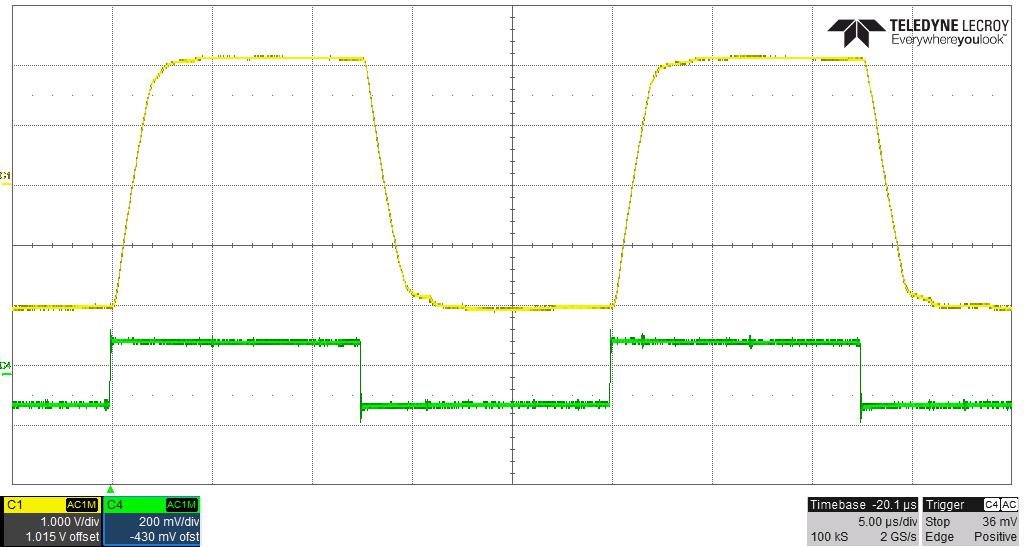

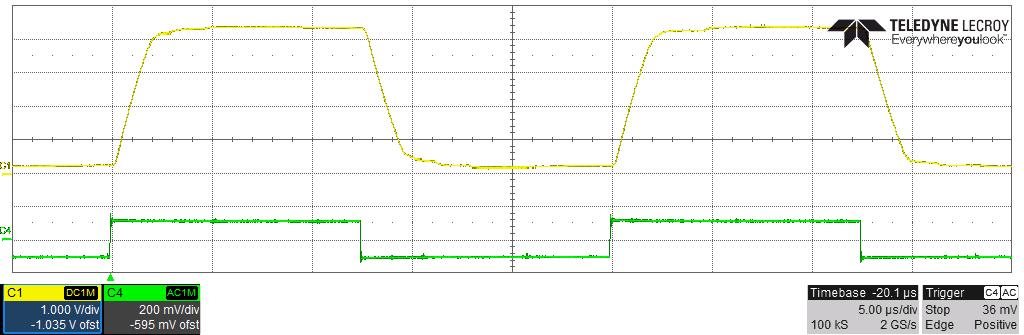

Actual PCB configuration without R1 installed: