Hi guys. I'm trying to make a custom PCB (FR-4 2-layer 1.6T) with OPA552 SOIC package.

https://www.digikey.com/product-detail/en/texas-instruments/OPA552UA-2K5/296-48161-1-ND/8347476

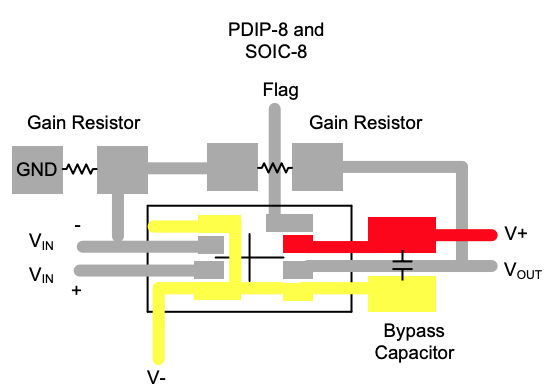

Q0. Is mandatory for connecting all 3 pins (1, 4, 5)? From my application, the OPA552 draws 40mA max and I connect + - 30V to both supply pins.

I just want to connect pin 4 to V- so that I can replace the IC to other SOIC Op Amps later. Unfortunately, not all Op Amps share the same pin like this SOIC type.

So I wish to ask whether it is okay not to connect some negative voltage supply.

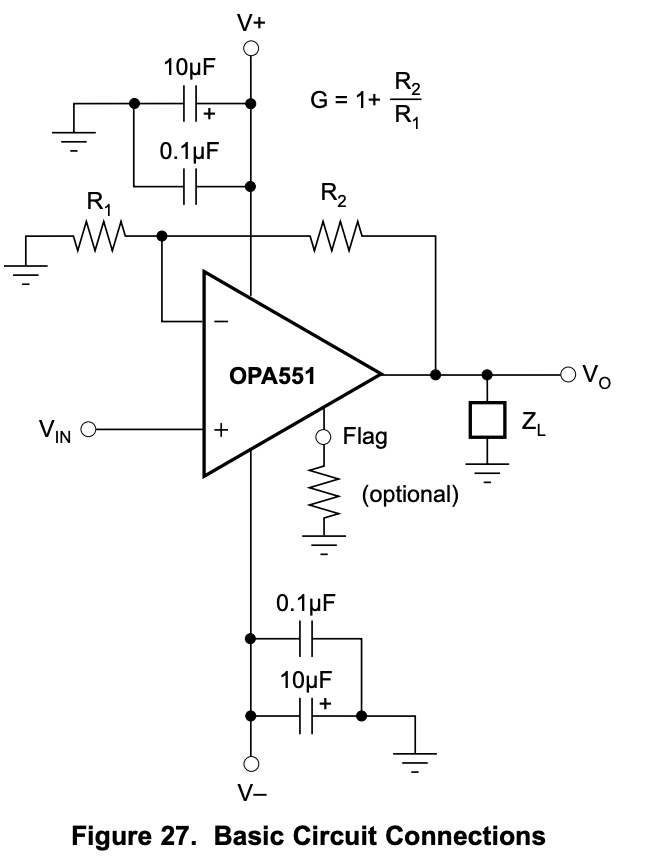

Q1. I tested OPA552P (DIP type) by connecting decoupling capacitors (180nF) to both positive and negative supply pins.

30V positive - GND, -30V negative - GND

Is this "bypass capacitor" connected between the positive/negative supply pins and is this mandatory as well?

Or if I connect the decoupling capacitors respectively, does the "bypass capacitor" becomes unnecessary?

If I need this "bypass capacitor", what should be the proper capacitance value, 180nF?

Q2. If I use the SOIC package, do I have to add total 4 decoupling capacitors (3 to the negative pins, 1 to the positive pin, each 180nF)?