Possible stress to LM124 during test

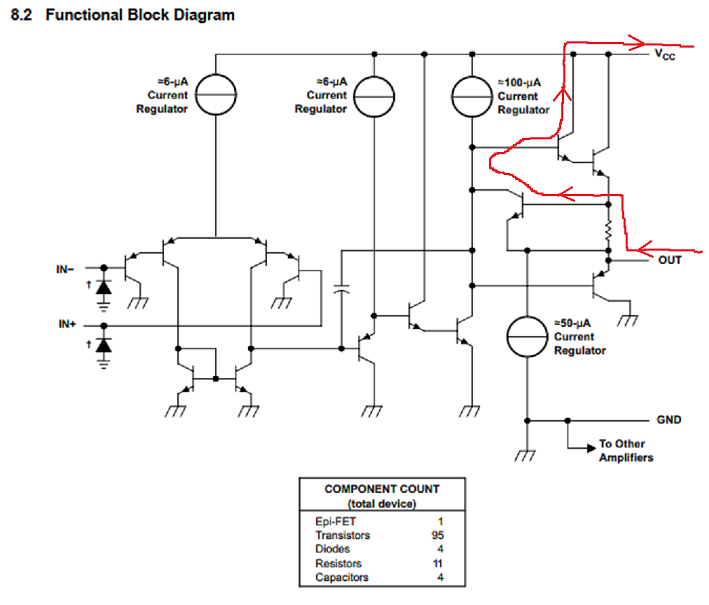

<remove personal information>: Open Provide case details or comments: Dear TI, This question relates to safety of applying current to the output of any one of the four op-amp sections of unpowered LM124 IC’s (TI “Base Part Number” 77043012A) in circuits that are unpowered. In particular, in circuits tested with a Flying Probe machine, outputs of the LM124 sections, one-at-a-time, are subjected to single 5ms pulses of +4.5V, or -4.5V (depending on the circuit configuration) through single resistors of 100 ohms, first with respect to the ground rail, to which the V- power-inputs are attached, and then with respect to the V+ power-input. The V+ power-inputs connect to a 12V (VCC) rail, which is at 0V during these tests since the board is unpowered. A capacitance of 21µF exists between the VCC and ground rails. For the first instant of each test, therefore, the applied pulses appear to be between the output and the V+ power input as well as the output and the V- power input (ground). The absolute-value of the current flowing to the power inputs through the capacitor would drop an unknown amount and at an unknown rate as this capacitance charges, depending on the characteristics of internal path(s) between the output and V+ and V- power-inputs. Presuming that both functional and parasitic components within the chip would conduct current during this test’s 5mS application of a maximum power level of 203mW, at levels limited to 45mA and 4.5V, especially in the hopefully correct presumed absence of a voltage-breakdown situation, it would seem that damage could occur only if dissipation of this power would cause a temperature rise within this 5ms period sufficient to damage the chip, either through die stress that could produce cracking of the die or thermal effects that could alter the characteristics of the components. It seemed reasonable to suspect that the “physics” of the situation might be sufficiently known by the chip designer to enable a confident determination that this dissipation level, for this 5ms application time, would be orders of magnitude below a level at which the potential for damage might begin to be thought possible. If such a declaration of “no stress from these tests” cannot be made, we are faced with the prospect of replacing devices on each of dozens of high-value avionics assemblies. Given the above information, can this test be considered benign, especially if they are performed only one time? We would greatly appreciate your analysis of this situation. Thank you.