Hi,

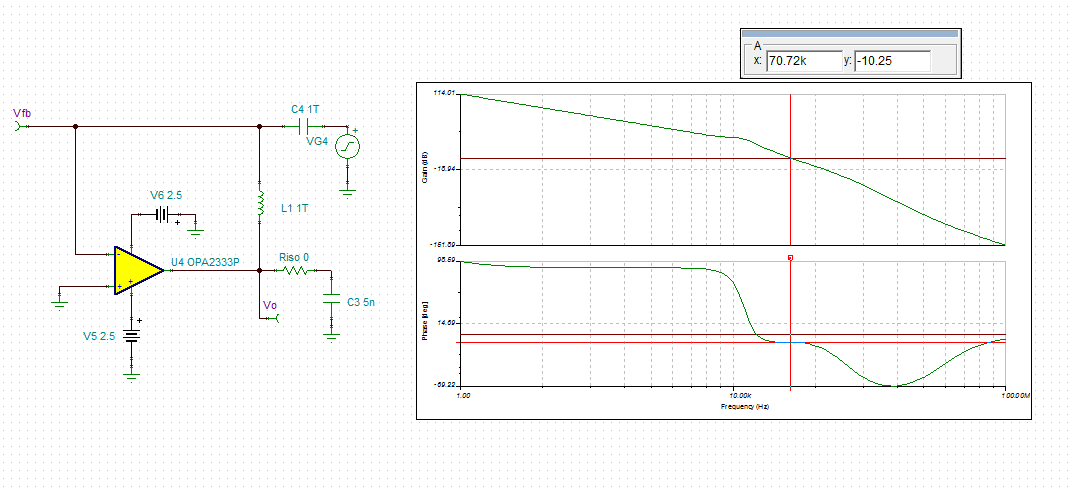

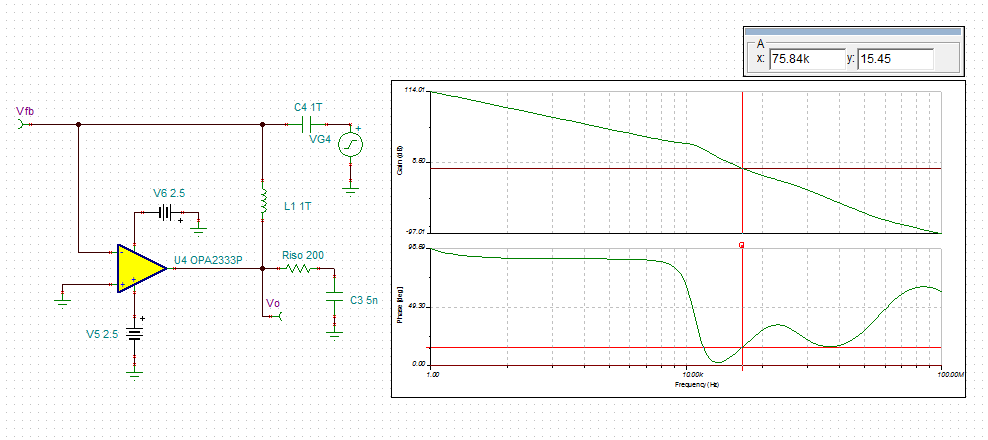

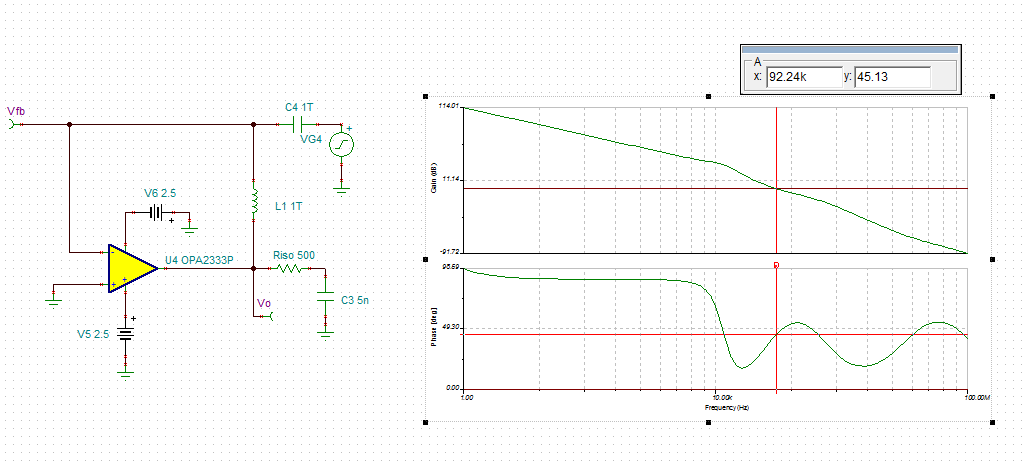

I am trying to simulate buffer stability with tina.

To get a transient graph, I used circuit above and got pretty good result.

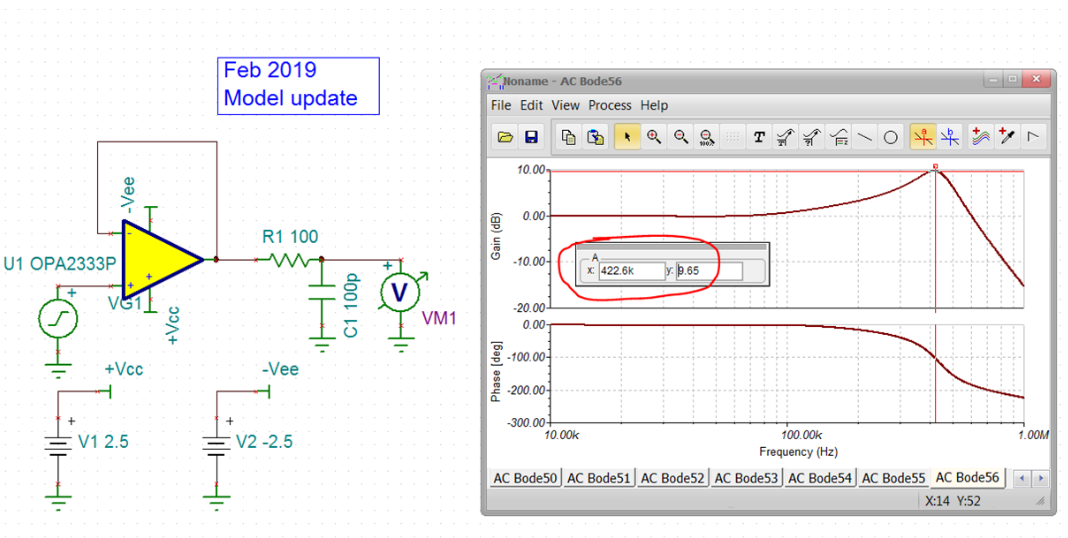

But in TI precision lab, I learned that if i want to simulate gain and phase margin, i have to use open loop circuit like below.

Why do i have to design circuit like above?

If i simulate with first circuit, will i get a wrong result?

Thanks,

Best regards,

Yunsik