Other Parts Discussed in Thread: DAC3283, LMH5401

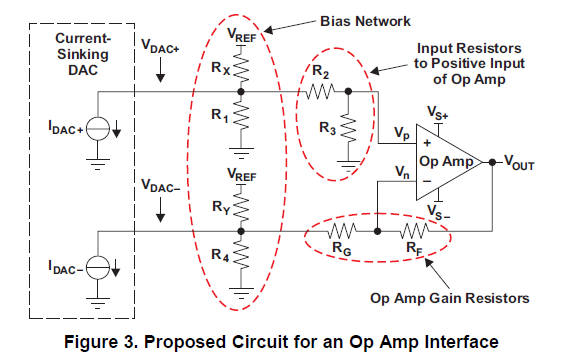

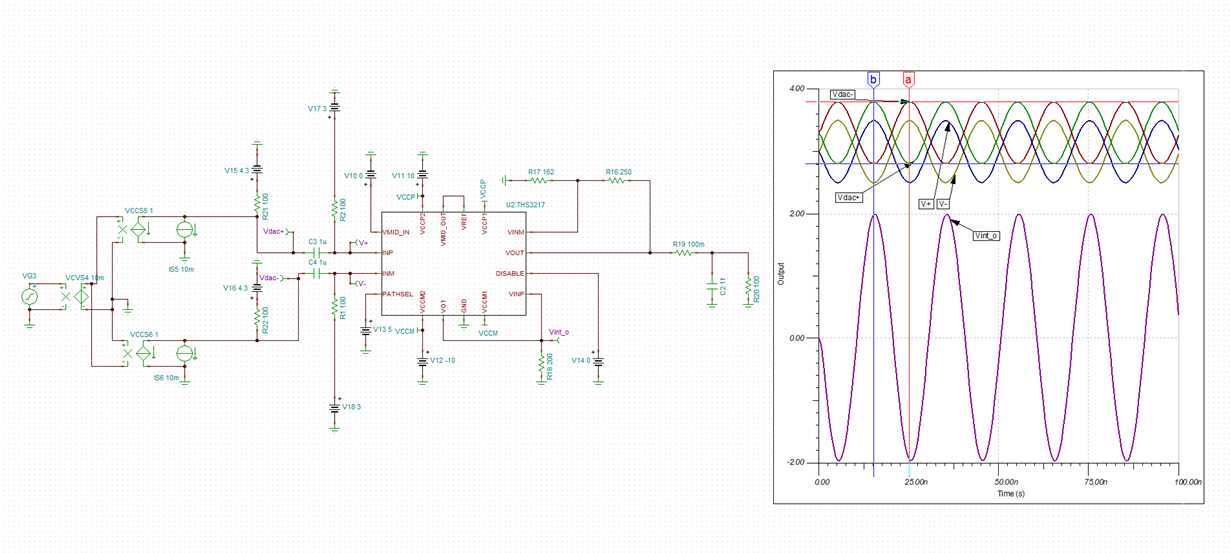

Hi, I am designing the interface circuit for current-sinking DAC3283 using THS3217. I went through the TI's application note and tried to design the circuit based on the topology given in Figure 3.

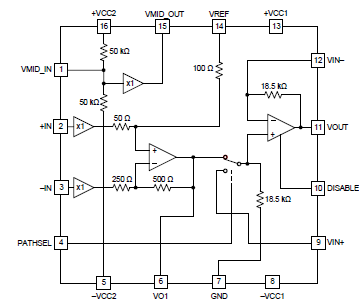

Since THS3217 has an input buffer (shown in x1 at pin 2/3) for each difference input, the input impedance will be quite large therefore the analysis for the circuit in Figure 3 will be invalid for THS3217.

Is this right? If it is true, how should the circuit be designed?

Although the datasheet mentions THS3217 is designed to ease the interface design between current-sinking/sourcing DACs, only design examples for current-sourcing DAC are given.