Hi Team,

Customer is looking for INA233 to sense the power

Would you please review the schematic and provide your comment?

BR,

SHH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Customer is looking for INA233 to sense the power

Would you please review the schematic and provide your comment?

BR,

SHH

Hello SHH,

I see a couple of issues with this schematic:

Best regards,

Ian Williams

Applications Manager

Current Sensing

Hi Ian,

thanks for reply.

Please review to the schematic again provide comment on the questions.

Q1: VBUS (pin 7) should be wired directly to the bus voltage (+19V node), not to the bottom side of the shunt resistor (R740). As it is wired now, there will be errors in the bus voltage and power measurements due to the voltage drop across the shunt.

from d/s page 41 figure 43, VBUS connected to the IN-. so this is not recommended for design. right?

Q2: from d/s figure 25, the RC filter is only on IN+, this is also not for practical design. is that right?

BR,

SHH

Q1: VBUS is shown wired in different ways in the datasheet. The first page diagram and Figure 25 show VBUS connected directly to the supply. Figure 43 and Figure 46 show VBUS connected to IN-. In reality the customer can use either approach, depending on if they want to measure the true bus voltage or the voltage after the shunt. In my experience most customers care about the true bus voltage, which is why I made that recommendation.

Q2: This is an error in Figure 25. There should be resistors on both inputs. You can see that the text for Rfilter is there on IN-, but the resistor symbol is not.

Best regards,

Ian Williams

Hi Ian,

Would you please review and provide comment on the schematic and layout?

schematic and layout file

here is the free layout viewer if not able to open.

https://txn.box.com/s/28086gkhz2ugytcjnpujajjdilv9ojki

BR,

SHH

Hello SHH,

I am able to open the layout with PADS viewer, but the image of the schematic is corrupted and I can't properly analyze it or read the reference designators. Can you please ask the customer to send me the schematic again?

Best regards,

Ian Williams

Hi Ian,

please refer to the pdf format schematic attachment here and provide comment on layout review

txn.box.com/.../g6a0dv07ryzb29d7uevbsxkx2gsso0xm

BR,

SHH

Hi Ian,

Please refer to the latest layout file.

schematic

txn.box.com/.../g6a0dv07ryzb29d7uevbsxkx2gsso0xm

layout

txn.box.com/.../wxudpq3fm7e7sg9r8qqsaq2gi8658c9e

BR,

SHH

Hello SHH,

Thank you very much for providing the updated files. I was able to review them with no issues. The schematic looks good - no issues there.

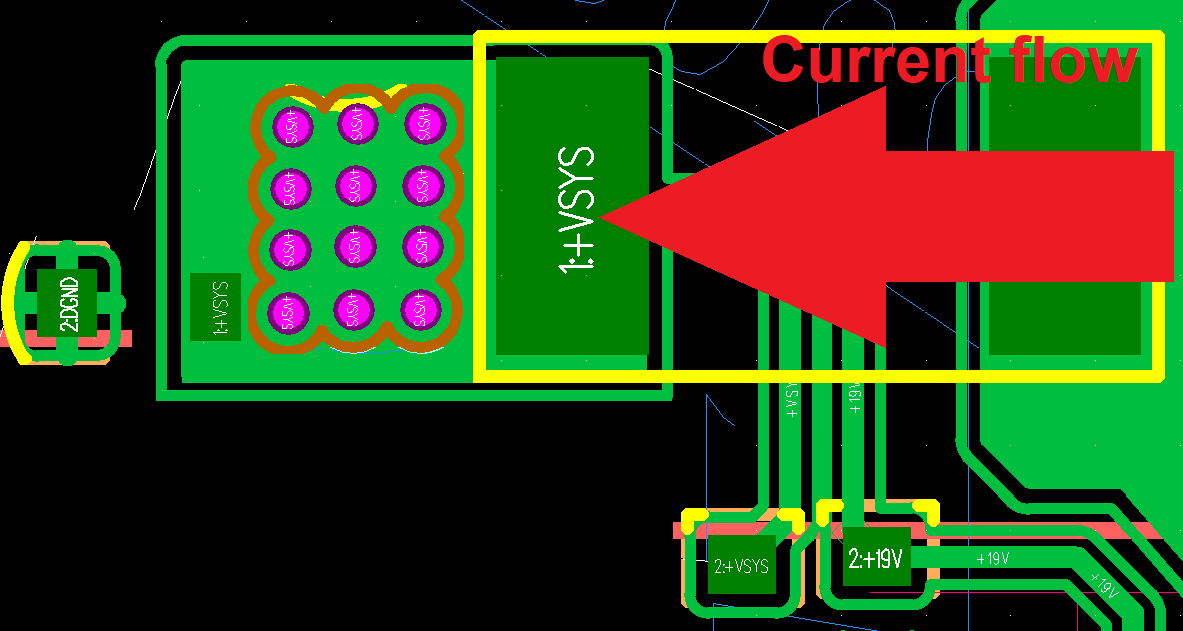

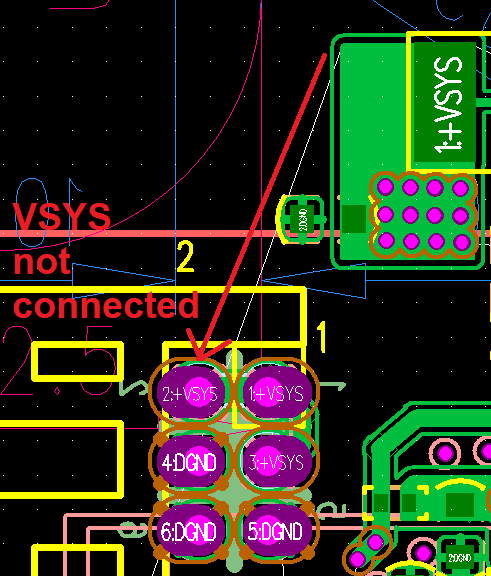

I also don't see any major issues with the layout, however I do have some comments and questions:

Best regards,

Ian Williams