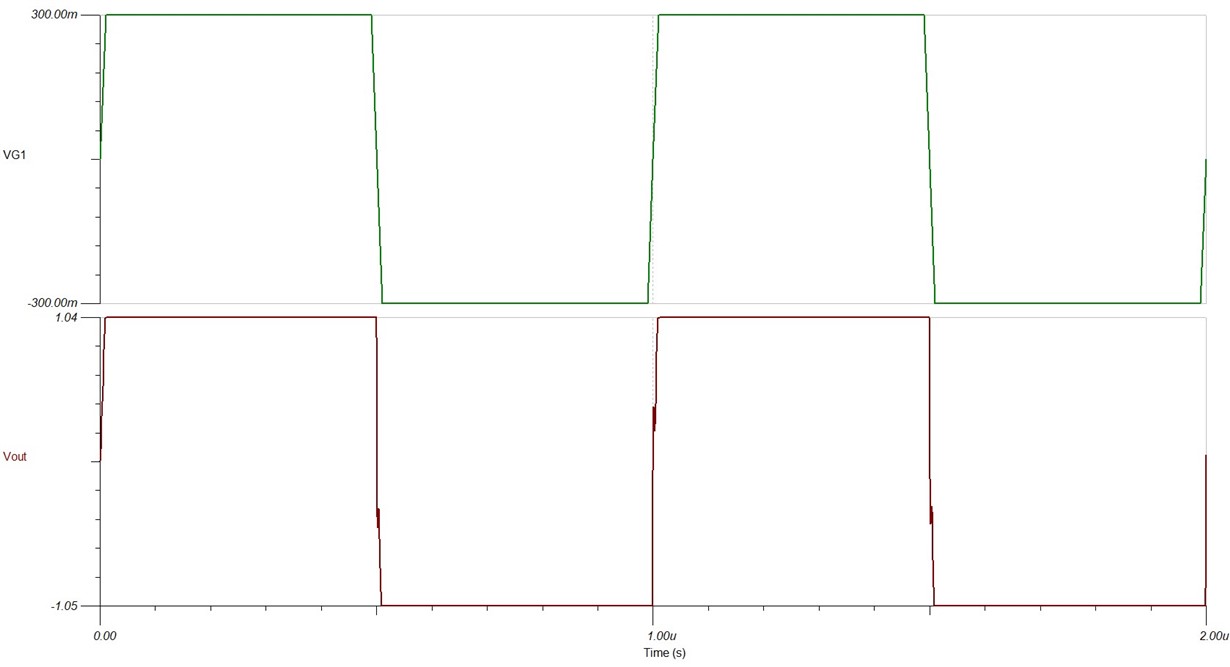

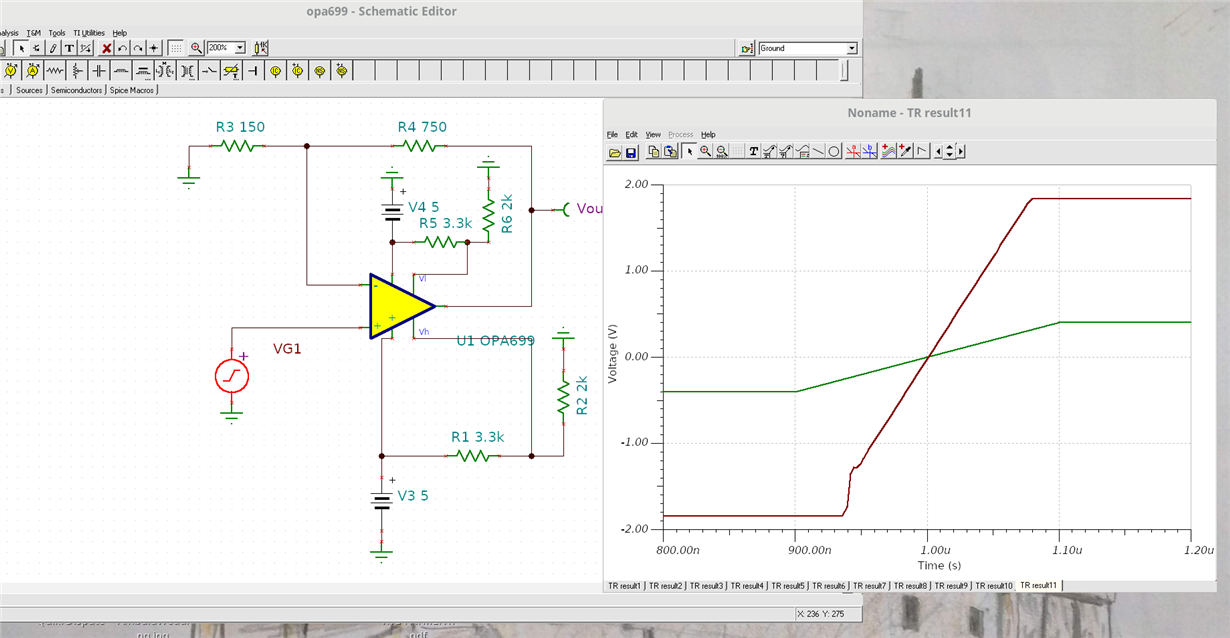

Greetings TI engineers! I am using an OPA699 for a sweep circuit and am witnessing some unexpected distortion. Here are the facts:

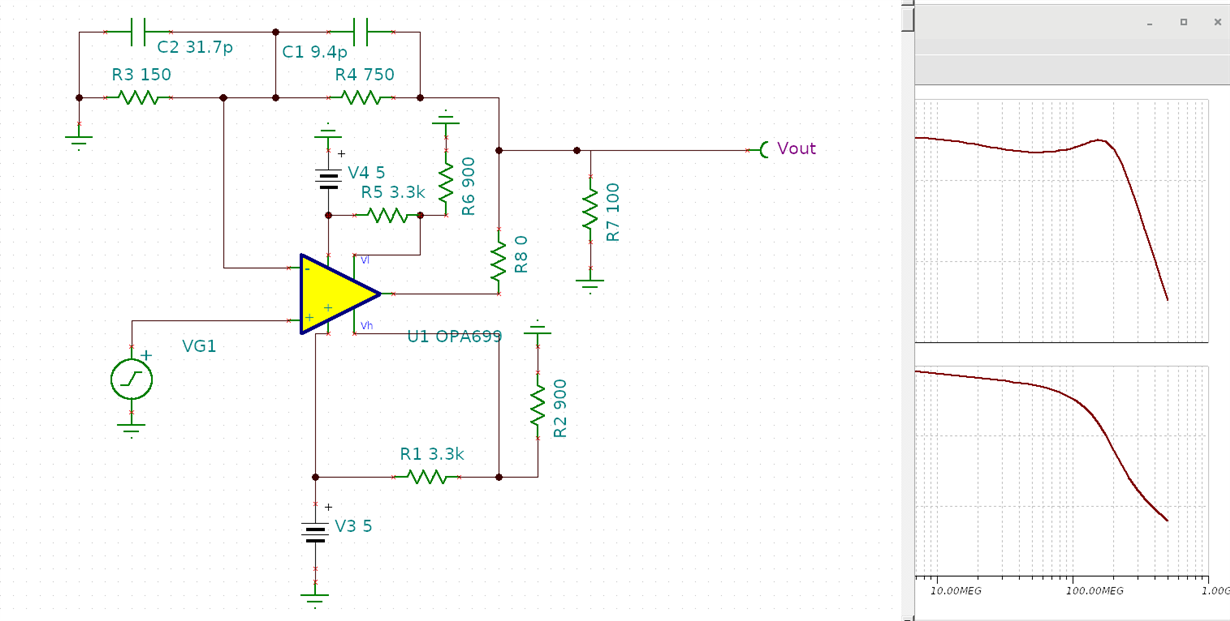

1. Dual supply = +/- 5V. G = +6 with Rf = 750 ohms. No capacitors. Opamp and limit pins bypassed with 0.1uF

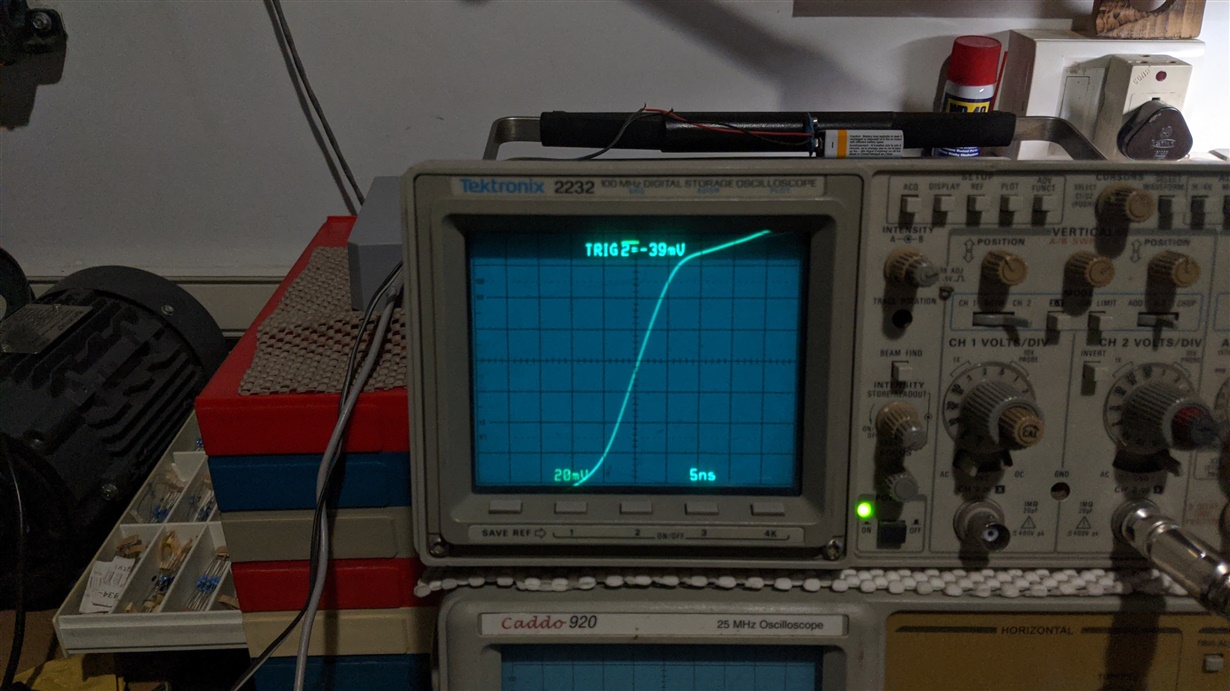

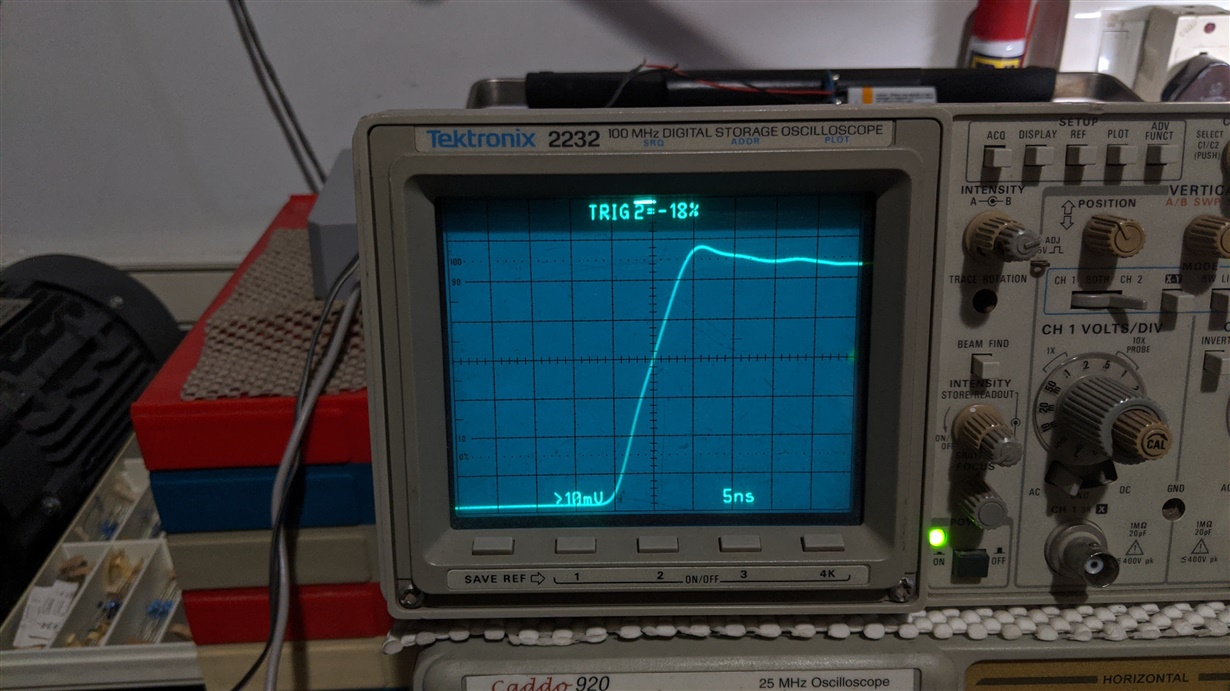

2. Noninverting input fed by another opamp generating a -0.3V -> +0.3V ramp at 50V/uS, overall signal peaks lie at at almost +/- 0.6V.

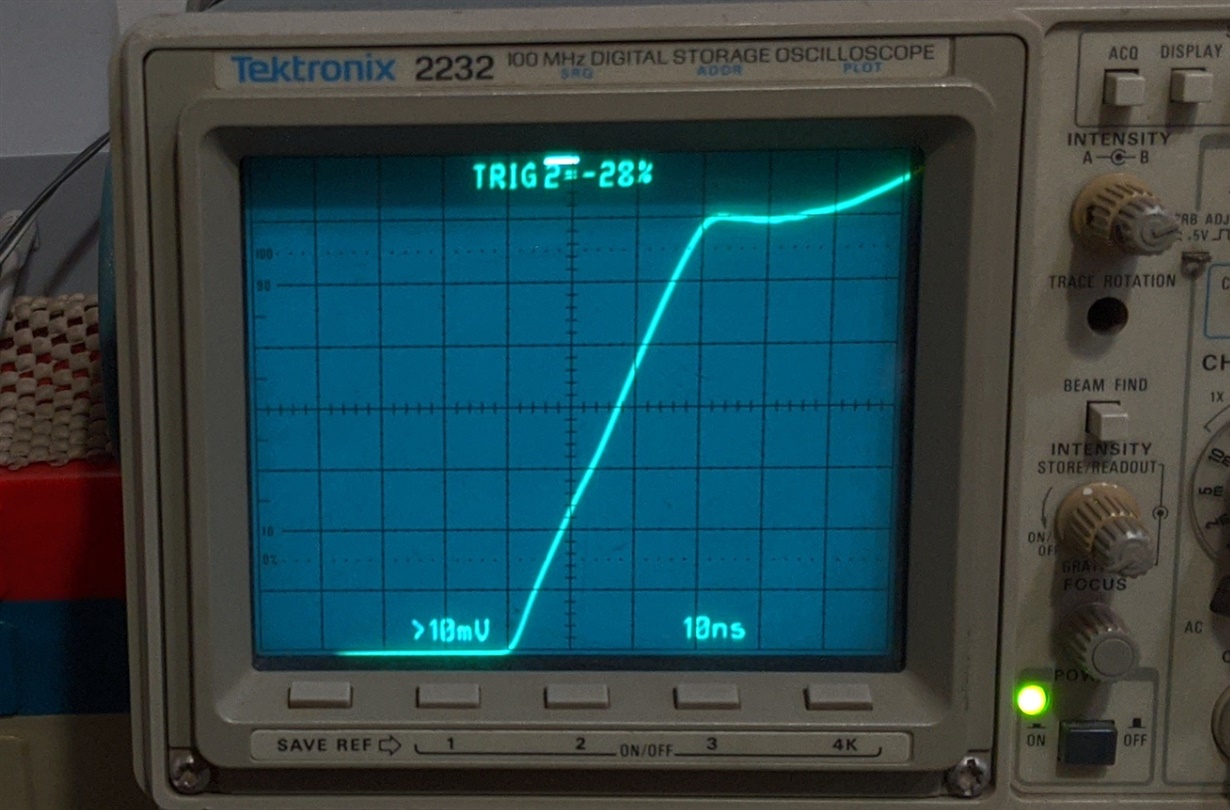

3. With limit pins open, I get a straight looking ramp on the output as expected. However, with limits set to +/- 2V (or less), I get a noticeably distorted ramp. Not "severe" but "noticeable".

I'm puzzled as It does not seem that I am pushing the amp with too fast an input ramp. Any suggestions? Could it be that the amplified signal peak (G=+6X0.6V = 3.6V) lying beyond the input voltage range of 3.2V causes the problem?

Thanks in advance.

Best - Ram