Hello,

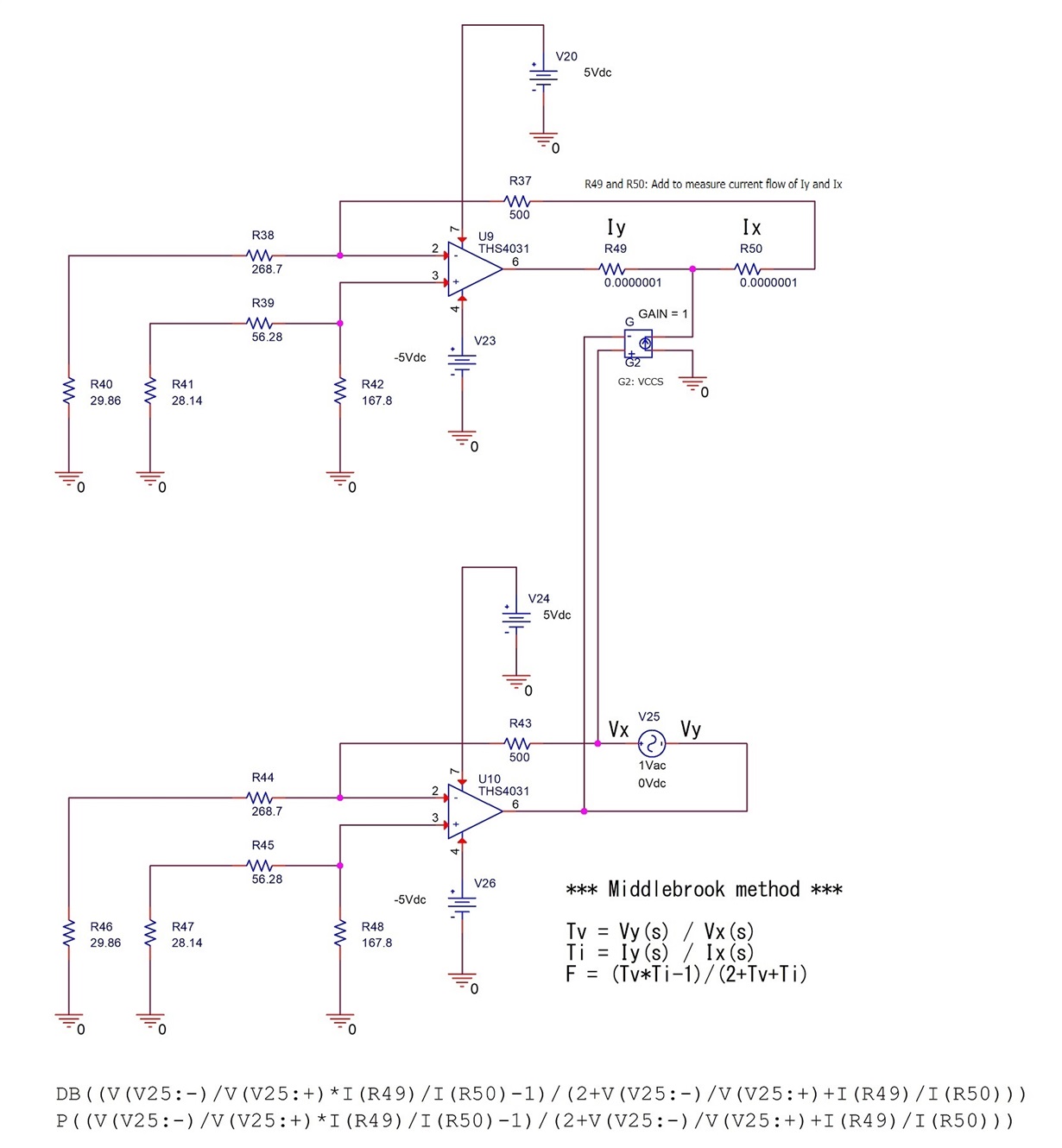

I executed PSpice circuit simulation to analyze stability for amplifier circuit used THS4031.

The circuit is same circuit as figure 6 of application report SBAA135A.

(Schematic for circuit simulation is shown below)

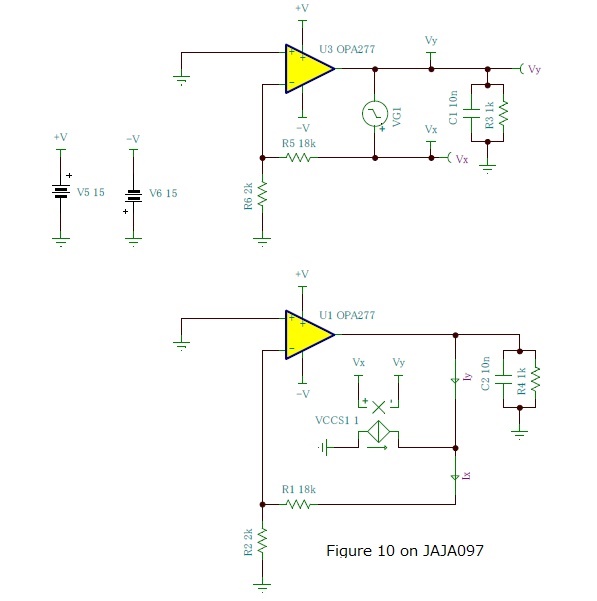

And stability analysis method is middlebrook method based on figure 10 (figure on page 9) and figure 12

(equation Tv, Ti, F on page 10 lower figure) on reference material JAJA097.

JAJA097 is reference material published by Texas Instruments Japan.

Title of JAJA097 is Study of negative feedback circuit stability used circuit simulator TINA.

My simulation result of gain margin and phase margin are below.

Gain margin: -11dB

Phase margin: 74deg

Q: Please comfirm simulation method (simulation circuit) and results are correct or not.

Regards,

MESH